Leishmania (Leishmania) amazonensis altera los parámetros ...

:インテル プログラマブル・デバイス・ パッケー … › content › dam ›...

Transcript of :インテル プログラマブル・デバイス・ パッケー … › content › dam ›...

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

更新情報フィードバック

AN-114 | 2018.10.09

最新版をウェブからダウンロード: PDF | HTML

目次

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン.........................31.1. BGA パッケージの概要...............................................................................................31.2. PCB レイアウト用語...................................................................................................4

1.2.1. エスケープ・ルーティング................................................................................. 41.2.2. マルチレイヤー PCB...................................................................................... 41.2.3. ビア..........................................................................................................41.2.4. ビア・キャプチャ・パッド....................................................................................51.2.5. 表面ランドパッド.......................................................................................... 61.2.6. ストリンガー................................................................................................7

1.3. 高集積 BGA パッケージの PCB レイアウト........................................................................ 71.3.1. 表面ランドパッドの寸法.................................................................................. 71.3.2. ビア・キャプチャ・パッドのレイアウトと寸法........................................................... 111.3.3. 信号ラインのスペースおよびトレース幅...............................................................181.3.4. PCB レイヤー数..........................................................................................20

1.4. AN 114 : インテル・プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインの文書改訂履歴 .......................................................................................................... 31

目次

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

2

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

プログラマブル・ロジック・デバイス (PLD) の集積度と I/O ピン数の増加に伴って、小型パッケージと多様なパッケージオプションの需要が増え続けています。ボールグリッド・アレイ (BGA) パッケージは、I/O 接続部分がデバイス内部にあり、ピン数とボード面積の比率が向上するため、理想的なソリューションです。標準 BGA パッケージは、接続部分を 2 個から 8 個多く含むクワッド・フラット・パック (QFP)パッケージです。さらに、BGA はんだボールは QFP リードよりも強度がかなり高いため、手荒な取り扱いにも耐えうる堅牢なパッケージになっています。

このアプリケーション・ノートで提供している推奨 PCB デザイン・ガイドラインの対象は、インテル・プログラマブル・デバイス用のより複雑なパッケージオプションの一部ですが、 インテル® Stratix® 10 デバイスとそれ以降は除きます。

注意: インテル Stratix 10 デバイスパッケージ以降に関する詳細については、それぞれ個別のManufacturing Advantage Services (MAS) Guidelines文書を参照してください。

Enpirion の電源ソリューション製品については、PCB ガイドラインおよび GERBER ファイルが各デバイスにあり、各 Enpirion データシートに記載されている情報と共に使用できます。

関連情報• Package Information (dimensions, materials, etc.) and Thermal Resistance

• Manufacturing with Intel® Field Programmable Gate Array Platform Code NamedIntel Stratix 10

1.1. BGA パッケージの概要

BGA パッケージでは、I/O の接続部分はデバイス内部に配置されています。通常、リード線はパッケージの周囲に沿って配置されていますが、基板の底部にマトリックス状に配置されているはんだボールと置き換えられます。最終デバイスのはんだ付けは直接 PCB にされ、使用する組み立て工程は、システム設計者推奨の標準表面実装技術と実質的に同一のものです。

AN-114 | 2018.10.09

フィードバック

Intel Corporation.無断での引用、転載を禁じます。Intel、インテル、Intel ロゴ、Altera、ARRIA、CYCLONE、ENPIRION、MAX、NIOS、QUARTUS および STRATIX の名称およびロゴは、アメリカ合衆国および/ またはその他の国における Intel Corporationの商標です。インテルは FPGA 製品および半導体製品の性能がインテルの標準保証に準拠することを保証しますが、インテル製品およびサービスは、予告なく変更される場合があります。インテルが書面にて明示的に同意する場合を除き、インテルはここに記載されたアプリケーション、または、いかなる情報、製品、またはサービスの使用によって生じるいっさいの責任を負いません。インテル製品の顧客は、製品またはサービスを購入する前、および、公開済みの情報を信頼する前には、デバイスの仕様を最新のバージョンにしておくことをお勧めします。*その他の社名、製品名などは、一般に各社の表示、商標または登録商標です。

ISO9001:2015登録済

さらに、BGA パッケージには次の利点もあります。

• リード損傷の危険性が低い - BGA パッケージのリードは頑丈なはんだボールで構成されており、取り扱いによってリードが損傷を受ける危険性が低くなっています。

• 単位面積あたりのリード数が多い - リード数を増やすため、 はんだボールをパッケージの端に近づけ、ピッチを次のように小さくします。

— フリップチップおよびワイヤーボンド BGA の場合は 1.0 mm

— ワイヤーボンドおよびウェハー・レベル・チップ・スケール・パッケージ (WLCSP、または別名VBGA) ファインピッチ BGA の場合は 0.8 mm、0.5 mm、および 0.4 mm。

• 低価格な表面実装機器が使用可能 - BGA パッケージでは、実装中の配置が多少不完全でも許容できるため、低価格の表面実装機器を使用することができます。BGA パッケージで配置が不完全になるのは、リフロー中のはんだのセルフ・アラインメントによるものです。

• 実装面積が小さい - 通常、BGA パッケージは QFP パッケージよりも 20%から 50%も小さいため、高性能でより小さい実装面積が要求されるアプリケーションに最適です。

• 集積回路による高スピード - BGA パッケージでは、マイクロ波帯の周波数スペクトラムでの良好な動作と、高い電気的性能の達成のため、パッケージ構造内にグランドプレーン、グランドリング、およびパワーリングを採用しています。

• 放熱性の向上 - ダイは BGA パッケージの中央に配置され、大部分の GND ピンおよび VCC ピンはパッケージの中央に配置されるため、GND ピンおよび VCC ピンはダイの下に配置されます。その結果、デバイスで発生した熱は GND ピンおよび VCC ピンを介して伝達されます(つまり、GNDピンと VCC ピンがヒートシンクの働きをします)。

1.2. PCB レイアウト用語

この項で定義する一般的用語は PCB レイアウトで使用され、インテル・プログラマブル・デバイスをデザインする場合に必要です。

1.2.1. エスケープ・ルーティング

エスケープ・ルーティングとは、信号をパッケージから PCB 上の他の部品に接続するときに使用される手法です。

1.2.2. マルチレイヤー PCB

BGA パッケージ関連の I/O 数の増加により、マルチレイヤー PCB によるエスケープ・ルーティングが業界標準の方法になっています。信号の PCB 上の他の要素への配線は、複数の PCB レイヤーを介して行われます。

1.2.3. ビア

ビア、またはメッキ・スルー・ホールは、マルチレイヤー PCB で使用され、あるレイヤーから別のレイヤーへ信号を転送します。ビアは、マルチレイヤー PCB にドリルで開けられた実際の穴で、各 PCB レイヤー間を電気的に接続します。すべてのビアはレイヤー間の接続のみに使用され、デバイスのリードやその他の補強材がビアに挿入されることはありません。

次の表に示すのは、ビア寸法の定義に使用される用語です。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

4

表 1. ビア寸法の用語

用語 詳細

アスペクト比 メッキ済みビアの直径に対するビアの長さまたは深さの比率を指します。

ドリル穴径 ボードにドリルで開けられた実際のビアホールの直径を指します。

仕上げ後のビア直径 メッキ完了後のビアホールの直径を指します。

次の表に示す 3 種類のビアは、PCB で一般的に使用されます。

表 2. ビアの種類

タイプ 詳細

スルービア PCB の最上位レイヤーと最下位レイヤーとの相互接続。内部 PCB レイヤーへの相互接続も提供します。

ブラインドビア 最上位レイヤーまたは最下位レイヤーと PCB 内部レイヤーとの相互接続。

エンベデッド・ビア 任意数の内部 PCB レイヤー間を相互接続。

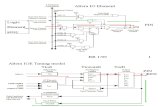

次の図で示すのは、3 つのビアタイプすべてです。

図 -1: ビアの種類

Connection to Layer

Through Via Blind Via Embedded Via

PCB Layers

ブラインドビアとスルービアは、エンベデッド・ビアよりも頻繁に使用されます。ブラインドビアはスルービアよりもコストが高くなりますが、信号トレースをブラインドビアの下に配線すると全体のコストが削減され、必要な PCB レイヤー数が少なくなります。一方、スルービアでは、信号を下位レイヤーに配線することができないため、必要な PCB レイヤー数と全体的なコストが増加する可能性があります。

1.2.4. ビア・キャプチャ・パッド

ビアは、各ビアの周囲に配置されたビア・キャプチャ・パッドを通じて PCB レイヤーと電気的に接続されます。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

5

1.2.5. 表面ランドパッド

表面ランドパッドは PCB 上の領域であり、そこに BGA はんだボールが付着します。パッドのサイズによって、ビアとエスケープ・ルーティングに使用できるスペースが影響されます。通常、表面ランドパッドが使用できるのは次の 2 つの基本デザインです。

• 非はんだマスク定義 (NSMD) 、別名銅定義

• はんだマスク定義 (SMD)

2 つの表面ランドパッドの主な違いは、トレースのサイズ、トレースライン間の間隔、使用できるビアのタイプ、およびはんだリフロー後のはんだボールの形状です。

図 -2: NSMD および SMD ランドパッドの側面図

PCB

Solder MaskOpening

Solder MaskOpening

SolderMask

Surface LandPad

SMD PadNSMD Pad

SolderMask

Surface LandPad

図 -3: NSMD および SMD はんだ接合部の側面図

SMD Solder JointNSMD Solder Joint

BGA Solder Ball

Copper Pad

Solder Mask

PCB

BGA Package

1.2.5.1. 非はんだマスク定義パッド

NSMD パッドでは、はんだマスクの開孔部が銅パッドよりも大きいため、表面ランドパッドの銅表面は完全に露出しており、より大きな領域に BGA ハンダボールが付着できるようになっています。ページ 6の NSMD および SMD ランドパッドの側面図を参照してください。

注意: インテルでは、NSMD パッドを大部分のアプリケーションで使用することをお勧めしています。理由は、柔軟性が高くなり、ストレスが加わる個所が少なくなり、パッド間のライン配線スペースが広くなるためです。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

6

1.2.5.2. はんだマスク定義パッド

SMD パッドでは、はんだマスクは表面ランドパッドの銅表面と重なります。ページ 6 の NSMD およびSMD ランドパッドの側面図を参照してください。この重なりによって大きくなる銅パッドと PCB のエポキシ/ガラス積層体との間の接着強度は、極端な曲げ応力が加えられた場合や、加速熱サイクル試験中に重要になります。ただし、はんだマスクの重なりにより、BGA はんだボールに使用可能な銅表面の量は減少します。

1.2.6. ストリンガー

ストリンガーは、長方形または正方形の相互接続セグメントであり、ビア・キャプチャ・パッドと表面ランドパッドを電気的に接続します。

図 -4: ビア、ランドパッド、ストリンガーおよびビア・キャプチャ・パッド

Surface Land Pad

Stringer Via Capture PadVia

1.3. 高集積 BGA パッケージの PCB レイアウト

高集積 BGA パッケージ用に PCB をデザインするときは、次の要素を考慮してください。

• 表面ランドパッドの寸法

• ビア・キャプチャ・パッドのレイアウトと寸法

• 信号ラインのスペースとトレース幅

• PCB のレイヤー数

注意: 制御寸法の計算は、すべての高集積 BGA 図でミリメートル単位でされています。

1.3.1. 表面ランドパッドの寸法

インテルで行ってきた広範囲にわたるモデリング・シミュレーションと実験的研究により、PCB 上の最適なランドパッドのデザインを決定することで、はんだ接合部の疲労寿命が最長になります。この研究結果によって示されている通り、パッドデザインによってバランスのとれた応力がはんだ接合部に提供されたときに、最良のはんだ接合部の信頼性が得られます。SMD パッドを PCB 上で使用する場合は、表面ランドパッドのサイズを BGA パッドと同じにして、はんだ接合部の応力をバランスのとれたものにしてください。非はんだマスク定義パッドを PCB に使用する場合は、ランドパッドのサイズを BGA パッドより約15%小さくして、はんだ接合部の応力をバランスのとれたものにしてください。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

7

図 -5: BGA パッドの寸法

BGA Substrate

BGA Pad

Solder Ball

A

B

次の表に示すのは、SMD および NSMD のランドパターンに推奨されるパッドサイズです。パッドサイズが小さいとビアとトレース配線の間隔が広くなるので、高集積の基板レイアウトには NSMD パッドを使用してください。

表 3. SMD および NSMD パッドの推奨パッドサイズ

BGA パッドのピッチ BGA パッドの開孔部 (A)(mm) (標準値)

推奨 SMD パッドサイズ(mm)

推奨 NSMD パッドサイズ(mm) (1)

1.27 mm (プラスチック・ボール・グリッド・アレイ (PBGA))

0.60 0.60 0.51

1.27 mm (スーパー・ボール・グリッド・アレイ(SBGA))

0.60 0.60 0.51

1.27 mm (テープ・ボール・グリッド・アレイ(TBGA))

0.60 0.60 0.51

1.27 mm (フリップチップ) (2) 0.65 0.65 0.55

1.00 mm (ワイヤーボンド) (2) 0.45 0.45 0.38

1.00 mm (フリップチップ)(2)、 (3) 0.55 0.55 0.47

1.00 mm (フリップチップ) (2) APEX 20KE 0.60 0.60 0.51

continued...

(1) ステンシル開孔部の推奨事項 - インテルでは、NSMD パッドサイズをステンシルの最小開孔部として使用することをお勧めします。この表に基づく各 BGA パッケージの SMD パッドサイズを超えないようにしてください。

(2) Intel® Device Package Information Datasheetでは、フリップチップ技術を使用した Fineline BGA パッケージは "Thermally Enhanced FineLine BGA" 、ワイヤーボンド・パッケージは "Non-ThermallyEnhanced FineLine BGA" と記載されています。

(3) これは インテル Stratix 10 デバイスには適用されません。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

8

BGA パッドのピッチ BGA パッドの開孔部 (A)(mm) (標準値)

推奨 SMD パッドサイズ(mm)

推奨 NSMD パッドサイズ(mm) (1)

0.80 mm UBGA (ワイヤーボンド) 0.40 0.40 0.34

0.80 mm UBGA (EPC16U88) 0.40 0.40 0.34

0.80 mm UBGA (フリップチップ) 0.425 0.425 0.36

0.80 mm UBGA (フリップチップ) 0.45 0.45 0.38

0.50 mm MBGA 0.30 0.27 0.26

注意: インテル Stratix 10 デバイスパッケージ以降に関する詳細については、それぞれの ManufacturingAdvantage Services (MAS) Guidelines 文書を参照してください。

次の表に示す PCB デザイン・ガイドラインは、VBGA (別名 WLCSP) 0.4 mm ボールピッチ用です。

表 4. VBGA 用推奨パッドサイズ (別名 WLCSP)

BGA パッドのピッチ PCB Cu パッドサイズNSMD (mm)

ソルダーマスク開孔部NSMD (mm)

PCB Cu パッドサイズSMD (mm)

ソルダーマスク開孔部SMD (mm)

0.4 mm VBGA (別名 WLCSP) 0.22 0.32 0.32 0.22

次の図で示すのは、NSMD ランドパッドを使用した場合の 1.00 mm、0.80 mm、および 0.50 mm ピッチのパッケージで使用可能なビアと配線スペースです。

図 -6: 1.00 mm フリップチップ BGA の NSMD ランドパッドに使用可能なビアおよび配線スペースこれは インテル Stratix 10 デバイスには適用されません。

0.53 mm(21.20 mil)

0.53 mm(21.20 mil)

0.47 mm(18.80 mil)

Surface Land Pads

1.00 mm(39.37 mil)

0.94 mm(37.60 mil)

1.00 mm(39.37 mil)

(1) ステンシル開孔部の推奨事項 - インテルでは、NSMD パッドサイズをステンシルの最小開孔部として使用することをお勧めします。この表に基づく各 BGA パッケージの SMD パッドサイズを超えないようにしてください。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

9

図 -7: 0.80 mm UBGA (BT 基板) NSMD ランドパッドに使用可能なビアおよび配線スペース

0.46 mm(18.11 mil)

0.46 mm(18.11 mil)

0.34 mm(13.39 mil)

Surface Land Pads

0.80 mm(31.50 mil)

0.79 mm(31.16 mil)

0.80 mm(31.50 mil)

図 -8: 0.50 mm MBGA NSMD ランドパッドに使用可能なビアおよび配線スペース

0.24 mm(9.45 mil)

0.24 mm(9.45mil)

0.26 mm(10.24 mil)

Surface Land Pads

0.50 mm(19.69 mil)

0.45 mm(17.72 mil)

0.50 mm(19.69 mil)

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

10

関連情報Manufacturing with Intel Field Programmable Gate Array Platform Code Named IntelStratix10

1.3.2. ビア・キャプチャ・パッドのレイアウトと寸法

ビア・キャプチャ・パッドのサイズとレイアウトは、エスケープ・ルーティングに使用できるスペースの大きさに影響を与えます。通常、レイアウトはキャプチャパッドを介して次の 2 つの方法で行います。

• 表面ランドパッドの水平線上に配置

• 表面ランドパッドの対角線上に配置

ビア・キャプチャ・パッドの配置を表面ランドパッドに対して対角線上にするか、または水平線上にするかは、次の点を基準に判断します。

• ビア・キャプチャ・パッドの直径

• ストリンガーの長さ

• ビア・キャプチャ・パッドと表面ランドパッド間の間隔

ページ 11 および表 5 (11 ページ) を使用し、1.00 mm ピッチ BGA パッケージのレイアウトのガイドを NSMD ランドパッドを使用して行います。

図 -9: 1.00 mm フリップチップ BGA NSMD ランドパッド用のビア・キャプチャ・パッドの配置これは インテル Stratix 10 デバイスには適用されません。

Surface land pad

Via capture pad

Vias

Stringer

Stringer length a

Stringer widthb

Minimum clearance between via capture pad and surface land pad

c

Via capture pad diameterdTrace widthe

Space widthfArea for escape routing(この領域は、表面ランドパッドとは異なる PCB レイヤー上にあります。)

g

Diagonally

0.47 mm(18.80 mil)

a

c

1.00 mm(39.37 mil)

d

b

f

e

f

g

In Line

0.53 mm(21.20 mil)

0.47 mm(18.80 mil)

1.00 mm(39.37 mil)

a c

d

b

f

e

f

g

1.00 mm(39.37 mil)

お使いの PCB のデザイン・ガイドラインが次の表のどの計算式にも準拠していない場合は、 IntelPremier Support にお問い合わせください。

表 5. 1.00 mm フリップチップ BGA NSMD ランドパッド用ビアのレイアウトに関する計算式これは インテル Stratix 10 デバイスには適用されません。

レイアウト 計算式

水平線上に配置 a + c + d <= 0.53 mm

対角線上に配置 a + c + d <= 0.94 mm

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

11

表 5 (11 ページ) で示す通り、より大きいサイズのビア・キャプチャ・パッドの配置は、表面ランドパッドに対して水平線上ではなく対角線上に行います。

ページ 12 および表 6 (12 ページ) を使用して、0.80 mm ピッチ U BGA パッケージのレイアウトのガイドを NSMD ランドパッドを使用して行います。

図 -10: 0.80 mm UBGA (BT 基板) NSMD ランドパッド用ビア・キャプチャ・パッドの配置

Surface land pad

Via capture pad

Vias

Stringer

Stringer length a

Stringer widthb

Minimum clearance between via capture pad and surface land pad

c

Via capture pad diameterdTrace widthe

Space widthfArea for escape routing(この領域は、表面ランドパッドとは異なる PCB レイヤー上にあります。)

g

Diagonally

0.34 mm(13.39 mil)

a

c

0.80 mm(31.50 mil)

d

b

f

e

f

g

In Line

0.46 mm(18.11 mil)

0.34 mm(13.39 mil)

0.80 mm(31.50 mil)

a c

d

b

f

e

f

g

0.80 mm(31.50 mil)

お使いの PCB のデザイン・ガイドラインが次の表のいずれの計算式にも準拠していない場合は、mySupport にお問い合わせください。

表 6. 0.80 mm UBGA (BT 基板) NSMD ランドパッド用ビアのレイアウトに関する計算式

レイアウト 計算式

水平線上に配置 a + c + d <= 0.46 mm

対角線上に配置 a + c + d <= 0.68 mm

表 6 (12 ページ) で示す通り、より大きいサイズのビア・キャプチャ・パッドの配置は、表面ランドパッドに対して水平線上ではなく対角線上に行います。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

12

図 -11: 0.5 mm の MBGA ランドパッド用ビア・キャプチャ・パッドの配置

Surface land pad

Via capture pad

Vias

Via capture pad diameterd 0.25 mm(9.84 mil)

0.50 mm(19.685 mil)

d

0.25 mm(9.84 mil)

In Line

0.5 mm ピッチの場合、インテルでは、パッド内の 0.10 mm ビアドリルのマイクロビア技術を使用し、内側の層にトレースを配線することをお勧めします。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

13

図 -12: 0.4 mm VBGA (別名 WLCSP) ランドパッド用ビア・キャプチャ・パッドの配置

Surface land pad

Via capture pad

Vias

Via capture pad diameterd 0.15 mm(5.90 mil)

0.40 mm(15.75 mil)

d

0.25 mm(9.84 mil)

In Line

0.4 mm ピッチの場合、インテルでは、パッド内の 0.10 mm ビアドリルのマイクロビア技術を使用し、内側の層にトレースを配線することをお勧めします。

ビア・キャプチャ・パッドのサイズもまた、PCB 上で配線できるトレース数に影響します。ページ 15 で示すのは、標準およびプレミアムタイプのビア・キャプチャ・パッドのレイアウト例です。標準レイアウトで示しているのは、ビア・キャプチャ・パッドのサイズが 0.660 mm、ビアのサイズが 0.254 mm、そして内部スペースとトレースが 0.102 mm です。このレイアウトでは、ビア間に配線できるトレースは 1 つだけです。さらにトレースが必要な場合は、ビア・キャプチャ・パッドのサイズまたはスペースとトレースのサイズを小さくしてください。

プレミアムタイプのレイアウトで示しているのは、ビア・キャプチャ・パッドのサイズが 0.508 mm、ビアのサイズが 0.203 mm、そして内部スペースとトレースが 0.076 mm です。このレイアウトでは、十分なスペースを確保して、ビア間に 2 つのトレースを配置しています。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

14

図 -13: 1.00 mm フリップチップ BGA 用標準およびプレミアムタイプのビア・キャプチャ・パッドのサイズこれは インテル Stratix 10 デバイスには適用されません。

10.00 mil

26.00 mil

4 mil

39.37 mil

8.00 mil

20.00 mil

3 mil

39.37 mil

Typical Premium

Via

Via Capture Pad

Space

Trace

15.00 mil

(1.0 mm) (1.0 mm)

(0.254 mm) (0.102 mm) (0.203 mm) (0.203 mm)

(0.660 mm) (0.508 mm) (0.381 mm)

次の表に示すのは、1.00 mm フリップチップ BGA 用標準およびプレミアムタイプのレイアウトであり、ほとんどの PCB ベンダーで使用されています。

表 7. 1.00 mm フリップチップ BGA の PCB ベンダーの仕様これは インテル Stratix 10 デバイスには適用されません。

仕様 標準 (mm) プレミアム (mm) 基板厚 > 1.5mm

プレミアム (mm) 基板厚 > 1.5mm

トレースおよびスペース幅 0.1/0.1 0.076/0.076 0.076/0.076

ドリル穴径 0.305 0.254 0.150

仕上げ後のビア直径 0.254 0.203 0.100

ビア・キャプチャ・パッド 0.660 0.508 0.275

アスペクト比 7:1 10:1 10:1

ページ 16 で示すのは、標準およびプレミアムタイプのビア・キャプチャ・パッドのレイアウト例です。標準レイアウトで示しているのは、ビア・キャプチャ・パッドのサイズが 0.495 mm、ビアのサイズが 0.254mm、そして内部スペースとトレースが 0.102 mm です。このレイアウトでは、ビア間に配線できるトレースは 1 つだけです。さらにトレースが必要な場合は、ビア・キャプチャ・パッドのサイズまたはスペースおよびトレースのサイズを小さくしてください。

プレミアムタイプのレイアウトで示しているのは、ビア・キャプチャ・パッドのサイズが 0.419 mm、ビアのサイズが 0.165 mm、そして内部スペースおよびトレースが 0.076 mm です。このレイアウトでは、十分なスペースを確保して、ビア間に 2 つのトレースを配置しています。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

15

図 -14: 0.80 mm UBGA (BT 基板) 用標準およびプレミアムタイプのビア・キャプチャ・パッドのサイズ

10.00 mil

19.50 mil

4 mil

31.50 mil

6.50 mil

16.50 mil

3 mil

31.50 mil

Typical Premium

(0.8 mm) (0.8 mm)

(0.254 mm) (0.102 mm) (0.165 mm)

(0.495 mm) (0.419 mm)

(0.076 mm)

Via

Via Capture Pad

Space

Trace

次の表に示すのは、0.80 mm UBGA 用標準およびプレミアムタイプのレイアウト仕様であり、ほとんどの PCB ベンダーで使用されています。

表 8. 0.80 mm UBGA (BT 基板) の PCB ベンダーの仕様

仕様 標準 (mm) プレミアム (mm) 基板厚 > 1.5mm

プレミアム (mm) 基板厚 <=1.5 mm

トレースおよびスペース幅 0.1/0.1 0.076/0.076 0.076/0.076

ドリル穴径 0.381 0.330 0.254

仕上げ後のビア直径 0.254 0.165 0.127

ビア・キャプチャ・パッド 0.495 0.419 0.381

アスペクト比 8:1 25:1 12:1

ページ 17 で示すのは、ビア・キャプチャ・パッドの標準レイアウト例です。標準レイアウトでは、ビア・キャプチャ・パッドのサイズが 0.25 mm、ビアサイズが 0.10 mm、そして内部スペースおよびトレースが0.068 mm です。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

16

図 -15: 0.50 mm MBGA 用標準ビア・キャプチャ・パッドのサイズ

4 mil

9.84 mil

3.4 mil

19.685 mil(0.5 mm)

(0.10 mm) (0.086 mm)

(0.25 mm)

Typical Via

Via Capture Pad

Space

Trace

次の表に示すのは、0.50 mm MBGA の標準およびプレミアムタイプのレイアウトであり、ほとんどのPCB ベンダーで使用されています。

表 9. 0.50 mm MBGA (BT 基板) の PCB ベンダーの仕様

仕様 標準 (mm)

トレースおよびスペース幅 0.086

仕上げ後のビア直径 0.10

ビア・キャプチャ・パッド 0.25

ページ 18 で示すのは、代表的なビア・キャプチャ・パッドのレイアウト例です。標準レイアウトでは、ビア・キャプチャ・パッドのサイズが 0.25 mm、ビアのサイズが 0.10 mm です。0.40 mm ピッチの場合、コンポーネント層にトレースを配線する十分なスペースがありません。理由は、最小トレース幅が 0.075mm、トレースとパッド間の最小ギャップが 0.086 mm であるためです。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

17

図 -16: 0.40 mm VBGA (別名 WLCSP) 用標準ビア・キャプチャ・パッドのサイズ

15.75 mil(0.40 mm)

4 mil(0.10 mm)

9.84 mil(0.25 mm)

Typical Via

Via Capture Pad

ドリルのサイズ、ビアのサイズ、スペースおよびトレースのサイズ、またはビア・キャプチャ・パッドのサイズに関する詳細は、各 PCB ベンダーに直接お問い合わせください。

1.3.3. 信号ラインのスペースおよびトレース幅

エスケープ・ルーティングの実行機能は、トレース幅とトレース間に必要な最小スペースによって規定されます。信号配線の最小面積は、信号の配線が必要な最小面積です (つまり、2 つのビア間の距離、または 1.00 mm フリップチップ BGA 用のダブルトレースとシングルトレースのエスケープ・ルーティング図中の g)。この面積の計算には次の計算式を使用します。

g = (BGA ピッチ) – d

この領域を介して配線できるトレースの数は、許容ライントレースとスペース幅に基づいています。次の表で示すのは、 g を通して配線できるトレースの合計数です。

表 10. トレース数

トレース数 計算式

1 g >= [2 x (スペース幅)] + トレース幅

2 g >= [3 x (スペース幅)] + [2 x (トレース幅)]

3 g >= [5 x (スペース幅)] + [3 x (トレース幅)]

次の図で示す通り、トレースとスペースのサイズを小さくすることによって、 より多くのトレースを g を通して配線できます。トレース数を増やすと、必要な PCB レイヤー数が減り、全体のコストが下がります。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

18

図 -17: 1.00 mm フリップチップ BGA 用ダブルおよびシングルトレースのエスケープ・ルーティングこれは インテル Stratix 10 デバイスには適用されません。

18.80 mil(0.47 mm)

21.20 mil(0.53 mm)

18.80 mil(0.47 mm)

4.2 mil(0.10 mm)

18.80 mil(0.47 mm)

21.20 mil(0.53 mm)

18.80 mil(0.47 mm)

7.07 mil(0.18 mm)

Double Trace Routing Single Trace Routing

Via Capture Pad

Space

Trace

図 -18: 0.80 mm UBGA 用 (BT 基板) 用ダブルおよびシングルトレースのエスケープ・ルーティング

13.39 mil(0.34 mm)

18.11 mil(0.46 mm)

13.39 mil(0.34 mm)

3.6 mil(0.09 mm)

13.39 mil(0.34 mm)

18.11 mil(0.46 mm)

13.39 mil(0.34 mm)

6.0 mil(0.15 mm)

Double Trace Routing Single Trace Routing

Via Capture Pad

Space

Trace

図 -19: 0.5 mm MBGA 用シングルトレースのエスケープ・ルーティング

10 mil(0.25 mm)

10 mil(0.25 mm)

10 mil(0.25 mm)

3 mil(0.075 mm)

Via Capture Pad

Space

Trace

Single Trace Routing

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

19

1.3.4. PCB レイヤー数

通常、信号配線に必要な PCB レイヤーの数は、ビア間の配線パターンの本数に反比例 (つまり、トレースの本数が増加すると、PCB レイヤーに必要なレイヤー数が減少) します。PCB で必要なレイヤー数の見積もりには、まず次の事項を決定します。

• トレースおよびスペースのサイズ

• ビア・キャプチャ・パッド間に配線されるトレース数

• 使用されるビアのタイプ

使用する I/O ピンを最大数より少なくすると、必要なレイヤー数を減らすことができます。ビアの種類の選択によっても、必要なレイヤー数を減らすことができます。ビアのタイプによって必要な PCB レイヤー数がどのように影響されるかを確認するには、次の項に示すレイアウト例を検討してください。

1.3.4.1. 1.00 mm フリップチップ BGA および 0.80 mm UBGA(BT 基板) の PCB レイアウト例

次の図のブラインド・ビア・レイアウトで必要となるのは、2 つの PCB レイヤーのみです。最初の 2 つのボールからの信号の配線は、直接最初のレイヤーを通します。3 番目および 4 番目のボールからの信号の配線は、ビアを通して 2 番目のレイヤーに出します。5 番目のボールからの信号の配線は、3 番目および4 番目のボール用のビアの下を通して 2 番目のレイヤーに出します。全部で 2 つの PCB 層のみを必要とします。

これとは対照的に、次の図のスルービアのレイアウトでは 3 つの PCB レイヤーが必要です。これは、信号の配線はスルービアの下にはできないためです。 3 番目および 4 番目のボールからの信号の配線は、ビアを経由して 2 番目のレイヤー出すことができますが、5 番目のボールからの信号の配線は、ビアを経由して 3 番目のレイヤーに出す必要があります。この例では、スルービアではなくブラインドビアを使用することで、PCB レイヤーを 1 つ節約しています。

図 -20: 1.00 mm フリップチップ BGA 用 PCB レイアウト例これは インテル Stratix 10 デバイスには適用されません。

Ball 1Ball 2Ball 3Ball 4Ball 5

Blind Via

10-mil Via

5-mil Trace

5番目のボールからの信号は、ビアの下を通って2番目のレイヤーに配線されます。

26-mil ViaCapture Pad

18.80-mil SurfaceLand Pad

Ball 1Ball 2Ball 3

Through Via5番目のボールからの信号は、ビアの下を通って3番目のレイヤーに配線されます。

信号は1番目のレイヤーを通って出てきます。

信号は2番目のレイヤーを通って出てきます。

信号は3番目のレイヤーを通って出てきます。

Ball 4Ball 5

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

20

図 -21: 0.80 mm UBGA (BT 基板) 用 PCB レイアウト例

Ball 1Ball 2Ball 3Ball 4Ball 5

Blind Via

10-mil Via

5-mil Trace

5番目のボールからの信号は、ビアの下を通って2番目のレイヤーに配線されます。

26-mil ViaCapture Pad

13.39-mil SurfaceLand Pad

Ball 1Ball 2Ball 3

Through Via5番目のボールからの信号は、ビアの下を通って3番目のレイヤーに配線されます。

信号は1番目のレイヤーを通って出てきます。

信号は2番目のレイヤーを通って出てきます。

信号は3番目のレイヤーを通って出てきます。

Ball 4Ball 5

1.3.4.2. 0.5 mm 484 ピン MBGA 用 6 レイヤーの PCB 配線方法例

次の図は、Cyclone V 0.5 mm 484 ピン MBGA パッケージ用 6 レイヤーの PCB 配線方法例です。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

21

図 -22: 0.5 mm 484 ピン MBGA 用 6 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 75 µm/75 µm (3 mils/3 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 275 µm (11 mils)4. Via land to line space – 75 µm (3 mils)

1.3.4.3. 0.5 mm 383 ピン MBGA 用 3 レイヤーの PCB 配線方法例

次の図は、Cyclone V GX および Cyclone V E 0.5 mm 383 ピン MBGA パッケージ用 3 レイヤーの PCB 配線方法例です。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

22

図 -23: 0.5 mm 383 ピン MBGA (Cyclone V GX) 用 3 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 75 µm/75 µm (3 mils/3 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 275 µm (11 mils)4. Via land to line space – 75 µm (3 mils)

図 -24: 0.5 mm 383 ピン MBGA (Cyclone V E) 用 3 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 75 µm/75 µm (3 mils/3 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 275 µm (11 mils)4. Via land to line space – 75 µm (3 mils)

1.3.4.4. 0.5 mm 301 ピン MBGA 用 2 レイヤーの PCB 配線方法例

次の図は、Cyclone V 0.5 mm 301 ピン MBGA パッケージ用 2 レイヤーの PCB 配線方法例です。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

23

図 -25: 0.5 mm 301 ピン MBGA 用 2 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 75 µm/75 µm (3 mils/3 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 275 µm (11 mils)4. Via land to line space – 75 µm (3 mils)

1.3.4.5. 0.5 mm 153 ピン MBGA 用 2 レイヤーの PCB 配線方法例

2014 年に、M153 パッケージが MAX 10 デバイスファミリーに導入されています。ボールピッチが0.5 mm の低密度のボールアレイを実装しています。0.5 mm 153 ピン MBGA 用 2 レイヤーの PCB配線方法の例を次の図に示します。

図 -26: 0.5 mm 153 ピン MBGA 用 2 レイヤーの PCB 配線方法例Top PCB Layer Routing

Routing Assumptions1. Line width/space - 3 mils/3 mils2. Hole drill size - 6 mils3. Via land size - 11 mils4. Via land to line space - 3 mils

A1 Corner 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

ABCDEFGHJKL

MNPR

Bottom PCB Layer Routing

A1 Corner(Top View) (Bottom View)

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

24

1.3.4.6. 0.5 mm 144 ピン MBGA 用 4 レイヤーの PCB 配線方法例

144 ピン MBGA パッケージ用配線のレイアウト例を次の図に示します。144 ピンパッケージは 4 レイヤーに配線されています。

図 -27: 0.5 mm 144 ピン MBGA 用 4 レイヤーの PCB 配線方法例

1.3.4.7. 0.5 mm 256 ピンおよび 100 ピン MBGA 用 2 レイヤーの PCB 配線方法例

2006 年には、0.5mm ピッチ Micro FineLine BGA® (MBGA) パッケージが MAX® II デバイスファミリーに導入されています。このパッケージのサイズと重量は、携帯用アプリケーションや基板スペースや電力に制約があるアプリケーションに適しています。ピンのレイアウトおよびピン・アサインメントのデザインによって、はんだパッドからの信号がスルーホール・ビアを使用して 2 レイヤーに配線できるようになっています。次の図で示す 2 レイヤーの配線方法例は、それぞれ 100 ピンおよび 256 ピンのMBGA に対するものです。このレイアウトタイプが適しているのは、PCB 厚さが 1.5 mm 以下の場合です。PCB 厚さが 1.5 mm を超える場合、ブラインドビアの使用がより適している可能性があるのはエスケープ・ルーティングです。2006 年以降、MBGA パッケージがポートフォリオにさらに追加されており、そのエスケープ・ルーティングの例をこの項で示しています。

この項の PCB 配線方法例では VCCN と VSS を使用します。ピンテーブルでは、VCCN と VSS はそれぞれ VCCIO と GND に対応しています。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

25

図 -28: 0.5 mm 256 ピン MBGA 用 2 レイヤーの PCB 配線方法例

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

26

図 -29: 0.5 mm 100 ピン MBGA 用 2 レイヤーの PCB 配線方法例

1.3.4.8. 0.4 mm 81 ピン VBGA (別名 WLCSP) 用 4 レイヤーの PCB 配線方法例

MAX 10 デバイスファミリーでは、81 ピンおよび 36 ピン VBGA パッケージ用の最初の VBGA (別名WLCSP) も導入されました。次の図は、0.4 mm 81 ピン VBGA (別名 WLCSP) パッケージ用 4 レイヤーの PCB 配線方法例です。

図 -30: 0.4 mm 81 ピン VBGA (別名 WLCSP) 用 4 レイヤーの PCB 配線方法例

9 8 7 6 5 4 3 2 1

ABCDEFGHJ

Top PCB Layer Routing PCB Layer 2 Routing PCB Layer 3 Routing Bottom PCB Layer Routing

A1 Corner A1 Corner A1 Corner A1 Corner

Routing Assumptions1. Line width/space – 75 µm/85 µm2. Neck width/space (at layer 2 and 3) – 50 µm/50 µm3. Hole drill size – 100 µm4. Via land size – 230 µm5. BGA solder pad diameter – 230 µm6. BGA solder mask opening – 330 µm

(Top View) (Bottom View)(Top View) (Bottom View)

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

27

1.3.4.9. 0.5 mm 68 ピン MBGA 用 2 レイヤーの PCB 配線方法例

2007 年には、68 ピンおよび 144 ピン MBGA パッケージが MAX IIZ デバイスファミリーに導入されました。68 ピン MBGA パッケージ用配線レイアウト方法例を次の図に示します。68 ピンパッケージの配線は 2 レイヤーです。

図 -31: 0.5 mm 68 ピン MBGA (個別 VCCN バンク) 用 2 レイヤーの PCB 配線方法例

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

28

図 -32: 0.5 mm 68 ピン MBGA (共通 VCCN バンク) 用 2 レイヤーの PCB 配線方法例

1.3.4.10. 0.4 mm 36 ピン VBGA (別名 WLCSP) 用 2 レイヤーの PCB 配線方法例

次の図は、0.4 mm 36 ピン VBGA (別名 WLCSP) パッケージ用 2 レイヤーの PCB 配線方法例です。

図 -33: 0.4 mm 36 ピン VBGA (別名 WLCSP) 用 2 レイヤーの PCB 配線方法例

Top PCB Layer Routing Bottom PCB Layer Routing

Routing Assumptions1. Line width/space – 75 µm/85 µm2. Neck width/space – 50 µm/50 µm3. Hole drill size – 100 µm4. Via land size – 230 µm5. BGA solder pad diameter – 230 µm6. BGA solder mask opening – 330 µm

6 5 4 3 2 1

ABCDEF

A1 Corner(Top View) (Bottom View)

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

29

1.3.4.11. 0.8 mm 324 ピン UBGA 用 3 レイヤーの PCB 配線方法例

MAX 10 324 ピン UBGA パッケージ用配線のレイアウト例を次の図に示します。324 ピンパッケージの配線は 3 レイヤーです。

図 -34: 0.8 mm 324 ピン UBGA 用 3 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 100 µm/100 µm (4 mils/4 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 300 µm (12 mils)4. Via land to line space – 100 µm (4 mils)

1.3.4.12. 0.8 mm 169 ピン UBGA 用 3 レイヤーの PCB 配線方法例

MAX 10 169 ピン UBGA パッケージ用配線のレイアウト方法の例を次の図に示します。169 ピンパッケージの配線は 3 レイヤーです。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

30

図 -35: 0.8 mm 169 ピン UBGA 用 3 レイヤーの PCB 配線方法例

Routing Assumptions1. Line width/space – 100 µm/100 µm (4 mils/4 mils)2. Hole drill size – 150 µm (6 mils)3. Via land size – 300 µm (12 mils)4. Via land to line space – 100 µm (4 mils)

1.4. AN 114 : インテル・プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインの文書改訂履歴

ドキュメント・バージョン

変更内容

2018.10.09 • インテル Stratix 10 の情報を削除しました。 インテル Stratix 10 パッケージおよびそれ以降の詳細については、それぞれ個別の Manufacturing Advantage Services (MAS) Guidelines 文書を参照してください。

• SMD および NSMD パッドの推奨パッドサイズ表を更新して、0.80 mm UBGA (フリップチップ) 情報を含めました。

2018.03.01 • 商標をインテルに変更しました。• このドキュメントの名前を Board Design Guidelines for Intel Programmable Device Packagesに変更しまし

た。• 「SMD および NSMD パッドの推奨パッドサイズ」の表の 0.50 mm MBGA の BGA パッド開孔部 (A) のサイズを

0.40 mm から 0.30 mm に修正しました。

日付 バージョン 変更内容

2017 年 2 月 2017.02.24 • 0.8 mm 169 ピン UBGA 用 3 レイヤーの PCB 配線方法例の項を追加しました。

• 0.8 mm 324 ピン UBGA 用 3 レイヤーの PCB 配線方法例の項を追加しました。

• NF43、UF50、および HF55 パッケージ用推奨 Stratix 10 ステンシルデザインの図を更新しました。

• 表面ランドパッドの寸法の項に編集上の修正を行いました。continued...

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

31

日付 バージョン 変更内容

• ビア・キャプチャ・パッドのレイアウトおよび寸法の項に編集上の修正を行いました。

• 推奨 Stratix 10 パッドパターン (PCB 側) の項に編集上の修正を行いました。

• テキストのマイナーな編集を行いました。

2016 年 11 月 2016.11.23 • 推奨 Stratix 10 パッドパターン (PCB 側) の項を追加しました。• Stratix 10 PCB 製造上の推奨事項の項を追加しました。• 0.5 mm 301 ピン MBGA 用 2 レイヤーの PCB 配線方法例の項

を追加しました。• 0.5 mm 383 ピン MBGA 用 3 レイヤーの PCB 配線方法例の項

を追加しました。• 0.5 mm 484 ピン MBGA 用 6 レイヤーの PCB 配線方法例の項

を追加しました。• Stratix 10 デバイスの NSMD および SMD パッドの図を追加しま

した。• Stratix 10 デバイスの推奨パッドサイズの表を追加して、Stratix

10 デバイスの 1.00 mm (フリップチップ) を含めました。

2014 年 12 月 2014.12.15 • WLCSP の推奨パッドサイズの表を追加しました。• 0.5 mm MBGA ランドパッド用ビアレイアウトの計算式の表を追

加しました。• 0.5 mm VBGA ランドパッド用ビアレイアウトの計算式の表を追

加しました。• 0.50 mm MBGA の PCB ベンダーの仕様の表を追加しました。• 0.40 mm VBGA の PCB ベンダーの仕様の表を追加しました。• 0.50 mm MBGA NSMD ランドパッドに使用可能なビアおよび配

線スペースの図を追加しました。• 0.5 mm MBGA ランドパッド用ビア・キャプチャ・パッドの配線の図

を追加しました。• 0.4 mm VBGA ランドパッド用ビア・キャプチャ・パッドの配線の図

を追加しました。• 0.50 mm MBGA 用標準ビア・キャプチャ・パッド・サイズの図を追

加しました。• 0.40 mm VBGA 用標準ビア・キャプチャ・パッド・サイズの図を追加

しました。• 0.5 mmMBGA 用シングルトレースのエスケープ・ルーティングの

図を追加しました。• 0.80 mm UBGA (BT 基板) NSMD ランドパッドに使用可能なビ

アおよび配線スペースの図を更新しました。

2014 年 9 月 5.3 • mm 単位の寸法をそれぞれの図に追加しました。• 0.80 mm UBGA (BT 基板) の PCB メーカーの仕様を更新しまし

た。• 0.5 mm 153 ピン MBGA 用 2 レイヤーの PCB 配線方法例を追

加しました。• 0.4mm 81 ピン VBGA 用 4 レイヤーの PCB 配線方法例を追加し

ました。• 0.4mm 36 ピン VBGA 用 2 レイヤーの PCB 配線方法例を追加し

ました。

2014 年 1 月 5.2 0.80 mm UBGA (BT 基板) パッケージを追加しました。

continued...

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン フィードバック

32

日付 バージョン 変更内容

2007 年 12 月 5.1 追加例を 15 ページの「PCB レイヤー数」に追加しました。

2007 年 5 月 5.0 • 表 3 を更新して、0.5mm MBGA 用パッドの推奨事項を含めました。

• 表 6 を更新して、最新の PCB ベンダーのケイパビリティーを反映しました。

• MBGA アップデートを 15 ページの「PCB レイヤー数」の項に追加しました。

• 図 16 および 17 を追加しました。

2006 年 2 月 4.0 ドキュメント名を Designing With High-Density BGA Packagesfor Altera Devices から Designing With FineLine BGAPackages for APEX, FLEX, ACEX, MAX 7000 & MAX 3000Devices に変更しました。

1. AN 114 : インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドラインAN-114 | 2018.10.09

フィードバック AN 114:インテル® プログラマブル・デバイス・パッケージのボード・デザイン・ガイドライン

33