Informe Previo 3 Circuitos Electronicos

-

Upload

tecnicoelectrico2014 -

Category

Documents

-

view

84 -

download

14

description

Transcript of Informe Previo 3 Circuitos Electronicos

-

SECION #3 INFORME PREVIO DE CIRCUITOS COMBINACIONALES MSI

I. OBJETIVO:

Comprobar el funcionamiento de los circuitos integrados que agrupan a los decodificadores, codificadores, multiplexores, demultiplexores y comparadores.

experimentalmente la operacin de las compuertas digitales bsicas.

Emplear los circuitos de mediana escala de integracin para la construccin de circuitos de diversos propsitos.

Analizar las posibilidades de ampliacin de cada uno de los circuitos experimentados.

III. INFORME PREVIO:

1. Analizar y sealar las caractersticas elctricas y electrnicas de los CI-TTL: 74LS85,

74HC85, 74LS43, 74LS148, 74LS42, 74LS45, 74LS46, 74LS47, 74LS48, 74LS49 74LS138,

74LS150, 74LS151 en base a las hojas de datos (no copiar los datashetts)

COMPARADOR

DECODIFICADOR

MULTIPLEXOR

-

2.Explicar brevemente los tipos de CI-TTL que operan como COMPARADORES

CODIFICADORES Y DECODIFICADORES.

CODIFICADOR

Es un circuito combinacional con 2N

entradas y N salidas, cuya misin es presentar en la

salida el cdigo binario correspondiente a la entrada activada. Se puede decir que tiene un

trabajo inverso al decodificador.

Existen dos tipos fundamentales de codificadores: codificadores sin prioridad y

codificadores con prioridad. En el caso de codificadores sin prioridad, puede darse el caso

de salidas cuya entrada no pueda ser conocida: por ejemplo, la salida 0 podra

indicar que no hay ninguna entrada activada o que se ha activado la entrada nmero

0. Adems, ciertas entradas pueden hacer que en la salida se presente la suma lgica de

dichas entradas, ocasionando mayor confusin.

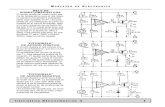

APLICACIONES DEL CODIFICADOR

Un ejemplo es el de la figura q muestra un diagrama que corresponde a una aplicacin de

un teclado lineal hexadecimal realizado con expansin de dos codificadores

74148. Este circuito detecta cuando ha sido pulsada una o ms teclas y la convierte en su

correspondiente cdigo binario de cuatro bits. Al presionar simultneamente ms de una

tecla, entonces aparece en la salida (O0, O1, O2, O3), la combinacin binaria de la

tecla ms significativa del cdigo hexadecimal entrante. La lnea de salida (T_P) indica,

con un uno, el momento cuando se presiona alguna tecla.

+

Figura Teclado lineal hexadecimal implementado con codificadores 74148.

-

DECODIFICADOR

Es un dispositivo que acepta una entrada digital codificada en binario y activa una salida.

Este dispositivo tiene varias salidas, y se activar aquella que establezca el cdigo

aplicado a la entrada. Para que el decodificador pueda mostrar su salida debe estar

debidamente habilitado. (Patilla E). Se clasifican segn el tipo y nmeros de entradas y

salida entregada.

As se tienen decoficadores de siete segmentos, decodificador decimal, de BCD a decimal,

etc.

APLICACIONES DEL DECODIFICADOR

Las aplicaciones de los circuitos decodificadores son diversas, entre las cuales se

pueden citar: los decodificadores de direcciones, decodificador de dispositivos de

Entrada/Salida en un sistema de desarrollo o computadora, convertidores de cdigo,

generador de funciones de conmutacin, etc.

COMPARADOR

Un circuito comparador combinatorio compara dos entradas binarias (A y B de n bits) para

indicar la relacin de igualdad o desigualdad entre ellas por medio de "tres banderas lgicas"

que corresponden a las relaciones A igual B, A mayor que B y A menor que B. Cada una de

estas banderas se activara solo cuando la relacin a la que corresponde sea verdadera, es

decir, su salida ser 1 y las otras dos producirn una salida igual a cero.

-

Ctodo Comn

En los de tipo de ctodo comn, todos

los ctodos de los leds o segmentos estn

unidos internamente a una patilla comn

que debe ser conectada a potencial

negativo (nivel 0). El encendido de

cada segmento individual se realiza

aplicando potencial positivo (nivel 1)

por la patilla correspondiente a travs

de una resistencia que lmite el paso de

la corriente.

Es aquel donde los ctodos de todos los

leds se conectan internamente al punto

de unin U y los nodos se encuentran

disponibles desde afuera del integrado.

Dentro de la familia de circuitos TTL se les denomina a estos circuitos con el nmero 7485

y manejan entradas de 4 bits, adems de que tambin se les puede conectar en cascada para

manejar entradas ms grandes.

Diseo de un circuito comparador de 2 bits.

Para este caso solo se requiere crear la tabla de verdad correspondiente y luego determinar

las funciones booleanas que producen las salidas requeridas.

Sean A y B entradas de un bit, entonces:

3.Explicar las diferencias internas y de caractersticas de los display individuales y de

varios dgitos en un pack

Displays de siete segmentos de 1y 2 digitos

nodo Comn

En los de tipo de nodo comn, todos los

nodos de los leds o segmentos estn

unidos internamente a una patilla comn

que debe ser conectada a potencial

positivo (nivel 1). El encendido de cada segmento individual se realiza

aplicando potencial negativo (nivel 0) por la patilla correspondiente a travs de

una resistencia que lmite el paso de la

corriente.

Es aquel donde los nodos de todos los

leds se conectan internamente al punto

de unin U y los ctodos se encuentran

disponibles desde afuera del integrado.

-

CIs 74LS47 (USA DISPLAY DE ANODO COMUN)

El 74LS47 es un decodificador "decodifica" un cdigo de entrada en otro. Es decir,

transforma una combinacin de unos y cero, en otra combinacin, en particular transforma

el cdigo binario en el cdigo de 7 segmentos. El decodificador recibe en su entrada el

nmero que ser visualizado en el display. Posee 7 salidas, una para cada segmento. Para

un valor de entrada, cada salida toma un estado determinado (activada o desactivada).

Figura Esquema de un decodificador

El decodificador recibe en su entrada el nmero que ser

visualizado en el display. Posee 7 salidas, una para cada segmento.

Para un valor de entrada, cada salida toma un estado determinado

(activada o desactivada).

La entrada consiste en 4 patas o pines donde el decodificador recibe

los nmeros binarios. Podemos ingresar valores de 0 a 9 en formato

binario.

Para ingresar un "0" en un pin, conectaremos el mismo al terminal negativo de la fuente.

Para ingresar un "1", vamos a conectarlo al terminal positivo. Este es un decodificador

TTL, por lo que la fuente debe ser de 5v.

CIs 74LS48 (USA DISPLAY DE CATODO COMUN)

El 'LS48 traduce 4 lneas de de datos de entrada en BCD (8421) en cdigos numricos de 7

segmentos y provee a las 7 correspondientes salidas de resistencias pull-up. estas salidas

pueden servir como seales lgicas, con una salida HIGH (estado alto) correspondiente al

segmento encendido, o puede proveer 1,3 mA para activar el segmento a travs de la base

de un transistor npn. Las entradas auxiliares proveen prueba de lmpara, parpado y

funciones de supresin de cero.

El 'LS48 decodifica la entrada segn el patrn indicado en la tabla de verdad.

-

4. Configurar un circuito que indique en cuatro display BAJO y ALTO para cero y uno

lgico respectivamente de cierta entrada.

-

5. Analizar y efectuar el clculo del siguiente requerimiento : disear la funcin

empleando un multiplexor de 16 canales tipo 74150.

SOLUCION

Diagrama de Conexin del 74150

Mapa de Karnaugh

Tabla de Verdad

Diseo