Ingeniería en Comunicaciones y Electrónica · Apéndice B. Programa ensamblador para el...

Transcript of Ingeniería en Comunicaciones y Electrónica · Apéndice B. Programa ensamblador para el...

Instituto Politécnico Nacional

Escuela Superior de Ingeniería Mecánica y Eléctrica

ESIME Unidad Culhuacan

Ingeniería en Comunicaciones y Electrónica

Reporte Final del Proyecto

“Diseño y construcción de un convertidor inversor de

potencia de 500 W con control digital de modulación de

ancho de pulso sinusoidal para el Laboratorio de

Electrónica de la ESIME Culhuacan”

Datos de los Participantes:

M. en C. Mario Ponce Flores

Dr. Ismael Araujo Vargas

Ing. Fermín Valencia Figueroa

Registro SIP: 20080940

Periodo del Proyecto: Enero 2008 – Diciembre 2008

Reporte Final del Proyecto SIP 20080940

Contenido

1. Resumen ......................................................................................................................... 1 2. Introducción.................................................................................................................... 1 3. Métodos y Materiales ..................................................................................................... 2

3.1 Inversores de Potencia ............................................................................................ 2 3.2 Inversor Medio Puente ........................................................................................... 3 3.3 Inversor Puente Completo ...................................................................................... 4 3.4 Análisis Armónico.................................................................................................. 5 3.5 Modulación de Ancho de Pulso Sinusoidal............................................................ 7 3.6 Principios de Modulación de Ancho de Pulso Sinusoidal...................................... 7 3.7 Otras técnicas de PWM ........................................................................................ 10 3.8 Diseño del prototipo inversor de 500 W............................................................... 10 3.9 Descripción de prototipo ...................................................................................... 10 3.10 Etapa de Potencia ................................................................................................. 10 3.11 Etapa de Control ................................................................................................... 11

4. Resultados experimentales ........................................................................................... 12 5. Impacto del proyecto .................................................................................................... 14 6. Conclusiones................................................................................................................. 14 7. Referencias ................................................................................................................... 15 8. Apéndice A. Figuras .................................................................................................... 16 9. Apéndice B. Programa ensamblador para el ATMEGA8535 ..................................... 29 10. Apéndice C. Circuito impreso y mascarillas del prototipo inversor ....................... 33

IPN ESIME Culhuacan ii

Reporte Final del Proyecto

“Diseño y construcción de un convertidor inversor de potencia de

500 W con control digital de modulación de ancho de pulso

sinusoidal para el Laboratorio de Electrónica de la ESIME

Culhuacan”

1. Resumen

El desarrollo de un prototipo inversor de potencia con modulación de ancho de

pulso sinusoidal (SPWM) es presentado en este reporte. El prototipo consiste de una etapa

de potencia y una de control, la cual un microcontrolador es el encargado de manipular al

inversor de potencia con un algoritmo que genera una SPWM de alta frecuencia. Sin

embargo, los componentes del inversor deben ser los apropiados para operar con

modulación a alta frecuencia y deben ser comerciales para construir el prototipo con fines

académicos. El principio de funcionamiento del inversor puente completo con SPWM, el

diseño y su construcción son descritos a lo largo de este reporte en conjunto con resultados

experimentales obtenidos con un prototipo de 500 W.

2. Introducción

La carrera de Ingeniería en Comunicaciones y Electrónica de ESIME Culhuacan

requiere de un prototipo convertidor de potencia para justificar los fundamentos y

principios de operación de inversores, o convertidores de CD-CA, de potencia que son

tratados en la materias de Electrónica de Potencia 1 y 2. A su vez, el alumno de esta

carrera requiere concretar el aprendizaje adquirido en el aula a través de la construcción de

un prototipo inversor de potencia, que actualmente es un sistema ampliamente usado en la

vida moderna para suministrar energía a cargas de CA a partir de un suministro de CD.

IPN ESIME Culhuacan 1

Reporte Final del Proyecto SIP 20080940

En respuesta a esta necesidad de las materias de Electrónica de Potencia 1 y 2 y para

cumplir con un eficiente desempeño del proceso enseñanza-aprendizaje de la carrera de

Ingeniería en Comunicaciones y Electrónica, este documento presenta el reporte final de la

propuesta de estudio para desarrollar un convertidor inversor de potencia de 500 W que

demuestre los principios básicos de inversión eléctrica y sustente la comprensión de temas

de control, electrónica básica, circuitos y microcontroladores en el desarrollo de un

prototipo. Primeramente, este protocolo muestra brevemente los fundamentos básicos de

los convertidores inversores de potencia. Posteriormente, se plantean los métodos de

control más comunes para inversores de potencia. Además, se describe uno de los métodos

de modulación de ancho de pulso (pulse width modulation, PWM) para controlar inversores

de potencia. Al final de este documento, se describe el desarrollo y la construcción de un

prototipo inversor de potencia de 500 W, el equipo y material empleado, los recursos

humanos involucrados y resultados experimentales obtenidos con el prototipo inversor de

potencia desarrollado.

3. Métodos y Materiales

3.1 Inversores de Potencia

Los inversores de potencia son usados para producir un suministro de potencia de

corriente alterna, CA, desde un suministro de corriente directa, CD. Estos sistemas son de

los más importantes convertidores de potencia ya que son empleados para producir

suministros de voltaje variable y frecuencia variable para controlar motores de CA, y

también para producir suministros de voltaje fijo y frecuencia fija para Sistemas

Ininterrumpibles de Potencia (Uninterrumpible Power Supplies, UPS). Las Figuras 1(a) y

1(b) muestran diagramas a bloques típicos de un sistema controlador para un motor de CA

y un sistema UPS. En estos diagramas se puede observar que el suministro de CD, del cual

los inversores operan, es normalmente la línea alterna principal rectificada y filtrada.

IPN ESIME Culhuacan 2

Reporte Final del Proyecto SIP 20080940

3.2 Inversor Medio Puente

La operación básica de un inversor puede ser explicada a través del circuito

mostrado en la Figura 2(a). Este circuito consta de un riel de CD, un filtro de dos

capacitores en serie con un nodo G, y un tótem o pierna inversora. El tótem está formado

por dos transistores Q1 y Q2 conectados respectivamente en antiparalelo con dos diodos D1

y D2 y conectados en serie mediante un nodo R. Los transistores mostrados en la Figura

2(a) son MOSFETs, pero alternativamente pueden ser usados BJTs, IGBTs, FETs, GTOs,

etc. de acuerdo con la aplicación.

Las señales de control que definen el estado de los transistores de la Figura 2(a) son

mostradas en la parte superior de la Figura 3. La conmutación alternada de Q1 y Q2 causan

que el voltaje entre los nodos R y G, vRG se polarice con ±VS como se muestra en la Figura

3. Asumiendo una carga conectada entre los nodos R y G, la forma de onda de la corriente

de carga, iLoad, será de acuerdo a la impedancia de la carga. Por ejemplo, si la carga es

puramente resistiva la forma de onda de iLoad será cuadrada; pero si la carga es puramente

inductiva, iLoad será triangular. Esto se puede observar en las dos formas de onda inferiores

de la Figura 3. De esta manera, una carga RL con una constante de tiempo intermedia

causará que la forma de onda de iLoad sea exponencial limitada entre una cuadrada y una

triangular.

iLoad en la Figura 3 indica que el tótem deberá ser capaz de conducir una corriente

bidireccional ya que iLoad puede cambiar el sentido de flujo. Esta es la razón para conectar

D1 y D2 en antiparalelo con Q1 y Q2 como se muestra en la Figura 2(a). En caso que alguno

de esto transistores sea activado y que el sentido de flujo de iLoad sea opuesto al del

transistor, el diodo el antiparalelo al transistor permitirá el flujo de iLoad; de lo contrario el

transistor activo conducirá iLoad.

Es evidente que el tótem del circuito de la Figura 2(a) es capaz de mantener una

operación de cuatro cuadrantes, como debe ser para un sistema de AC; sin embargo, la

correcta operación de cualquiera de estos tótems prohíbe la activación simultanea de sus

IPN ESIME Culhuacan 3

Reporte Final del Proyecto SIP 20080940

transistores superior e inferior, ya que esto causaría un corto circuito y ambos transistores

serían destruidos.

El circuito de la Figura 2(a) es muy popular en la práctica ya que los suministros de

potencia con derivación central no son muy comunes y resultan ser complejos. El rango de

potencia para la operación de este circuito es menor a unos cuantos cientos de Watts debido

a que la energía es suministrada por medio de la derivación central del arreglo capacitivo.

3.3 Inversor Puente Completo

El circuito inversor puente completo, también conocido como puente H, se presenta

en la Figura 2(b). El circuito de esta figura muestra que dos tótems forman al inversor

puente completo y que actúan como interruptores de dos polos y un tiro. La operación de

este circuito es similar a la del inversor medio puente, a diferencia que la carga está

conectada entre los nodos R y Y, y puede ser explicada usando las formas de onda de la

Figura 4.

La Figura 4 muestra en la parte superior las señales de control vgs1, vgs2, vgs3 y vgs4

que determinan los estados de Q1, Q2, Q3, y Q4. Se hace notar que Q1 y Q3 son activados

simultáneamente y alternadamente de Q2 y Q4. La derivación central del filtro capacitivo

del riel de CD, nodo G, es usado como referencia para obtener los voltajes vRG y vYG,

tercera y cuarta formas de onda de la Figura 4. El voltaje de la carga es vRY = vRG – vYG, que

se muestra como la quinta forma de onda de la Figura 4 y la corriente iLoad es determinada

nuevamente por la impedancia de la carga. La forma de onda de iLoad será cuadrada para

una carga resistiva y será triangular para una carga inductiva, lo cual es mostrado en la

parte inferior de la Figura 4 donde se indica el patrón de conducción de los dispositivos.

Para el caso de una carga resistiva los diodos son teóricamente innecesarios; sin embargo,

son siempre incluidos en cualquier realización práctica.

Un método más sofisticado de control de un inversor puente completo se obtiene

desplazando la fase del tótem Y con un ángulo γ. La operación descrita anteriormente

IPN ESIME Culhuacan 4

Reporte Final del Proyecto SIP 20080940

consideró que γ = 0, pero γ puede tomar valores dentro del rango 0 ≤ γ ≤ π. Por ejemplo,

con un desfase γ diferente de cero, la formas de onda de la Figura 4 son modificadas como

las mostradas en la Figura 5, y el voltaje en la carga, vRY, toma en esta figura una forma de

onda casi-cuadrada o de tres niveles.

Las ventajas de la estrategia de desplazamiento de fase entre tótems y las

propiedades de las formas de onda vRG, vYG y vRY de los inversores medio puente y puente

completo se pueden entender más a fondo utilizando un análisis armónico.

3.4 Análisis Armónico

El análisis armónico de vRG y vRY puede ser simplificado empleando un conjunto de

pulsos rectangulares. Si los amplitudes de los componentes armónicos de un pulso son

conocidos, entonces, las amplitudes de los armónicos de las forma de onda completa de vRG

y vRY pueden ser obtenidas por medio de sumas. Los componentes complejos de la serie de

Fourier de un pulso rectangular, como el mostrado en la Figura 6, son calculados como

sigue:

α

α

δα

δα

θ

δδ

πδ

θπ

jnnn

jnSn

jnSn

eKA

en

nVA

deVA

−

−

+

−

−

=

=

= ∫

)()(

)(

)(

sin21

…(1)

donde:

δδ

πδ

nnVK Sn

sin)( = es la magnitud de cada armónico y depende del ancho de pulso.

αjne− es la fase que contiene los pesos relativos de los términos cosinusoidal y

sinusoidal de la serie de Fourier trigonométrica.

La forma de onda de vRG de la Figura 3 consiste de dos pulsos rectangulares de

amplitud ±VS/2 y ancho δ = π/2; estando el pulso positivo centrado en π/2 y pulso negativo

en 3π/2. De esta forma el contenido armónico de vRG puede ser calculado usando la

ecuación (1) y superposición como sigue:

IPN ESIME Culhuacan 5

Reporte Final del Proyecto SIP 20080940

( )

imparn

jnSn

jnjnSnRG

enjVA

een

nVA

=

−

−−

=

−=

π

ππ

π

ππ

ππ

)(

232)( 2

2sin22

…(2)

La forma de onda de vYG de la Figura 3 es idéntica a vRG pero con un desfase de π-γ,

y por lo tanto los componentes armónicos de vYG son:

( )

( )

imparn

jnSnYG

imparn

jnjnSnYG

enjVA

eenjVA

=

−−

=

−−−

=

=

γπ

γππ

π

π

2)(

)(

…(3)

Usando las expresiones (2) y (3) los componentes armónicos del voltaje de salida

vRY pueden ser calculados como sigue:

( ){ }( )[ ] ( )

imparn

jnSnRY

imparn

jnjnSnRY

nYGnRGnRY

enjnjVA

eenjVA

AAA

=

−−

=

−−−

±=

−=

−=

2/3)(

2)(

)()()(

2/cos2 γπ

γππ

γπ

π …(4)

y la amplitud de los armónicos de la serie trigonométrica de Fourier para vRY son:

( )imparn

SnRYnRY n

nVAV

=

== 2/cos42 )()( γπ

…(5)

La expresión (5) muestra que la amplitud de los armónicos de vRY son dependientes

de γ, y si se mantiene el desfase entre tótems con γ = π/3 todos los armónicos múltiplos de 3

son cero. Esto resulta ser una ventaja porque el número de armónicos predominantes es

disminuido en gran medida y la calidad de la forma de onda de vRY será mejorada.

IPN ESIME Culhuacan 6

Reporte Final del Proyecto SIP 20080940

3.5 Modulación de Ancho de Pulso Sinusoidal

En la sección anterior se asumió que los dispositivos de los inversores analizados

son conmutados a la misma frecuencia que la frecuencia del voltaje de salida, por ejemplo,

los dispositivos en una pierna inversora son activados y desactivados a una frecuencia de 60

Hz para obtener una forma de onda cuadrada de 60 Hz. Esta técnica produce una pobre

aproximación a una onda sinusoidal y las ondas sinusoidales son requeridas en la mayoría

de las aplicaciones de potencia.

La calidad de las formas de onda de voltaje puede ser mejorada conmutando los

dispositivos de potencia a una alta frecuencia y usando alguna técnica de modulación, de tal

forma que la frecuencia fundamental del voltaje de salida sea la requerida. Sin embargo,

además de la frecuencia fundamental, componentes armónicos de alta frecuencia serán

obtenidos causados por la conmutación de alta frecuencia de los dispositivos, estando estos

componentes en bandas laterales y en frecuencias múltiples enteras.

La modulación de ancho de pulso sinusoidal es la técnica más efectiva para obtener

una forma de onda de voltaje de alta calidad y su principio de operación se describe a

continuación.

3.6 Principios de Modulación de Ancho de Pulso Sinusoidal

El principio de modulación de ancho de pulso sinusoidal (SPWM) puede ser

explicado con referencia a las formas de onda de la Figura 7. Las primeras formas de onda

mostradas en esta figura son la portadora vCarrier y la modulante vMod. vCarrier es una señal

triangular de alta frecuencia y múltiple de la frecuencia de salida requerida, fS. vMod es una

señal sinusoidal de frecuencia fS. La comparación instantánea de vCarrier y vMod resulta en

una serie de pulsos modulados en ancho de pulso que se muestran en la segunda forma de

onda de la Figura 7, vgs1,3, y en su versión complementada mostrada en la tercera forma de

onda de la Figura 7, vgs2,4. Por ejemplo, si vMod es mayor que vCarrier entonces el estado de

vgs1,3 es “1”, de lo contrario es “0”. Esta técnica de modulación también es conocida como

IPN ESIME Culhuacan 7

Reporte Final del Proyecto SIP 20080940

modulación natural muestreada. Las señales vgs1,3 y vgs2,4 son las señales de control para

activar y desactivar los transistores impares y pares respectivamente de los transistores del

inversor mostrado en la Figura 2(c). De esta forma vRG y vYG resultan ser formas de onda

con p pulsos de voltaje de niveles ±VS/2 cuyos anchos de pulso varían con un patrón

sinusoidal a lo largo de un ciclo obteniéndose una componente fundamental de frecuencia

fS. Así mismo, el voltaje de carga, vRY contiene pulsos de ±VS modulados en su ancho de

pulso. La cuarta, quinta y sexta formas de onda de la Figura 7 muestran a vRG, vYG y vRY

obtenidas con SPWM.

La última forma de onda de la Figura 7 muestra la caracterización del k-ésimo pulso

modulado en su ancho. Este pulso tiene un periodo Δ que se calcula como p/2π=Δ , donde

p es la razón de frecuencia, p = fSW/fS, fSW es la frecuencia de conmutación (o de

“switcheo”), y δO es un cuarto del periodo, δ0 = Δ/4. αk es la posición del pulso desde el

origen del periodo fundamental hasta el centro del periodo Δ. Los ángulos δ1k y δ2k son los

ángulos modulantes que varían a lo largo de un ciclo de frecuencia fundamental y es

necesario derivar una ley de modulación para calcular los valores que pueden tomar δ1k y

δ2k.

δ1k y δ2k son calculados igualando las expresiones de vMod y vCarrier para el k-ésimo

pulso de conmutación natural, ya que vMod y vCarrier se intersectan en αk - δ1k y αk – δ2k, de tal

forma que δ1k y δ2k equivalen a:

( )( )( )( )k

kk

k

kk

MM

MM

αδαδδ

αδαδδ

cos1sin1cos1

sin1

002

001

−+

=

++

=…(6)

donde M = VM/Vcpk es el índice de modulación. Por lo tanto, los componentes armónicos de

vRG de la Figura 7 pueden ser obtenidos calculando los harmónicos producidos por k-ésimo

pulso modulado en ancho, Ak(n), y luego sumando la contribución armónica de todos los p

pulsos de vRG, es decir:

IPN ESIME Culhuacan 8

Reporte Final del Proyecto SIP 20080940

( )∫+

−

−= 02

02)( 21 δα

δα

θ θθπ

k

k

jnnk devA …(7)

donde v(θ) es el voltaje del pulso mostrado en la parte inferior de la Figura 7, de tal manera

que:

⎭⎬⎫

⎩⎨⎧ −+−= ∫ ∫∫

−

−

+

+

−+

−

−−kk

k

k

kk

jnSkk

kk

jnSjnSnk deVdeVdeVA 1

02

02

2

2

1)( 2222

1 δα

δα

δα

δα

θδα

δα

θθ θθθπ

( ){ } kjnkjnkjnSnk enjee

jnVA αδδ δ

π−− +−⎟⎟

⎠

⎞⎜⎜⎝

⎛ −⎟⎠⎞

⎜⎝⎛⎟⎠⎞

⎜⎝⎛= 0

12)( 2sin2

21

2 …(8)

La ecuación (8) no puede ser simplificada para la amplitud de los armónicos de

todos los pulsos p de un ciclo fundamental de vRG, y por lo tanto los armónicos de vRG con

SPWM, ARG(n), se calculan con:

∑=

=p

knknRG AA

1)()( …(9)

Por ejemplo, los resultados de las expresiones (6), (8) y (9) calculados para ARG(n)

con una amplitud normalizada de VS/2 usando Matlab son mostrados en la Figura 8. En esta

figura se observa que la amplitud del componente fundamental del voltaje vRG es

proporcional al índice de modulación M, existen conjuntos de armónicos en las bandas

laterales o alrededor de los múltiplos de la razón de frecuencia p, y que la amplitud de los

armónicos varía con M, pero no con la incidencia de los armónicos. Cuando p > 10 la

variación de los armónicos resultantes es mínima; sin embargo, cuando p < 10, que no es

común en la práctica, los armónicos en las bandas laterales se traslapan con los armónicos

de bajo orden y sus amplitudes son modificadas

IPN ESIME Culhuacan 9

Reporte Final del Proyecto SIP 20080940

3.7 Otras técnicas de PWM

Existen otras técnicas de modulación de ancho de pulso sinusoidal. Las más

destacas son SPWM con balance voltaje-tiempo, SPWM con portadora diente de sierra

natural muestreada y SPWM con vectores de espacio (space vector modulation). Ésta

última figura entre las más populares para el tiempo actual. Es empleada con frecuencia

para controlar inversores dedicados a la propulsión de máquinas de CA, como lo son los

motores de inducción.

3.8 Diseño del prototipo inversor de 500 W

A partir del análisis teórico descrito anteriormente, se desarrolló un inversor puente

completo de 500 W con finalidades educativas para las materias de Electrónica de Potencia

I y II, materia que es impartida en el octavo y noveno semestres de la carrera de Ingeniería

en Comunicaciones y Electrónica (ICE) de la Escuela Superior de Ingeniería Mecánica y

Eléctrica.

3.9 Descripción de prototipo

El prototipo está formado por dos etapas, una de potencia y una de control. El

diseño del prototipo fue planeado para una carga máxima de 500 W, con un suministro de

24 V y salida monofásica. A su vez, se consideró utilizar piezas electrónicas disponible en

el mercado Mexicano para que los alumnos de la carrera de ICE pudieran implementarlo.

Las secciones 4.2 y 4.3 resumen los materiales empleados para la construcción del

prototipo.

3.10 Etapa de Potencia

La etapa de potencia consiste de dos partes: la etapa de interfase y acondicionamiento

de las señales de control, y de un inversor puente completo. El circuito inversor es

IPN ESIME Culhuacan 10

Reporte Final del Proyecto SIP 20080940

mostrado en la parte superior de la Figura 9. Este circuito cuenta con dos capacitores en

serie de 2200 μF divisores del voltaje de suministro, cuyo nodo central es la referencia G

con respecto a la salida de los tótems (nodos R y Y), y un capacitor de reserva de 4700 μF.

El inversor esta formado por dos tótems, cada uno con dos MOSFETS IRF540 y dos diodos

de marcha libre ultrarrápidos MUR820, elementos capaces de ser operados a alta

frecuencia.

El circuito acondicionador de las señales de control es mostrado en la parte inferior

de la Figura 9. El acondicionamiento de las señales de control se realiza a través de un

circuito integrado TTL MC14504, el cual convierte señales de nivel TTL a nivel TTL o

CMOS (15V). Las señales de control con nivel CMOS son aplicadas posteriormente a 4

circuitos generadores de tiempo muerto. Estos circuitos generadores de tiempo muerto son

necesarios para evitar que algunos de los tótems del inversor se cortocircuiten por la

activación simultánea de ambos MOSFETs de un tótem, y son formados por compuertas

AND y NOT en combinación con un circuito RC y un diodo en antiparalelo con un

capacitor. El arreglo RC retrasa los flancos de subida de las señales de control, pero no

retrasa los flancos de bajada. El arreglo RC fue seleccionado de tal manera que se

produjera un tiempo muerto de 1μs.

Una vez acondicionadas las señales de control con un tiempo muerto, las señales

son aplicadas a dos circuitos IR2110, los cuales sirven para controlar la activación y

desactivación de los MOSFETs del inversor. Los IR2110 permiten el control de dos

MOSFETs en un tótem y, particularmente, controla la activación del MOSFET superior del

tótem por medio de un circuito de elevación por capacitor y diodo (booststrap circuit). Las

dos salidas de cada IR2110 son complementadas, de tal forma que la activación de cada

MOSFET de un tótem es alternada. Cada IR2110 genera un voltaje de compuerta a

suministro, vgs, que el aplicada a cada MOSFET por medio de un resistor de 4.7 Ohms.

3.11 Etapa de Control

La etapa de control es formada por un microcontrolador AVR ATMEGA8535. Un

programa de control fue desarrollado en este microcontrolador para generar una señal

IPN ESIME Culhuacan 11

Reporte Final del Proyecto SIP 20080940

portadora triangular de alta frecuencia (1.95 kHz) y de una señal sinusoidal modulante de

60 Hz, como fue explicado en la Sección 3.1, Figura 7. La señal portadora triangular se

genera mediante la configuración de un temporizador (timer 1) del ATMEGA8535, el cual

es preparado para operar en el modo PWM con corrección de fase y frecuencia.

La amplitud de la señal portadora es de 8 bits, con un nivel de valle de 0 y un nivel

pico de 255. El registro de referencia OCR1A del temporizador 1, es comparado con el

contador del mismo temporizador. Este registro es refrescado siempre que ocurre el evento

de la comparación, activándose una interrupción para recargar al registro de comparación

con el siguiente valor de acuerdo con una tabla de datos ordenados de forma sinusoidal.

La tabla de datos para el registro de comparación posee valores de 0 a 255

ordenados de forma sinusoidal. Esta tabla es leída de forma ascendente y

descendentemente dentro de la interrupción descrita anteriormente, de tal manera que el

registro de comparación genere una señal sinusoidal de 60 Hz y ocurra una modulación de

ancho de pulso sinusoidal.

El programa en lenguaje ensamblador realizado para el ATMEGA8535 es mostrado

en el Anexo B del presente documento.

4. Resultados experimentales

El prototipo inversor fue ensamblado en los laboratorios de electrónica de la ESIME

Culhuacan. El inversor fue alimentado con un suministro de 24 V, la interfase de control

con un suministro de 15 V y un suministro de 5 V para el microcontrolador AVR

ATMEGA8535. Se empleó un osciloscopio digital para analizar las formas de onda de

voltaje producidas por el prototipo y justificar la operación del mismo.

La Figura 10 muestra las formas de onda de control obtenidas con el AVR, vgsR y

vgsY. vgsR y vgsY son señales digitales complementadas de 1.95 kHz moduladas en ancho de

pulso, y corresponden a la secuencia de control de cada tótems R y Y. Estas señales tienen

IPN ESIME Culhuacan 12

Reporte Final del Proyecto SIP 20080940

una componente fundamental de 62 Hz, que es muy cercana a la frecuencia deseada de 60

Hz. Para comprobar experimentalmente la forma de onda de la componente fundamental,

un circuito RC aislado por medio de un diodo de RF fue conectada a una de las salidas

digitales del microcontrolador. La Figura 11 muestra una comparación de la señal vgsR y la

salida del filtro RC aislado, demostrándose que efectivamente la modulación de ancho de

pulso causa una componente sinusoidal.

La Figura 12 muestra una comparación entre la señal vgsR del microcontrolador y su

conversión a nivel CMOS obtenida en una de las salidas del circuito MC14504. Para

comprobar la operación de los circuitos de tiempo muerto se amplificó la base de tiempo

del osciloscopio para observar uno de los pulsos modulados de vgsR en nivel CMOS. La

Figura 13 muestra uno de los pulsos modulados en ancho de vgsR (CH1) junto con el voltaje

de salida del circuito de tiempo muerto, señal CH2. En este figura se puede observar como

el flanco de subida de la señal cuadrada de CH2 ha sido retrasado aproximadamente por 1

μs con respecto al flanco de subida de vgsR (CH1). Así mismo, la Figura 13 muestra el

voltaje del capacitor del circuito de tiempo muerto. El tiempo muerto de 1 μs equivale al

tiempo que tarda el capacitor en cargarse hasta 7.5 V, voltaje en el cual se efectúa la

transición de estado bajo a estado alto en las compuertas CMOS.

La operación del circuito IR2110 es justificada con las formas de onda presentadas

en la Figura 14. En esta figura CH1 corresponde a vgsR, mientras que CH2 y CH3

corresponden a vgs4 y vgs1, los voltajes de activación de los MOSFETs Q4 y Q1

respectivamente. Estas mediciones fueron repetidas para comprobar la operación del

segundo IR2110 y asegurar la activación de ambos tótems.

Para corroborar la operación adecuada del inversor puente completo, una carga

resistiva de 500 W fue conectada entre los tótems R y Y. Los voltajes vRG, vYG y vRY fueron

medidos utilizando el osciloscopio y estos son presentados en las Figuras 15, 16 y 17

respectivamente. Estas figuras demuestran la efectiva operación del inversor en modo

PWM ya que corresponden de manera similar a las formas de onda ideales de la Figura 7, a

IPN ESIME Culhuacan 13

Reporte Final del Proyecto SIP 20080940

diferencia que el índice de frecuencia p es mucho mayor que 10, es decir, prácticamente se

utilizó p = 1.95 kHz / 62 Hz = 31 .5 pulsos por ciclo fundamental.

Como prueba de veracidad del trabajo realizado en este proyecto, la Figura 18

muestra una fotografía del prototipo inversor ensamblado en el laboratorio y la Figura 19

muestra una fotografía del circuito inversor. A su vez, en el Apéndice C se presenta las

caras frontal e inferior del circuito inversor en conjunto con las mascarillas de

componentes, perforaciones y soldaduras.

5. Impacto del proyecto

El análisis, diseño y construcción de un prototipo inversor de potencia ha causado

un gran impacto en la impartición de los temas de convertidores de CD-CA en las materias

de Electrónica de Potencia 1 y 2 de la carrera de ICE de ESIME Culhuacan. El profesor de

esta materia utilizó este prototipo para demostrar prácticamente los principios básicos de

funcionamiento y operación de circuitos inversores de potencia y actualmente los alumnos

de dichas materias pueden entender teórica y experimentalmente la funcionalidad de los

circuitos inversores.

Un aspecto que vale la pena mencionar es el hecho de que los alumnos de ICE de la

especialidad de electrónica han empezado a utilizar este prototipo para controlar otro tipo

de cargas, como son motores de CD, fuentes ininterrumpibles de potencia, e inclusive para

controlar motores a pasos de diversos sistemas mecatrónicos.

6. Conclusiones

En conclusión, el presente documento reportó el análisis, diseño, construcción y

experimentación de un inversor de potencia de 500 W con modulación PWM sinusoidal

para fines educativos. Se explicó detalladamente cual es el principio de operación de un

inversor puente completo con PWM sinusoidal. A su vez, se describió los materiales y

IPN ESIME Culhuacan 14

Reporte Final del Proyecto SIP 20080940

métodos empleados para construir un prototipo inversor de 500 W y se mostraron

resultados experimentales con el mismo.

En lo que respecta a la aplicación del prototipo, el sector educativo es el principal

usuario. Lo anterior se demuestra con el uso actual del prototipo para apoyarse en la

impartición de la currícula de las materias de Electrónica de Potencia 1 y 2 de la carrera de

ICE.

7. Referencias

[1] Forsyth, A. J. (2000) “Introduction to Power Electronic Converters, AC-DC

converters””, Module EE5A2. Handout for MSc course in Power Electronics and

Drives Program, School of Electrical and Electronic Engineering, The University of

Birmingham. United Kingdom.

[2] Mohan, Ned (1995) “Power Electronics: Converters, applications and design”, Second

Edition, New York, John Wiley & Sons.

[3] Rashid, Muhammad H. (1995) “Electrónica de Potencia, Circuitos Dispositivos y

Aplicaciones”, Segunda Edición, México, Prentice-Hall Hispanoamericana S.A. de

C.V.

[4] Araujo-Vargas, Ismael (2000) “Inversor de Voltaje para Carga Máxima de 50 Watts

Controlado por Microcontrolador AVR AT90S1200”, Tesis de Licenciatura presentada

en la Escuela Superior de Ingeniería Mecánica y Eléctrica Unidad Culhuacan. México

D.F.

[5] Franco, Sergio (1988), “Design with Operational Amplifiers and Analog Integrated

Circuits” First Edition, New York, McGraw-Hill International Book Company.

[6] International Rectifier, http://www.irf.com

[7] Erickson, R.W. (2001) “Fundamentals of Power Electronics”, Second Edition, Boulder

Coloado, Kluwer Academic Publishers.

IPN ESIME Culhuacan 15

Reporte Final del Proyecto SIP 20080940

8. Apéndice A. Figuras

(ver anexo)

(Las figuras se quitaron y se colocaron en un archivo anexo para que el archivo fuera menor

de 700 kB.)

IPN ESIME Culhuacan 16

Reporte Final del Proyecto SIP 20080940

9. Apéndice B. Programa ensamblador para el ATMEGA8535

;***** probando timer en PWM con modulación sinusoidal con el ATMEGA8535, última

versión con interrupción

.include "M8535DEF.inc"

.def refer =r0 ;registro de referencia para PWM

.def refer2 =r16

.def temp =r17 ;registro temporal

;usando theta como r30 y r31 que son ZL y ZH respectivamente

.def delta =r20 ;registro para delta baja

.def deltaH =r21 :registro para delta alta

;bande

.equ SLOPE =1

.equ CICLO =0

;inicio

.cseg

.org 0x000

INICIO: rjmp RESET ;salto a subrutina para reset

.org 0x006

rjmp TIM1_COMPA ;salto a subrutina para compare match T1A

;dejando espacio para futuras interrupciones

IPN ESIME Culhuacan 29

Reporte Final del Proyecto SIP 20080940

.org 0x011

RESET: ;SUBRUTINA PARA RESET

ldi temp,low(RAMEND) ;stack pointer hasta el final de Ram para

permitir subrutinas e interrupciones.

out SPL,temp

ldi temp,high(RAMEND)

out SPH,temp

ldi ZL,0x00 ;parte baja de Z con theta inicial

ldi ZH,0x02 ;parte alta de Z, pero recordando que 0x0100

equivale a

;la direccion para 16bits y 0x0200 a la dirección en

8bits

lpm ;cargando referecia con primer valor de la tabla de

seno

ser temp ;temp a FFh

out DDRD,temp ;configurando D como salida

out DDRA,temp

ldi delta,0x11 ;delta a 61decimal

ldi deltaH,0x00 ;delta alta con 0x00

out OCR1AL,refer ;mandando referencia a registro comparador

1A

ldi temp,0x00

out OCR1AH,temp

ldi temp,(1<<OCIE1A) ;cargando temporal con comp match 1A para

interrup

out TIMSK,temp ;cargando TIMSK con temp

ldi temp,0x00

out TCNT1H,temp ;cargando contador 1 con 0x0000

out TCNT1L,temp

IPN ESIME Culhuacan 30

Reporte Final del Proyecto SIP 20080940

ldi temp,(1<<PWM10)|(1<<COM1A1) ;configurando TCCR1A para

PWM 8b non-inverted

out TCCR1A,temp

ldi temp,(1<<CS10) ;(1<<CS11)|(1<<CS10)

configurando prescaler de timer 1 a ck/1

out TCCR1B,temp

sei ;activando bit de interrupción global

rjmp MAIN

MAIN: ;inc refer2

;out PORTA,refer2

rjmp MAIN

TIM1_COMPA: ;ser temp

;out TIFR,temp

add ZL,delta

adc ZH,deltaH

;comparación de 16 bits

cpi ZL,low(0x0200+3999) ;comparando parte baja del maximo de

la tabla con theta

ldi temp,high(0x0200+3999) ;cargando valor inmediato alto

cpc ZH,temp ;comparando parte alta inmediata con

ZH

brlo SALIDA ;salta si es menor

MAYOR: subi ZL,low(3999) ;si no es menor, resta 3999 localidades

al apuntador Z

subi ZH,high(3999)

SALIDA: lpm

out OCR1AL,refer ;mandando referencia a registro comparador

1A

;out PORTA,ZL

IPN ESIME Culhuacan 31

Reporte Final del Proyecto SIP 20080940

reti

.org 0x100

TABLA:

.include "sintab.txt" ;tabla de 4000 valores de seno

IPN ESIME Culhuacan 32

Reporte Final del Proyecto SIP 20080940

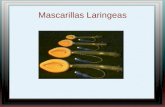

10. Apéndice C. Circuito impreso y mascarillas del prototipo inversor

IPN ESIME Culhuacan 33