Organización del Computador I · Organización del Computador I Federico Yulita Segundo...

Transcript of Organización del Computador I · Organización del Computador I Federico Yulita Segundo...

-

Organización del Computador IFederico Yulita

Segundo Cuatrimestre, 2020

Esta materia la estoy cursando con Carlos López Pombo como docente de las clases teóricas, con María ElenaBuemi como JTP, con Daniel Foguelman y Gustavo Hurovich como Ayudantes de Primera y con Leticia Rodríguez,Hernán Gagliardi y Augusto González Omahen como Ayudantes de Segunda. Si querés ver el resto de mis apunteslos podés encontrar en mi blog.

Índice1. Evolución Histórica de la Computadora 3

2. El Modelo de von Neumann-Turing 42.1. Jerarquía de Máquina . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3. Sistemas de Numeración 7

4. Lógica Digital 94.1. Álgebra de Boole . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94.2. Puertas Lógicas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94.3. Circuitos Secuenciales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5. Instruction Set Architecture 125.1. Subrutinas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175.2. Modos de Direccionamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6. Unidad de Control y Microprogramación 18

7. Entrada y Salida 287.1. Control de Dispositivos e Interrupciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287.2. Conversión de Señales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8. Memoria 358.1. Tipos de Memoria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358.2. Memoria Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9. Buses 399.1. Diseños y Protocolos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 399.2. Ejemplos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

1

http://materias.df.uba.ar/rga2020c2/https://elrepositoriodefede.wordpress.com/

-

John von Neumann (1903 - 1957)

2

-

1. Evolución Histórica de la ComputadoraDefinimos una Computadora como una máquina digital electrónica programable para el tratamiento auto-

mático de la información, capaz de recibirla, operar sobre ella mediante procesos determinados y suministrar losresultados de tales operaciones. Se dice que algo es Digital si su operación se basa en la utilización de valores discre-tos en contraposición al uso del espectro continuo de valores (Analógico). Un dispositivo se lo llama Electrónicosi resulta de la organización de componentes en circuitos con el objetivo de controlar y usar señales eléctricas.Ejemplos modernos de computadoras son nuestras laptops, PCs, celulares, tablets y también calculadoras y otrosdispositivos smart. En esta materia vamos a estudiar la arquitectura y la organización de computadoras. La Arqui-tectura consiste de todos los elementos que son visibles al programador: el conjunto de registro, de instrucciones,la representación de datos, los mecanismos de direccionamiento de memoria, el acceso a dispositivos de entrada yde salida, etc.. La arquitectura se encarga de describir el diseño de una computadora. La Organización se refierea cómo se implementa la arquitectura en un sistema físico: las señales de control, la tecnología de la memoria, lasinstrucciones ejecutadas por el hardware o las interpretadas por microprogramas, la implementación de operacionescomo suma y multiplicación, etc.. La organización se encarga de describir cómo funciona una computadora. Porejemplo, toda la familia de procesadores x86 de Intel comparten la misma arquitectura, ya que aseguran backwards-compatibility - es decir - se pueden ejecutar cualquier programa diseñado para esta arquitectura sin importar quetan viejo sea (DOS con un Intel Core i7). Sin embargo, para cada procesador la organización es distinta, ya queesto es lo que permite que haya mejora e innovación en cada nuevo procesador. Esta distinción entre arquitecturay organización no siempre es clara, ya que a veces ambas se condicionan entre sí.

Es imposible determinar con exactitud dónde terminan los problemas de hardware y empiezan los problemas desoftware ya que todo en la computación está armado a través de estándares y algoritmos. Cualquier programa queusemos está descrito a través de algoritmos mediante algún lenguaje de programación que, a su vez, está descritomediante otros algoritmos. Las computadoras son implementaciones de algoritmos que corren otros algoritmos. Deaquí se forma el Principio de Equivalencia entre Hardware y Software, que establece que cualquier cómputoque puede ser realizado por intervención de una pieza de software puede ser realizado por un artefacto de hardwarey viceversa.

Al nivel más básico existen tres componentes principales de toda computadora:

1. Un procesador que interprete y ejecute programas.

2. Una memoria para guardar datos y programas.

3. Un mecanismo de transferencia de los datos desde y hacia el mundo exterior.

Esta forma de ver una computadora es lo que se llama la Visión Funcional de una computadora. Sin embargo,existe la Visión Estructural que se fija en la forma en que las componentes se relacionan entre sí para llevar acabo alguna tarea. En la Figura 1 puede verse una imagen de la visión estructural de una computadora.

La evolución histórica de la computadora se divide de forma general en cinco generaciones. Para esta parterecomiendo ver las dispositivas de la primera clase teórica ya que tiene muchos ejemplos con fotos y demás que novale la pena que transcriba a este documento.

Generación 0 (hasta el 1945) Esta generación consiste de computadoras mecánicas o electromecánicas. Algunosejemplos de computadoras de esta generación son el ábaco, las máquinas de Babbage (1920), y sistemas basados enrelays como la Harvard Mark I. Algunas figuras importantes de esta generación son Charles Babbage (padre de lacomputación) y Ada Lovelace (madre de la computación, la primera programadora).

Generación 1 (1945 - 1954) Esta generación consiste de computadoras que utilizan válvulas de vacío o tableroscon conectores. Una Válvula de Vacío es un dispositivo que consiste de un ćatodo y un ánodo que usa el fenómenode emisión termoiónica de electrones desde un ćatodo caliente para controlar la corriente. En 1904 John AmbroseFleming usó una válvula de vacío para crear un diodo. Luego en 1906 Lee de Forest la usó para crear un triodo, quelogró reemplazar los relays como una opción mas duradera. Algunos ejemplos de computadoras de esta generaciónson la Atanossof Berry (1942), la Colossus (1945), la Enigma (1945), la ENIAC (1946). Algunas figuras importantesde esta generación son John von Neumann y Alan Turing. Además, von Neumann formó lo que se conoce como laarquitectura de von Neumann a partir de la cual se construyeron algunas máquinas como la ENIAC. Alan Turing

3

-

Figura 1: Visión estructural de una computadora.

creó el concepto de Máquinas de Turing, que fue implementada (junto con la arquitectura de von Neumann) en laManchester Mark I, la IAS y la UNIVAC.

Generación 2 (1955 - 1965) Esta generación consiste de computadoras que utilizan transistores y hace cómputopor lotes. El Transistor es un dispositivo eléctrico que usa semiconductores para realizar el mismo trabajo que unaválvula de vacío pero de forma más eficiente. Los transistores permitieron la Microprogramación, que consisteen generar una abstracción de combinaciones de señales que llevan a cabo tareas como lectura de instruccionesdesde la memoria, decodificación de instrucciones usando la ALU (Arithmetic Logic Unit), lectura de datos desdela memoria, escritura en la memoria, etc.. Estos microprogramas son una abstracción del sistema físico que son lasseñales, pero no se considera software porque se trata de la manipulación de señales mientras que los programasson más abstractos aún. Los microprogramas son propios a la organización del computador. En 1957 nace el primercompilador de Fortran para la IBM 704. El Compilador es un programa que traduce del lenguaje de programaciónque nosotros podemos entender a lenguaje de máquina. Luego en 1959 surgen los Mainframes que son ...

Generación 3 (1966 - 1980) Esta generación consiste de computadoras que tienen circuitos integrados (o chips)y programas almacenados. Estas computadoras permiten la Multiprogramación que consisten en administrarmúltiples programas para que se ejecuten uno detrás del otro de manera automática. En 1968 se funda Intel y en1972 papi Dennis Ritchie crea C.

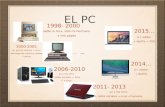

Generación 4 (desde el 1980) Esta generación consiste del surgimiento de las computadoras personales (PCs) ylas primeras empresas para este mercado cono Microsoft y Apple. En 1982 surge la querida Commodore 64. La Leyde Moore establece que la cantidad de transistores por chip se duplican por año y la Ley de Rock que el costode equipamiento de necesario para construir semiconductores se duplica cada cuatro años.

2. El Modelo de von Neumann-TuringEn 1928, David Hilbert presentó un programa con los objetivos de la matemática para los próximos años en el

Congreso Internacional de Matemáticos. Su programa consistía de cinco puntos principales:

1. Formalizar la matemática: Toda proposición debe ser escrita en un lenguaje formal y manipulada porreglas bien definidas.

2. Completitud: Este formalismo debe permitir demostrar toda proposición verdadera.

4

-

3. Consistencia: Este formalismo no puede permitir demostrar una proposición falsa.

4. Conservación: Cualquier resultado sobre “objetos reales” obtenido a partir de razonar sobre “objetos ideales”puede ser demostrado sin recurrir a “objetos reales”.

5. Decidibilidad: Debe exisitir un algoritmo que determine la verdad o falsedad de toda proposición del lenguaje.

Sin embargo, en 1931 Gödel publicó un paper llamado “Über formal unentscheidbare Sätze der Principia Mathema-tica und verwandster Systeme” donde demuestra su Teorema de Incompletitud que establece que para todo sistemaaxiomático formal existen proposiciones verdaderas que no pueden ser demostradas bajo dicho sistema. Es decir, lamatemática no está completa. Luego en 1936 Alonzo Church crea el cálculo de lambda y muestra que no existe unasolución general para el problema de la decisión. Independientemente ese mismo año Alan Turing publica un paperllamado “On computable numbers, with an application to the Entscheidungsproblem” donde conceptualiza lo que sellama una “Máquina de Turing” y demuestra que efectivamente existen algoritmos que no pueden ser determina-dos verdaderos o falsos (Halting Problem). Una Máquina de Turing modela matemáticamente un mecanismo demanipulación de símbolos. Esta cuenta con:

Cinta: Una secuencia infinita de celdas capaces de contener (o no) un símbolo.

Cabeza: Un dispositivo que puede leer el contenido de una celda o escribir uno nuevo. Esta cabeza puedemoverse hacia la izquierda o hacia la derecha hacia la celda contigua.

Registro de Estado: Un registro que guarda el estado actual de la máquina, puediendo tener un conjuntofinito de distintos posibles estados.

Tabla de Instrucciones: Una tabla que dado el estado actual y el contenido de la celda donde esté la cabezapueda cambiar (o no) el contenido de la celda, moverse hacia la izquierda o derecha y cambiar de estado.

Cualquier sistema que pueda simular una máquina de Turing se la llama Turing Completo.La idea de von Neumann sobre las computadoras es que debían ser capaces de tener una memoria donde

almacenaran programas que puedan ser ejecutados. El modelo de von Neumann-Turing consiste en los siguientespuntos:

Los programas y los datos se almacenan en la misma memoria sobre la que se puede leer y escribir.

La operación de la máquina depende del estado de la memoria.

El contenido de la memoria es accedido a través de su posición.

La ejecución es secuencial a menos que se indique lo contrario.

La arquitectura de von Neumann consiste de tres componentes principales:

CPU: (Central Processing Unit) Unidad de procesado de datos.

Memoria: Unidad capaz de almacenar información en sistema binario.

Sistema de Entrada y Salida: Unidad capaz de lidiar con las instrucciones que el usuario le dé a la máquinay con los resultados que esta devuelva.

Dentro del CPU existen otras tres componentes principales:

Unidad de Control: Se conecta a la memoria mediante un único camino. Coordina la labor de los compo-nentes de forma que las instrucciones y los datos puedan ser transgferidos entre la memoria y los registros.Además, decodifica instrucciones de los programas y las transforma en órdenes a los componentes. Esta unidadpuede ser implementada en hardware o puede ser microprogramada. La unicidad del camino con la memoriafuerza a la alternación entre ciclos de lectura y de escritura, lo que se conoce como Cuello de Botella devon Neumann.

ALU: (Arithmetic-Logic Unit) Se encarga de realizar las operaciones matemáticas y lógicas entre los datos.También, en caso de direccionamientos complejos, se encarga de calcular los desplazamientos de memoria.

5

-

Figura 2: Esquema de la arquitectura de von Neumann.

Registros: Pequeñas unidades de memoria de acceso rápido.

En la Figura 2 puede verse un esquema de la arquitectura de von Neumann. Entonces, para funcionar la arquitecturade von Neumann requiere de Ciclos de Instrucción. Estos ciclos constan también de tres partes:

Fetch: Se obtiene una instrucción de la memoria. La ubicación de esta instrucción en la memoria está deter-minada por un contador. Entonces, la ALU luego se encarga de incrementar este contador para reiniciar elciclo con la siguiente instrucción.

Decode: La instrucción obtenida se decodifica en señales que luego se almacenan en registros.

Execute: Luego de haber decodificado la instrucción se ejecutan las operaciones en los registros y se guardael resultado de vuelta en la memoria.

2.1. Jerarquía de MáquinaUna computadora se puede dividir en siete niveles de abstracción. Cada nivel funciona como una máquina

abstracta que oculta la capa anterior y es capaz de resolver distintos tipos de problemas. La capa anterior se utilizacomo servicio.

Nivel 0 Este es el nivel más bajo de la jerarquía. Consiste de circuitos, compuertas lógicas y manipulación explícitade bits. Es el nivel más bajo ya que lidia explícitamente con el sistema físico que es la computadora.

Nivel 1 Este nivel consiste de la unidad de control y del microcódigo, ya que utiliza el hardware a través de ciclosde instrucciones para ejecutar programas.

Nivel 2 Este nivel consiste de lo que se llama “Lenguaje de Máquina” e ISA (Instruction Set Architecture). ElLenguaje de Máquina consiste en la interpretación y manipulación de cadenas de bits como instrucciones quepueden ser comprendidas por la unidad de control. Estas instrucciones son específicas a la arquitectura de la máquinaya que asume la existencia de registros, señales, etc.. Además, este lenguaje no necesita ser compilado ni ensambladoy puede ser almacenado en la memoria y ejecutado diractamente.

Nivel 3 Este nivel consiste del software del sistema, de las bibliotecas y el sistema operativo. Este nivel proporcionala estructura sobre la cual procesos pueden ser ejecutados y brinda servicios de acceso a dispositivos de entrada yde salida.

6

-

Nivel 4 Este nivel consiste del Lenguaje de Ensamblado. Este es un lenguaje de programación muy cercano ala arquitectura de la computadora que es producido por compiladores con el objetivo de traducir otros lenguajesde programación al lenguaje de máquina.

Nivel 5 Este nivel consiste de los lenguajes de programación de alto nivel, como C++, Python, Javascript, etc..Estos lenguajes permiten la programación de software de propósito general.

Nivel 6 Este es el nivel más alto de la jerarquía y consiste de los programas ejecutables. El usuario ejecutaprogramas con cierta finalidad y la máquina le provee una interfaz con la que el usuario puede usarla.

3. Sistemas de NumeraciónLlamamos un Bit a la mínima unidad de información que es un dígito binario (binary digit). Llamamos un

Byte a 8 bits. Entonces, para poder representar números que una máquina puede interpretar debemos definir unsistema de numeración capaz de esto. Ya que la mínima unidad de información es un dígito binario entonces vamosa usar el sistema binario para representar magnitudes. Consideramos:

(an . . . a1a0.a−1 . . . a−m)b = anbn + · · ·+ a1b + a0 + a−1b−1 + · · ·+ a−mb−m

Estos sistemas se llaman Sistemas Posicionales. Llamamos b la Base del sistema y llamamos al punto que apareceentre a0 y a−1 el Punto Fraccionario. Entonces, el Sistema Decimal es el sistema de base b = 10 (con dígitos 0,1, 2, 3, 4, 5, 6, 7, 8 y 9) y el Sistema Binario es el de base b = 2 (con dígitos 0 y 1). También, existen el SistemaOctal de base b = 8 (con dígitos 0, 1, 2, 3, 4, 5, 6, y 7) y el Sistema Hexadecimal de base b = 16 (con dígitos 0,1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E y F). Obviamente hay infinitas bases posibles, pero estas cuatro son las máscomunes que se usan en distintos contextos. Matemáticamente n y m pueden ser arbitrariamente grandes pero pararepresentar números en una computadora va a ser necesario fijar estos valores a conveniencia. Algunos ejemplos denúmeros en estos sistemas son:

(1)10 = (1)2 = (1)8 = (1)16(20)10 = (10100)2 = (24)8 = (14)16(307)10 = (100110011)2 = (463)8 = (133)16(44.5)10 = (101100.1)2 = (54.4)8 = (2C.8)16

Ahora, para representar números con signo lo que podemos hacer es usar el dígito más a la izquierda: si es 0 elnúmero es positivo y si es 1 es negativo. Sin embargo, notemos que con este sistema existen dos representacionesdel número 0: +0 y −0.

Consideremos la operación suma. Consideremos la suma de dos números de tres dígitos: 358 y 823:

13 5 8

+ 8 2 31 1 8 1

Notemos que esta suma devuelve un número que es de cuatro dígitos, un dígito más que los tres que teníamos. Estenuevo dígito necesario para el resultado de la suma se lo llama Overflow. Esto puede ser un problema, ya querecordemos que el n es una cantidad acotada que representa la cantidad de dígitos que la computadora usa pararepresentar un número. En este caso si n = 3 entonces este nuevo número, resultado de la suma de otros dos queestaban correctamente representados, no puede ser representado por esta computadora. Otra situación en la que seencuentra esta limitación en la representación de números es en los números fraccionarios con infinitos dígitos. Paraestos números simplemente se redondean hasta donde dé la capacidad de representación de la computadora. Parael overflow se tiene un dígito especial en el procesador que vale 0 cuando no hay overflow y 1 cuando hay. De estamanera se puede registrar cuando hay un overflow.

Para representar números negativos lo que se hace es restar el complemento del número más grande posible.Esto se llama el Sistema de Complemento, ya que dado un número n y el número más grande posible bk − 1

7

-

entonces el complemento de n es −n = bk − 1− n. Este máximo número va a ser propio del diseño del procesador.Veamos algunos ejemplos considerando solo tres dígitos:

(−1)10 = (998)10(−52)10 = (947)10(−499)10 = (500)10(−0)10 = (999)10

En este sistema también existen dos maneras de representar el número 0: 0 y bk − 1.Notemos que entonces para hacer cualquier operación matemática necesitamos solo dos circuitos: uno que permita

sumar y otro que permita complementar. Notemos que para hacer una resta basta con hacer una suma con el segundonúmero complementado:

(167)10 − (52)10 = (167)10 + (947)10= (1114)10

Notemos que en este caso hay overflow. Sin embargo, para obtener el resultado correcto de la resta debemosAcarrear este dígito - es decir - lo sacamos de enfrente y lo sumamos al número que queda:

(167)10 − (52)10 = (114)10 + (1)10= (115)10

Este es el algoritmo de resta: se suma un número con su complemento y se acarrea. Sin embargo, notemos que elcomplemento como le venimos representando hasta ahora en base 10 implica una resta. Esto no nos sirve, ya quejustamente queremos evitar tener que diseñar un circuito que reste. Sin embargo, el complemento en base binariaes mucho más simple ya que simplemente hay que invertir los dígitos. Veamos un ejemplo:

(−101)2 = (1111)2 − (0101)2= (1010)2

Notemos que 1010 es igual al 0101 pero con los dígitos invertidos (0s por 1s y 1s por 0s). Esto se puede hacer conun circuito muy fácilmente.

Sin embargo, lo que vamos a hacer es usar el menor número no representable en vez del mayor número represen-table. Esto nos va a dejar un rango de números de

[−2n−1, 2n−1 − 1

]. De esta forma se rompe la simetría del rango

pero nos deja una sola posible representación para el número 0, ya que el −0 ya no existe porque nos da un númerono representable. El problema es que ahora el complemento se nos complica levemente. Lo que hay que hacer ahoraes invertir cada dígito y sumar 1. Entonces ahora (−0101)2 = (1011)2.

Para multiplicar números es bastante simple, ya que hay que hacerlo como lo hacíamos en la primaria:

1 0 0 1× 1 1 0 1

1 0 0 1+ 0 0 0 0 −

+ 1 0 0 1 − −+ 1 0 0 1 − − −

1 1 1 0 1 0 1

Básicamente se va multiplicando por cada dígito del segundo número y se va agregando un 0 (o una raya como lorepresenté yo) cada vez que avanzamos un dígito. Al final hay que sumar todo. Ya que los números son siempre 0sy 1s las multiplicaciones y las sumas son bastantes fáciles.

8

-

4. Lógica Digital4.1. Álgebra de Boole

Necesitamos representar la información de alguna forma en circuitos. Ya mencionamos que vamos a trabajar ensistema binario con bits, que son la mínima unidad de información. Entonces vamos a usar el esquema CMOS, queinterpreta un voltaje entre 0VDD y 13VDD, donde VDD es el voltaje de alimentación, como un 0 y voltajes entre23VDD y 1VDD como un 1. Ya que este sistema tiene dos posibles valores entonces podemos interpretar un 1 comoun verdadero y un 0 como un falso, lo cual nos posibilita el uso de operaciones lógicas al sistema. En particular,podemos usar el Álgebra de Boole que modela matemáticamente el razonamiento proposicional. Si X e Y sonelementos binarios del álgebra de Boole entonces representamos X + Y como el operador análogo al operador lógico∨, X · Y como el operador análogo al operador lógico ∧ y X̄ como el operador análogo al operador lógico ¬. Lasoperaciones básicas del álgebra de Boole son:

X Y X̄ X + Y X · Y0 0 1 0 00 1 1 1 01 0 0 1 01 1 0 1 1

Veamos algunas propiedades de este álgebra:

Identidad: 1 ·X = X ∧ 0 + X = X.

Neutro: 0 ·X = 0 ∧ 1 + X = 1.

Idempotencia: X ·X = X ∧X + X = X.

Inversa: X · X̄ = 0 ∧X + X̄ = 1.

Conmutatividad: X · Y = Y ·X ∧X + Y = Y + X.

Distributividad: X + (Y · Z) = (X + Y ) · (X + Z) ∧ (X + Y ) · Z = X · Z + Y · Z.

Asociatividad: (X · Y ) · Z = X · (Y · Z) ∧ (X + Y ) + Z = X + (Y + Z).

Absorción: X · (X + Y ) = X.

De-Morgan: ¯X · Y = X̄ + Ȳ .

Llamamos la Forma Conjuntiva Normal como la forma de expresar una función del álgebra de Boole a travésde la conjunción de disyunciones, es decir, productos de sumas. Por ejemplo:

f (X, Y, Z) = (X + Y ) · (X + Z) · (X + Y + Z)

Llamamos la Forma Disyuntiva Normal como la forma de expresar una función del álgebra de Boole a travésde la disyunción de conjunciones, es decir, suma de productos. Por ejemplo:

f (X, Y, Z) = X · Z + Y · Z

4.2. Puertas LógicasPara representar estas operaciones del álgebra de Boole físicamente se usan Puertas Lógicas. Estas puertas

lógicas son dispositivos electrónicos que se arman usando transistores. Un Transistor es, a su vez, un dispositivoelectrónico que funciona usando semiconductores para controlar el flujo de corriente a través del circuito. En laFigura 3 puede verse un dibujo de un transistor real y el diagrama circuital de un transistor. Como se puede ver enla figura hay tres partes principales en un transistor: el colector, la base y el emisor. Si se tiene un voltaje mayor alcrítico en la base entonces el transistor permite el flujo de corriente del colector al emisor. De esta forma, se puedenarmar las compuertas lógicas que representen las operaciones booleanas. Para evitar cortocircuitos se puede usar un

9

-

Figura 3: Un transistor.

Figura 4: Buffer de tres estados.

Figura 5: Semi-sumador.

10

-

Figura 6: Sumador.

Buffer de Tres Estados (Three-State Buffer) que actúa como switch en el circuito. En la Figura 4 puede verseel diagrama circuital de este componente y el análogo que forma al switch. Usando estas componentes eléctricasuno pude armar circuitos que hagan las operaciones matemáticas y lógicas que queramos.

En la Figura 5 podemos ver el diagrama circuital de un Semi-Sumador. Dadas dos entradas A y B, Srepresenta la suma de ambas entradas y C representa el acarreo de la suma. En la Figura 6 puede verse el diagramacircuital de un Sumador. Este sumador toma tres entradas: A, B y un acarreo Cin. Entonces, este sumador devuelvela suma A + B junto con un acarreo Cout pero a diferencia del semi-sumador tiene otra entrada que es Cin queconsidera si hubo un acarreo previamente. Otro circuito importante es el Decodificador. Este circuito tiene nentradas y 2n salidas. Cada salida representa una única combinación de valores en las entradas. De esta forma,sabiendo los valores de salida podemos decodificar cuáles son los valores de entrada. En la Figura 7 puede verseel diagrama circuital de un decodificado 2-a-4. Un Codificador hace el trabajo inverso. Luego un Multiplexor esun circuito que selecciona una de n entradas a partir de log2 (n) líneas de control. El Demultiplexor es un circuitoque hace lo opuesto. El multiplexor es útil para implementar funciones booleanas. En la Figura 8 puede verse unaALU que toma entradas de 1bit y puede sumar las entradas o hacer operaciones lógicas entre ellas.

4.3. Circuitos SecuencialesEl objetivo de losCircuitos Secuenciales va a ser lograr almacenar información en lo que llamaremos memoria.

Los Flip-Flops son circuitos secuenciales que permiten guardar el estado de un bit, es decir, guardar un valor.Estos flip-flops van a servir para construir memorias. El nombre proviene del hecho que guardan un valor hasta quese lo cambia por otro. En la Figura 9 puede verse un Flip-Flop RS (Reset-Set) que es el más simple ejemplo deun flip-flop. La tabla de verdad de este circuito es:

S R Q (t) Q (t + dt)0 0 0 00 0 1 10 1 0 00 1 1 01 0 0 11 0 1 11 1 0 Indefinido1 1 1 Indefinido

Notemos que cuando R = S = 0 el circuito almacena el estado de Q y cuando R = S = 1 el circuito está en unestado indefinido, ya que Q = Q̄ = 0. El nombre Reset-Set viene de que si R = 1 y S = 0 entonces el circuito seresetea a 0 y si R = 0 y S = 1 entonces el circuito se setea a 1.

11

-

A 2-to-4 line single bit decoder Truth Table

Minterm Equations

Figura 7: Decodificador.

En estos circuitos secuenciales se suele usar una compuerta AND como Habilitación de Datos. Esto nospermite controlar cuándo queremos leer y grabar la información almacenada, ya que una de las entradas de lacompuerta es la de control (notada como enable). Entonces, lo que podemos hacer es cambiar los NORs del circuitoa ANDs con las entradas negadas y usar dos ANDs para habilitación de datos como se ve en la Figura 9. Entonces,podemos mandar una señal oscilante de ceros y unos a cierta frecuencia por el enable para establecer periodos deescritura y de lectura. Cuando el enable (de ahora en más clock) está en 1 entonces podemos escribir en la memoriay cuando está en 0 solo podemos leer la memoria.

Otro flip-flop es el Flip-Flop D. Este circuito toma una sola entrada (sin contar el clock) y almacena el valorde entrada. Con este flip-flop podemos armar un Registro de Memoria encadenando estos flip-flops. Es necesarionegar el clock al pasar de un flip-flop a otro para alternar los estados de lectura y escritura y asegurarse de que elvalor de uno se transfiera al otro sin sobreescribirse durante el mismo ciclo de escritura. Es decir, nos asegura quela velocidad de propagación de la señal sea menor que la del ciclo.

Con todo esto podemos armar una Celda de Memoria como se ve en la Figura 11. in es el circuito de entrada,out el de salida, Clk es el clock, select es una señal que habilita los datos de entrada y salida (habilita la celda) yR/W es una señal que determina si el siguiente ciclo de reloj es de escritura o de lectura. En la Figura 12 puedeverse el circuito de una memoria de 4 palabras de 3 bits. Cada BC es una celda de memoria. El decodificador nosasigna una palabra en base a las dos entradas, que son la dirección de memoria a la que queremos acceder.

5. Instruction Set ArchitectureLa ISA (Instruction Set Architecture) es el conjunto de instrucciones que definen la arquitectura del computador.

Haciendo referencia a los niveles de jerarquía, la ISA vive en el nivel 2 de jerarquía. Estas instrucciones que definenla ISA son utilizadas por un programador de bajo nivel para utilizar las componentes que construímos en el capítuloanterior. La ISA es el límite entre el hardware y el software y utiliza la organización para definir la arquitectura delsistema.

Existen elecciones que se deben tomar al definir la ISA. Una de las elecciones a tomar es la complejidad delconjunto de instrucciones. A mayor cantidad de instrucciones el rendimiento es peor, ya que hay más instrucciones

12

-

Figura 8: ALU de 1-bit.

13

-

Figura 9: Flip-Flop RS (Reset-Set).

Figura 10: Flip-Flop RS con habilitación de datos.

Figura 11: Celda de Memoria.

14

-

Figura 12: Memoria de 4 palabras de 3 bits.

que decodificar, pero la programación es más simple, ya que hay más instrucciones disponibles. Esto se llamaComplex Instruction Set Computer, o CISC. Es lo opueto a Reduced Instruction Set Computer, o RISC.Otras elecciones a tomar es si la longitud de las instrucciones es fija o variable, la cantidad de memoria utilizadapor un programa, los tipos de datos disponibles y sus representaciones, Big Endian vs. Little Endian, etc. En estamateria vamos a ver tres arquitecturas distintas:

1. Stack Architecture: Se cuenta con una pila y las operaciones se realizan sobre los elementos almacenadosen ella accesibles desde el tope.

2. Accumulator: Se cuenta con un registro distinguido y las operaciones tienen como operando implícito dichoregistro. De ser necesario otro operando se proporciona su dirección en la memoria y el resultado se coloca enel acumulador.

3. General Purpose Registers: Se cuenta con un banco de registros y las operaciones se realizan entre ellosasí que todos los operandos, y el destino del resultado, son explícitos.

Accumulator (MARIE) MARIE (Machine Architecture that is Really Intuitive and Easy) es un ejemplo dearquitectura accumulator. Puede verse un esquema de esta arquitectura en la Figura 13. Usa representaciónbinaria de complemento a 2, memoria de 4K accedida por palabras de 16 bits, instrucciones de tamaño fijo de 16bits (4 para el código y 12 para las direcciones), una ALU de 16 bits y 7 registros para control y movimiento dedatos.

General Purpose Architecture Esta arquitectura usa representación binaria en complemento a 2, memoria de 64Kaccedida por palabras de 16 bits, instrucciones de tamaño variable de 16, 32 o 48 bits dependiendo de si es de 0, 1o 2 operandos (4 para el código de operación y 12 para el operando 1, 16 para el operando 2 y 16 para el operando3), una ALU de 16 bits y 11 registros, 8 para uso general (R0 - R7) y 3 para control (PC, SP y Flags).

15

-

Figura 13: MARIE.

Figura 14: Stack Architecture.

16

-

Stack Architecture Esta arquitectura fue creada por Jan Łukasiewicz, un matemático y filósofo polaco. Él inventóla notación polaca inversa, que usa otro orden para las operaciones. Por ejemplo, la suma se escribe como XY +, oX · (Y + Z) se escribe como XY Z + ·. Está bueno porque no requiere paréntesis para eliminar ambigüedad. Las dosoperaciones principales de esta arquitectura es Push y Pop. Push permite colocar un dato en la primera posiciónlibre y Pop permite retirar el último dato que se encuentra en la pila. En la Figura 14 puede verse un esquema deesta arquitectura.

5.1. SubrutinasUna Subrutina es una construcción que permite reutilizar código a partir de la modularización de fragmentos

que son invocados y ejecutados para luego retornar a la ejecución del programa que lo invocó. Los sistemas operativosorganizan la memoria como una pila que posibilita la invocación de subrutinas, preservado la información delprograma que la invocó para que la ejecución pueda retornar a la instrucción siguiente a dicha invocación.

5.2. Modos de DireccionamientoVamos a definir 6 básicos modos de direccionamiento con los cuales vamos a acceder a distintas direcciones de

memoria. El acceso a memoria se hace mediante un código del formato:

|OpCode|Op1|Op2|Op3|

Cada una de las partes entre barras consiste de instrucciones de 16 bits. La primera nos va a indicar el modo dedireccionamiento y luego cada operando que vamos a utilizar. La naturaleza de cada operando va a ser interpretadapor el modo de direccionamiento. Estos modos son los siguientes:

Inmediato: La codificiación de este modo es 000000. Representa acceder al valor de la variable guardada encierta posición. Esto es lo que las constantes representan. Notamos c16.

Directo: La codificación de este modo es 001000. Representa acceder directamente a la dirección de memoria.Esto es lo que las variables representan. Notamos [c16].

Indirecto: La codificación de este modo es 011000. Representa acceder a una dirección de memoria que“apunta” a otra dirección de está guardado el dato de interés. Esto es lo que los punteros representan.Notamos [[c16]].

Registro: La codificación de este modo es 100rrr. Representa utilizar el valor almacenado en el registro rrr.Notamos Rrrr.

Indirecto con Registro: La codificación de este modo es 110rrr. Representa acceder a la posición dememoria del registro. Notamos [Rrrr].

Desplazamiento (o Indexado): La codificación de este modo es 111rrr. Representa acceder a una posiciónde memoria del registro con cierto corrimiento. Notamos [Rrrr + c16].

Los primeros tres y los últimos tres son análogos entre sí donde en los primeros uno tiene un operando en lainstrucción y en los últimos uno utiliza un registro. Veamos algunos ejemplos:

Inmediato:

MOV R1, 230: |0001|100001|000000|(230)2|

Directo:

MOV R1, Var: |0001|100001|001000|@Var|

Indirecto:

MOV R1, [Var]: |0001|100001|011000|@Var|

17

-

La diferencia entre el acceso directo e indirecto es que el indirecto va a acceder a una posición de memoria que leva a devolver otra posición de memoria donde se va a guardar una variable.

Registro:

MOV R1, R5: |0001|100001|100101|

Indirecto con Registro:

MOV R1, [R5]: |0001|100001|110101|

Desplazamiento:

MOV R1, [R5+1F3D]: |0001|100001|111101|1F3D|

La Ortogonalidad de la ISA establece que es posible utilizar cualquier modo de direccionamiento con cualquieroperación. Esto me permite tener un montón de posibles instrucciones. Si n es el número de instrucciones, m elnúmero de modos de direccionamiento y k el número de operandos entonces hay n · mk distintas instruccionesposibles. Esto hace que sea mucho más cómoda la programación pero hace que la implementación para la ALU seacostosa. Ya que no todas las operaciones requieren de la misma cantidad de operandos entonces resulta útil usarcódigos de operación variables para extender la cantidad de posibles operaciones. Para esto consideremos operandosy un código de 4 bits. Si usamos tres operandos entonces podemos usar:

0000|R1|R2|R3 - 1110|R1|R2|R3

Esto me da 15 posibles instrucciones de 3 operandos. Nos reservamos el código que empieza con 1111 para querepresente que el siguiente operando es parte del código. Entonces, para 2 operandos tenemos:

1111|0000|R1|R2 - 1111|1101|R1|R2

De esta forma tenemos 14 posibles instrucciones de 2 operandos. Luego para 1 operando usamos:

1111|1110|0000|R1 - 1111|1111|1110|R1

Esto nos habilita 31 instrucciones de 1 operando. Finalmente, para operaciones sin operandos tenemos:

1111|1111|1111|0000 - 1111|1111|1111|1111

Esto nos habilita 16 operaciones son operandos.

6. Unidad de Control y MicroprogramaciónLa labor de la unidad de control va a ser administrar las instrucciones que el CPU debe ejecutar. La arquitectura

que vamos a considerar es MIPS (Microprocessor without Interlocked Pipeline Stages). Consta de un procesadorRISC con 32 registros de propósito general y 3 tipos de instrucciones de 32 bits. El program counter es de 32 bits, los4 bits más significativos dividen la memoria en Reserved, Text, Data y Stack, los siguientes 26 bits son la direcciónrelativa en dicho espacio y los 2 bits menos significativos son 00, ya que nos permiten alinear a palabras. Esto sehace porque siempre queremos acceder a palabras de 32 bits, así que las alineamos con el 00 para nunca acceder auna dirección del medio de la palabra.

Las instrucciones se dividen en las siguientes categorías:

1. CPU Instructions: Loads, Stores, ALU, Shifts, Multiplicación, División, Jump, Branch y Exception.

2. Floating-Point Unit Instructions: Arithmetic, Data Transfer y Branch.

18

-

Figura 15: Formato de los tres tipos de instrucciones de la arquitectura MIPS.

Figura 16: Instrucciones MIPS que vamos a considerar.

19

-

El ciclo de ejecución de una instrucción MIPS consta de 5 etapas: Fecth (IF), Decode (ID), Execution (EX), lecturade memoria (MEM) y escritura de memoria (WB). Cada instrucción implementada en MIPS es un microprograma.En la Figura 15 puede verse el formato de las tres instrucciones.

Un microprograma ejecuta microoperaciones que permiten mover datos entre registros y memoria. La ejecuciónde estas microoperaciones presenta una precedencia temporal derivada de la utilización múltiple de recursos. Ellenguaje para los microprogramas lo llamamos RTL (Register Transfer Language). Por ejemplo, si queremos hacerfetch de un instrucción en la arquitectura de MARIE entonces en RTL lo escibimos como:

IR←Mem[PC]PC←PC+4

Vamos a considerar solo 6 instrucciones del conjunto de instrucciones MIPS para determinar el camino de datos. Enla Figura 16 se pueden ver las instrucciones que vamos a implementar en RTL y su codificación para la arquitecturaMIPS.

Entonces, veamos cómo implementamos la suma y resta:

Add y SubT1: IR←Mem[PC]

PC←PC+4T2: A←R[rs]

B←R[rt]T3: ALUOut←A±BT4:T5: R[rd]←ALUOut

Cada etapa del ciclo de instrucción se representa con el label con T en su respectivo orden. Entonces, para sumaro restar la operación está codificada con el código de operación, seguido por 5 bits que llamamos rs, luego otros 5bits que llamamos rt , luego otros 5 bits que llamamos rd y finalmente 11 bits que en este caso no nos importan. rty rs van a ser las direcciones de memoria donde los valores A y B que queremos sumar o restar están almacenadosy rd va a ser la dirección de memoria donde vamos a almacenar el resultado de la suma. Entonces, en la etapa defetch queremos cargar la instrucción en el registro de instrucciones IR e incrementar el program counter PC. Enla etapa de decode vamos a setear las variables A y B (que representan registros de entrada de la ALU) que vamosa sumar o restar. En la etapa de execution vamos a hacer la suma o resta y obtener su resultado por la salida dela ALU (ALUOut es el registro de salida de la ALU). En la etapa de lectura de memoria no vamos a hacer nada.Finalmente, en la etapa de escritura de memoria vamos a tomar la salida de la ALU y vamos a almacenar su valor.Esto es lo que el código que escribimos en RTL significa.

Ahora veamos el almacenamiento:

LoadT1: IR←Mem[PC]

PC←PC+4T2: A←R[rs]

B←R[rt]T3: ALUOut←A+sing_ext(IR[15..0])T4: MDR←Mem[ALUOut]T5: R[rt]←MDR

StoreT1: IR←Mem[PC]

PC←PC+4T2: A←R[rs]

B←R[rt]T3: ALUOut←A+sing_ext(IR[15..0])T4: Mem[ALUOut]←BT5:

20

-

Notemos que para esta operación cargamos al registro B de la ALU el contenido del registro rt cuando no hacíafalta. Esto lo hicimos para que las dos primeras etapas sean idénticas a las de la suma y resta, ya que esto va a hacerque el diseño de la lógica de control sea mucho más simple. Para Load, en la etapa de execution en vez de usar elregistro B vamos a sumar la extensión con signo de los últimos 16 bits de lo que esté en el código de instrucción.Luego en la etapa de lectura de memoria vamos a almacenar en el Memory Data Register (MDR) lo que haya enla memoria en la dirección que obtuvimos de la suma de la ALU. Finalmente, en la etapa de escritura de memoriavamos a escribir lo que escribimos en MDR en la etapa anterior en el registro indicado en la instrucción. Store esbastante similar a Load con la diferencia de que no tenemos que actualizar los registros.

Veamos ahora Branch on Equal:

BranchT1: IR←Mem[PC]

PC←PC+4T2: A←R[rs]

B←R[rt]ALUOut←PC+sign_ext(IR[15.00])

-

Figura 17: Implementación RTL de las instrucciones separadas en las cinco etapas.

Usamos multiplexores para poder diferencial las entradas que provienen del PC de otras. Esto va a ser útil másadelante. Ahora, para el decode debemos considerar ambas implementaciones: la del Branch y la del resto menosJump. El diseño queda así:

22

-

Veamos cómo va avanzando el diseño a medida que vamos agregando las etapas:

23

-

Luego, debemos agregar la unidad de control que sea capaz de determinas las señales de control necesarias parala ejecución de cada etapa de cada instrucción. Es decir, la unidad de control va a seleccionar el flujo de datoscorrespondiente a cada etapa. Finalmente, el diseño nos queda así:

24

-

Al hacer este diseño se tomaron varias decisiones de todo tipo, en particular qué códigos vamos a usar paraindicar distintas cosas. Por ejemplo, la señal conectada a la unidad de control llamada RegDst indica si el registroa utilizar es el rt o rd y para eso usamos un multiplexor donde el número 1 está asociado a rd y el 0 a rt. Esta esuna decisión que se tomó durante el diseño. En la Figura 18 pueden verse dos tablas que resumen las decisionestomadas durante el diseño.

Sin embargo, notemos que falta algo más. A medida que se van ejecutando las etapas la unidad de control debereaccionar a los resultados y elegir el camino que deben tomar los datos. Para lograr esto podemos armar el siguientediagrama de flujo:

25

-

Figura 18: Tablas de las decisiones tomadas en el diseño del computador.

26

-

Este diagrama de flujo va a ayudarno a diseñar la unidad de control, ya que debe ajustarse a estas decisiones. Silas decisiones que tomamos fueran distintas entonces la unidad de control debería cambiar para reflejar este cambio.Entonces, ya que numeramos cada estado de la unidad de control con números entre el 0 y el 9 podemos armar unatabla que indique qué valor debe tomar cada señal de control para cada estado:

Entonces, el diagrama de flujo con los valores de cada señal de control para cada estado posible nos queda así:

27

-

Entonces, una vez que tenemos esto podemos armar la unidad de control. Para eso existen dos maneras distintasde hacerlo. Una manera es usando Memoria ROM (Read-Only Memory) que consiste en usar un decodificador de(en este caso) las 1024 posibles combinaciones conectando todos los cables mediante fusibles y quemando aquellos queno queremos que estén conectados. Este método es muy rápido y relativamente simple ya que consiste principalmentede conexiones entre cables pero hay mucho desperdicio, ya que la mayoría de las combinaciones de entrada no seutilizan. La otra manera consiste en usar PLA (Programmable Logic Arrays) que consiste en usar conjunciónde disyunciones de las señales para determinar la salida. Este método es relativamente lento en comparación aROM porque consiste de dos etapas (una de conjunciones y otra de disyunciones) pero es programable y no haydesperdicio. Otra posibilidad es usar microprogramación y armar un microdiseño que ejecute microinstruccionescomo sean necesarias.

7. Entrada y Salida7.1. Control de Dispositivos e Interrupciones

A nuestro computador le vamos a conectar dispositivos externos, llamados periféricos, que van a modificar sucomportamiento. Algunos ejemplos de estos dispositivos son el mouse, teclado, pantalla, discos de almacenamiento,impresora, etc. Estos dispositivos van a permitirle al usuario manipular la computadora en tiempo real y por lotanto necesitamos desarrollar métodos por los cuáles la computadora se va a encargar de atender estos dispositivos.Veamos entonces dos tipos distintos de acceso a entrada/salida (I/O) - es decir - dos maneras distintas de enviar yrecibir información de dispositivos periféricos.

Una forma es establecer direcciones en la memoria principal que se van a usar solamente como lectura o escriturade dispositivos I/O. El controlador del dispositivo va a acceder a una determinada dirección cada vez que quieraleer sobre la memoria y a otra dirección cada vez que quiera escribir sobre la memoria. De esta forma se usa lamemoria principal como puente de comunicación entre el computador y el dispositivo. La otra forma es establecer

28

-

Figura 19: Esquema de la comunicación entre el CPU y los dispositivos I/O a través de uncontrolador de interrupciones.

instrucciones especiales que se encarguen del I/O. Podemos hacer una instrucción de In y otra de Out para ciertosdispositivos a través de un identificador específico y guardar la información en variables de la memoria principal.

Otra cuestión importante es cómo la computadora establece una noción de importancia sobre los dispositivosI/O. Es decir, cómo el CPU se entera de un evento (un click, una tecla presionada, etc.) en algún dispositivo. Unaforma de establecer esto se llama Polling y se trata de consultar periódicamente a cada dispositivo si hubo algúnevento. El problema de este métodos es que desperdicia mucho tiempo si es que no hubo un evento. Otra opciónes usar interrupciones del CPU, donde los dispositivos mandan una señal que interrumpen al CPU para notificarlede un evento. Para esto los dispositivos se conectan a un controlador de interrupciones que se encarga de mandary recibir señales al CPU notificando eventos. En la Figura 19 puede verse un esquema de la comunicación entreel CPU y los dispositivos I/O a través de un controlador de interrupciones. Por lo general para cada dispositivoI/O se desarrollan programas llamados Drivers que la computadora ejecuta cada vez que ese dispoisitivo hace unainterrupción. Estos drivers son programas hechos para cada arquitectura y le enseñan al CPU cómo comunicarsecon cierto dispositivo, muchos drivers son genéricos para cierto tipo de dispositivos y otros que son para dispositivosmuy específicos (un lector de barras por ejemplo) necesitan instalarse manualmente, sea mediante un disco, un USBo descargando el instalador de internet.

Consideremos el procesador Intel 8086 de la Figura 20. Notemos que tenemos un controlador de interrupcionescon un registro de interrupciones. Cada vez que un dispositivo conectado al controlador manda una señal colocaun 1 en el registro asociado a ese dispositivo. En la imagen se puede ver que el dispositivo 4 está encendido.Luego tenemos un registro máscara que indica (con un 1) cuáles son las interrupciones permitidas - es decir - quédispositivos pueden interrumpir actualmente al procesador. Esta máscara está determinada por el software quese está ejecutando en el momento. Entonces, si se hace una interrupción permitida el controlador manda la señalINTR al procesador. El procesador entonces termina la instrucción en curso, chequea la señal INTR y mira unapalabra que se llama palabra de estado (PSW). En esa palabra hay un bit denominado IF que determina si elprocesador está dispuesto a ser interrumpido. Si el procesador está dispuesto a ser interrumpido entonces le va amandar la señal INTA (Interruption Acknowledged) al controlador. Una vez que el controlador recibe esta señalmanda por el bus de datos el número del dispositivo que pide la interrupción (en este caso el 4). Este númerosirve para hallar en qué dirección está el programa que hay que ejecutar. Esto lo logra hacer ya que al prenderla máquina el sistema operativo se encarga de establecer direcciones de memoria (en este caso a partir de 0000)donde va a guardar un puntero que apunta al comienzo del programa que cada dispositivo requiere para comenzarla interrupción (driver). En este caso en la dirección 0006 tenemos guardada la dirección del comienzo del programapara manejar las interrupciones del dispositivo 4. Este lugar donde se guardan estos punteros se llama vector deinterrupción. Para calcular dónde está el puntero usa que la dirección a la que debe ir es V0 + w ∗ (n− 1), donde V0

29

-

Figura 20: Interrupciones en el procesador Intel 8086.

es el comienzo del vector de interrupciones, w es el número de bytes por palabra y n es la cantidad de dispositivos.En este caso V0 = 0000, w = 2 y n = 4.

Entonces, los pasos de una interrupción para el procesador Intel 8086 son los siguientes:

Hardware

1. El dispositivo requiere una interrupción así que coloca un 1 en su posición del registro de interrupciones.

2. Si el dispositivo está habilitado el controlador activa la señal de interrupción a la que se encuentra conectado.

3. La CPU termina de ejecutar la instrucción en curso y verifica si el flag IF está encendido y si la señal INTRestá encendida. Si es así, enciende la señal INTA.

4. El controlador envía por el bus de datos el identificador del dispositivo que produjo la interrupción.

5. La CPU guarda el contexto del programa en la pila (PSW y PC).

6. La CPU deshabilita las interrupciones globalmente apagando el flag IF.

7. Se pasa el procesador a modo kernel para que la rutina ejecute con privilegios de sistema operativo.

8. Cambia el PC a la dirección de memoria donde comienza el programa que se encarga de ejecutar la interrupcióndel dispositivo que produjo la interrupción.

Software

1. Se guarda la máscara de interrupciones.

2. Se modifica la máscara a fin de habilitar selectivamente las interrupciones que permitiremos durante la eje-cución de la rutina.

3. Se habilitan globalmente las interrupciones prendiendo el flag IF.

30

-

Figura 21: Esquema de bloques del DMA conectado a la CPU, el bus, la memoria y el controladorde interrupciones.

4. Se ejecuta la rutina de atención de la interrupción solicitada.

5. Se deshabilitan globalmente las interrupciones apagando el flag IF.

6. Se reemplaza la máscara de interrupciones con la original.

7. Retorna de la interrupción con una instrucción que restaura el estado del programa antes del llamado (IRET).Esta instrucción restaura el PC y el PSW de la pila.

Consideremos ahora un disco donde almacenamos información (disco rígido, CD, DVD, USB, etc.). Este dispositivoes distinto al resto ya que se va a usar para cargar la memoria con volúmenes información que son son muchomayores a los del resto de dispositivos y por lo tanto definen un tratado paradigmático. Un método que se utilizapara comunicarse con el CPU se llama PIO (Programmed Input/Output). Este método de interrupción consiste enejecutar un programa que lee el disco y coloca cada palabra en el memoria principal. Ya que el bus permite solo unapalabra entonces esto debe hacerse palabra por palabra hasta tener en la memoria todo el bloque de informaciónnecesario para la ejecución de la tarea solicitada. El programa que realiza esta tarea es interno al disco. El problemade este método de interrupción es que dejaba a la CPU ocupada por mucho tiempo, copiando información del discoa la memoria. Otro método que remediaba este problema se llama DMA (Direct Memory Access) que se utilizapara construir un subsitema que independiza a la CPU de los dispositivos que se usan para leer o escribir grandesvolúmenes de información (se usa también para impresoras). Este método consiste en un controlador (DMAC)que se va a encargar de la transferencia de información mientras el CPU continúa ejecutando instrucciones queno requieran de esta información. El CPU configura el DMAC para que transfiera la información (sea indicandola cantidad de palabras del dispositivo o desde qué dirección empezar a transferir) y luego continúa ejecutandoinstrucciones (siempre y cuando sea posible) mientras el DMAC se encarga de la trasnferencia. Una vez terminadala transferencia el DMAC solicita una interrupción y el CPU la atiende. En la Figura 21 se puede ver un diagramade las conecciones entre dispositivos para este método.

7.2. Conversión de SeñalesLas señales que recibe un dispositivo I/O son señales analógicas. Estas señales deben digitalizarse para que

la computadora pueda manejarlas y luego deben pasarse de vuelta a señales analógicas para el usuario. Vamosa pensar a las señales analógicas como señales físicas continuas dependientes del tiempo. Estas señales puedendescomponerse en funciones armónicas con cierta amplitud y frecuencia. Entonces, el tratamiento de una señal

31

-

Figura 22: Conversión Analógica-Digital de una señal analógica f (t) (en gris) a otra digital (enrojo) con una frecuencia de muestreo de 6 Hz.

Figura 23: Amplificador operacional.

analógica utilizando una computadora digital implica necesariamente la Conversión Analógica-Digital (ADC)y la Conversión Digital-Analógica (DAC). En la Figura 22 puede verse la conversión analógica-digital de unaseñal f (t). Notemos que la digitalización de una señal limita la cantidad de valores que se toman en ambos ejes xe y.

Para evitar o minimizar la pérdida de información en ADC el Criterio de Nyquist establece que la frecuenciade muestreo - es decir - la frecuencia a la cual se toman muestras de la señal debe ser mayor que el doble de lamáxima frecuencia de la señal:

fs > 2fmaxAdemás, debe definirse un rango de valores a obtener de la señal con ciertos umbrales - es decir - con ciertos posiblesvalores dentro del rango donde la señal va a ser efectivamente redondeada para tomar valores discretos. Mientrasmayor sea la frecuencia de muestreo y mientras menor sea la distancia entre umbrales menor va a ser la cantidadde información perdida en la ADC.

Un dispositivo útil en la conversión de señales es el Amplificador Operacional, conocido como Op-Amp.Este dispositivo permite amplificar la diferencia de tensión entre la entrada no-inversora V+ y la entrada inversoraV− de forma que Vout = AOL (V+ − V−), donde AOL es la ganancia del dispositivo cuando no es retroalimentado.En la Figura 23 puede verse la representación circuital de un op-amp. Por lo general, la magnitud de gananciade los op-amp es del orden de 105 o más. Entonces, cuando el op-amp está en configuración de lazo abierto (no-retroalimentado) la más pequeña diferencia de tensión entre V+ y V− se traduce en que la salida es muy cercana a latensión de alimentación, efectivamente actuando como un comparador entre señales. Sin embargo, cuando está enconfiguración lazo cerrado (retroalimentado negativamente) la ganancia es significativamente menor ya que quedadeterminada por la configuración de la red resistiva del circuito. En la Figura 24 pueden verse diagramas circuitalespara ambas configuraciones del op-amp. La red resistiva de la configuración de lazo cerrado es la relación entre la

32

-

Figura 24: Configuración lazo abierto (open loop) y lazo cerrado (closed loop) para un amplificadoroperacional.

Figura 25: Conversión Digital-Analógica de una señal de 4 bits mediante un amplificador opera-cional y resistencias en paralelo.

resistencia Rf del lazo y Rg de la entrada inversora. Si Rf < Rg entonces la ganancia no se ve seriamente afectadaya que ACL = 1 + RfRg . Este dispositivo nos va a servir para ADC y DAC.

Veamos cómo usar un op-amp para DAC. En la Figura 25 puede verse una configuración donde se usa unop-amp en lazo cerrado para DAC. Cada señal A, B, C y D es una señal digital con un resistencia que sirve parapesarla que es digitalizada mediante un op-amp. Resulta que:

Vout = −(

RfRD

VD +RfRC

VC +RfRB

VB +RfRA

VA

)= −

(VD +

12VC +

14VB +

18VA

)Cada resistencia en la entrada le asigna un peso a esa señal y ya que tenemos cuatro señales con distintos pesos esonos permite 24 distintos valores en la salida entre 0V y −9.375V. Mientras más señales se usen mejor puede ser laconversión a analógico. En la Figura 26 puede verse otra configuración que independiza la tensión digital de la desalida ya que solo se usa para cambiar la red resistiva y se usa una tensión de referencia en el op-amp.

Ahora veamos cómo usar un op-amp para ADC. En la Figura 27 puede verse una configuración donde seusan varios op-amps en lazo abierto junto con un codificador para digitalizar una señal de 10V. Ya que la entrada

33

-

Figura 26: Conversión Digital-Analógica de una señal de 4 bits mediante un amplificador opera-cional y resistencias en serie.

Figura 27: Conversión Analógica-Digital de una señal mediante un amplificador operacional.

34

-

Figura 28: Diagrama circuital de la placa de sonido.

analógica está en la entra inversora del op-amp entonces si VA > Vi, donde Vi es la tensión de entrada de algúnop-amp, entonces la salida es 0V y si no la salida es 5V. Notemos que los op-amps están negados en la salida asíque este resultado se va a invertir. Una desventaja de este dispositivo es que requiere muchos op-amps ya que laresolución está determinada por la cantidad de op-amps. Para remediar esto se usa una placa de sonido que tieneuna microcomputadora. Lo que esta microcomputadora hace es usar un contador que suma hasta que llega al valorque es igual a la señal. De esta forma podemos saber cuánto vale la señal en forma digital para una gran cantidadde puntos. En la Figura 28 se puede ver el diagrama circuital que muestra el funcionamiento de la placa de sonido.Notemos que usa una señal de comienzo (start) junto con el clock y la salida del op-amp. Esto está conectado alcounter, lo que hace que mientras que la señal analógica sea mayor que la del contador y mientras no haya una nuevaseñal de comienzo el contador cuente un número en cada ciclo de clock. Cuando el contador supera o iguala la señalanalógica entonces el AND queda negado y esa señal digital queda fija en el valor que estaba, lo que nos permiteguardarla o manipularla de alguna forma. Cuando llegue una nueva señal de comienzo el contador se resetea y elciclo comienza de vuelta. Esto puede hacerse muy rápido así que sirve como para digitalizar una señal de sonido(fNyquist = 44.1 kHz). Este conversor es mucho más eficiente que el anterior ya que uso un solo op-amp a diferenciade los miles que usa el otro.

8. Memoria8.1. Tipos de Memoria

Ya vimos en otras secciones cómo armar circuitos que almacenen datos y por lo tanto puedan usarse comomemoria de la máquina. Sin embargo, no detallamos en cómo construir la memoria principal de la máquina. Vimosque para la unidad de control podíamos usar memoria ROM que es muy rápida en la lectura pero no es reprogramable- es decir - no puede reescribirse. También mencionamos los PLAs que también son rápidos en lectura y que sonreprogramables, pero incluso estos dispositivos no nos van a servir para la memoria principal porque no son losuficientemente rápidos en escritura. Lo que usamos hoy en día es la memoria RAM (Random Access Memory) queson memorias que pueden ser leídas y escritas prácticamente a la misma velocidad que es independiente del lugarfísico donde se está escribiendo/leyendo. Principalmente existen dos tipos de memoria RAM, la estática (SRAM)y la dinámica (DRAM).

En la Figura 29 puede verse un diagrama circuital de la memoria SRAM. Consiste de seis transistores (haydos en cada NOT) que forman dos bits Q y Q̄ que son opuestos entre sí. A esto se lo llama biestable y es lo que

35

-

Figura 29: Diagrama circuital de la memoria SRAM.

Figura 30: Diagrama circuital de la memoria DRAM.

vimos en circuitos secuenciales. Notemos que en esta memoria tres transistores consumen máxima energía mientrasque los otros tres consumen la energía residual. Esto hace que esta memoria seade alto consumo. Lo bueno es quela lectura es directa y no destructiva - es decir - uno puede medir el bit cuantas veces quiera y no va a cambiar.Esto hace que la memoria SRAM sea sumamente rápida.

En la Figura 30 puede verse un diagrama circuital de la memoria DRAM. Consiste de un transistor y uncapacitor que va a almacenar carga si el valor del bit es 1 y va a estar descargado si el valor del bit es 0. Para leeresta memoria vamos a tener una línea de sensado (sense line) y una de control, donde la de control va a habilitarque la corriente vaya a la línea de sensado y en esta se va medir una corriente (o no) para interpretar si el valor delbit es 1 o 0. Notemos que a diferencia de la memoria SRAM la lectura en este caso es destructiva ya que descarga elcapacitor. Por lo tanto, luego de una lectura es necesario cargar de vuelta el capacitor si es que estaba cargado. Estohace que esta memoria sea más lenta que la anterior. Lo bueno es que es mucho más eficiente ya que no tiene tantostransistores como en la memoria SRAM. Otra desventaja de esta memoria es que a medida que pasa el tiempo elcapacitor se va descargando, así que cada tanto es necesario refrescar todos los capacitores para que no pierdan losbits almacenados.

Debido a que ninguna de las dos memorias es mejor que la otra entonces no va a bastar con elegir una de las dospara usar en la memoria principal. Vamos a tener que analizar la estructura de la memoria principal y elegir algunade las dos para cada parte. Debido a que la velocidad de los procesadores es mucho mayor que la de las memorias(ya que el crecimiento en velocidad de los procesadores es exponencial mientras que el de las memorias es lineal)entonces vamos a formar una jerarquía de memorias donde las más rápidas son las que se conecten al procesadorpara así disminuir su tiempo de espera. En la Figura 31 puede verse un diagrama de esta jerarquía mediante unapirámide, donde las memorias más rápidas y costosas están por encima de las más lentas y baratas. Las memoriasmás altas en la pirámide van a ser las más cercanas al procesador para minimizar el tiempo perdido del mismo. Lamemoria más cercana al procesador son los registros, con los cuales ya estuvimos trabajando. Estas memorias estánarmadas con celdas biestables y son tan rápidas que prácticamente no alentizan al procesador.

Luego de los registros viene la memoria Cache y hay dos tipos. La de nivel 1 está construida como SRAM y seencuentra dentro del procesador como subsistema aparte y entonces el CPU tiene electrónica asociada a administraresta memoria. El objetivo de esta memoria es amortiguar el costo de acceder a la memoria principal. La de nivel 2por lo general se encuentra en la motherboard y opera como puente entre el procesador y la memoria principal. Estamemoria también está construida como SRAM pero su administración es más compleja que la de nivel 1 y además

36

-

Figura 31: Pirámide de jerarquía de memorias. Las más rápidas están encima de las más lentaspero a su vez las más rápidas son las más costosas.

está más alejada del procesador, lo que lleva a que tenga tiempos de acceso más lentos. Ambas memorias cache vana almacenar copias de algunos datos e instrucciones que están en la memoria principal y van a estar disponiblesjusto cuando el procesador las necesita, evitando así que este tenga que esperar.

Luego de ambas memorias cache está la memoria principal que está construida como DRAM y que por lo tantoes más lenta que las otras. Junto con las otras forman las memorias del sistema, el resto (fixed rigid disk, opticaldisk y magnetic tape) van a formar memorias externas (discos rígidos, USBs, CDs, DVDs, Blu-Rays, etc.) que vana servir de almacenamiento más masivo o de backup.

8.2. Memoria CacheVeamos en detalle cómo funciona y cómo se diseña la memoria cache. Esta memoria debe ser los suficientemente

grande como para que el procesador sea capaz de resolver la mayor cantidad posible de accesos a esta memoriasin recurrir a la memoria principal y lo suficientemente pequeña como para no afectar el consumo ni el costo delsistema. Para medir este balance en tamaño usamos el hit rate - es decir - la razón de hits, o accesos a ítems que seencuentran en el cache, sobre la cantidad total de accesos que incluyen aquellos que no se encuentran en el cache.Es claro entonces que queremos que el hit rate sea lo más alto posible ya que significa que la mayoría de las vecesel procesador accede al cache y no a la memoria principal. Definimos el miss rate como m = 1 − h, donde h es elhit rate. Es claro entonces que un miss es cuando la memoria accede a un ítem que no está en el cache.

En la Figura 32 podemos ver un diagrama de bloques de la estructura del computador con memoria cache.Tenemos un controlador que se va a encargar de controlar la información almacenada en el cache. Cada vez queel CPU pida información el controlador se va a encargar de darle esa información. Si la información que el CPUrequiere está en el cache entonces el controlador simplemente se le alcanza. Si la información que el CPU requiere noestá en el cache entonces el controlador se encarga de acceder a la memoria principal para alcanzarle la informaciónal CPU y actualiza el cache bajo algún criterio. Con esto nos referimos a que debe existir algún criterio para elegirde qué información almacenar en el cache de forma que maximice el hit rate. Existen dos principios para esto, unoes el de Vecindad Espacial y otro es el de Vecindad Temporal. El primero establece que si un ítem es utilizadoentonces es probable que ítems cercanos sean utilizados pronto, mientras que el segundo establece que si un ítemes utilizado entonces es probable que pronto sea utilizado de vuelta. Consideremos el siguiente código (en C):

int v[9];int i = 0;for (int j = 0; j < 3; j++) {

37

-

Figura 32: Estructura del computador con memoria cache.

for (int k = 0; k < 3; k++) {v[i] = j + k;i++;

}

}

En este ejemplo la utilización de las variables i, j y k responden al principio de vecindad temporal mientras que lautilización del arreglo v responde al principio de vecindad espacial.

Entonces, para respetar estos principios y maximizar el hit rate lo que se hace es separar la memoria cache enbloques. Cada vez que el controlador tenga que acceder a la memoria principal además de traerse el ítem que elCPU pide se trae información cercana al ítem para llenar un bloque de memoria cache. Esto cumple con el principiode vecindad temporal ya que almacena en el cache la información utilizada y también cumple con el principio devecindad espacial ya que almacena también información cercana a la utilizada. El tamaño de los bloques debeelegirse con cuidado, ya que mientras mayor sea más lento va a ser el acceso a la memoria principal y menor va aser la cantidad de bloques disponibles; mientras que menor sea el tamaño del bloque menor va a ser la cantidad deinformación cercana espacialmente almacenada. Además, se debe almacenar un directorio con las entradas a cadabloque de la cache, ya que debe existir alguna manera de saber qué información está en el cache y qué informaciónno.

Veamos entonces algunos métodos para reemplazar los contenidos del cache. Un método se llama Least RecentlyUsed y consiste en priorizar los contenidos utilizados recientemente. Otro se llama Least Frequently Used y consisteen priorizar los contenidos más utilizados. Finalmente, hay otro que se llama First In - First Out y consiste enpriorizar los últimos contenidos guardados.

El cache también va a impactar en la escritura en memoria y, por lo tanto, existen distintas maneras de manejaresto. Una manera se llama Write Through y consiste en que el procesador escriba en la memoria principal y luegoel controlador actualice el cache. Otra manera se llama Write Through Buffered y consiste en que el procesadorescriba en el cache y luego el controlador actualiza la memoria principal. Finalmente, otra manera se llama CopyBack y consiste en que el procesador escriba en el cache y luego antes de borrar una linea del cache que no está enla memoria principal el controlador hace una copia a la misma.

Entonces, consideremos la estructura interna del cache. En la Figura 33 puede verse un diagrama interno de lamisma. El cache interno (nivel 1) se separa en dos partes: I-Cache que se encarga del almacenamiento de instrucciones

38

-

Figura 33: Estructura interna del cache.

y D-Cache que se encarga del almacenamiento de datos. El cache de nivel 2 no distingue entre instrucciones y datos.Por lo tanto, esta memoria se encarga de guardar información que es utilizada recientemente para pasar a la cachede nivel 1. Por eso la cache de nivel 2 es mucho mayor en tamaño que la de nivel 1. Luego tenemos la memoriaprincipal con un acceso mucho más lento y la memoria virtual que se va a ver recién en Orga 2. A este sistema decache se lo llama Cache Multinivel.

9. Buses9.1. Diseños y Protocolos

Las componentes que estuvimos viendo del computador se comunican entre sí mediante buses. Ya que estoscaminos de conexión son únicos entonces debe necesariamente existir una alternación entre ciclos de lectura/escrituray ejecución de instrucciones, lo cual forma un cuello de botella ya mencionado como el cuello de botella de vonNeumann.

Los buses están formados por un conjunto de señales con un propósito específico y sirven para conectar dos omás componentes. En general se cuentan con señales de direcciones, señales de datos y señales de control y entoncesse tiene un bus para cada tipo de señales. Por lo general, los buses se construyen de forma jerárquica ya que existenconexiones preferenciales, como la del procesador al cache por ejemplo. En la Figura 34 podemos ver la estructurade un ejemplo de jerarquía de buses. Notemos que hay un bus local de alta velocidad que conecta al procesadorcon el cache y con el controlador I/O, luego un bus de sistema que conecta el cache con la memoria principal yluego un bus de expansión que conecta otros dispositivos a una interface que está conectada al bus de sistema. Deesta forma uno logra jerarquizar los procesos del computador y los buses adquieren propósitos más específicos. Ala conexión entre buses de distintos niveles se la llama Bridge.

Además, a un bus se lo divide en Líneas. Estas líneas pueden ser Dedicadas o Multiplexadas. Las líneasdedicadas tienen un rol único en el sistema y entonces el bus está divido en base a los roles que debe cumplir. Cadalínea tiene un dedicación física, que se refiere a la conexión entre las componentes, y una dedicación funcional, que serefiere a la función que cumplen. La dedicación de las líneas implica menor cantidad de disputas por su uso al mismotiempo, lo que incrementa el tamaño y costo del sistema pero incrementa la velocidad. Las líneas multiplexadascumplen más de un rol en el sistema. Por ejemplo, si el bus de datos y el bus de direcciones comparten las mismaslíneas físicas entonces estas son multiplexadas. La multiplexización de líneas reduce el tamaño y costo del sistemapero complejiza la lógica de administración. Llamamos el Ancho de un bus a la cantidad de líneas físicas que utiliza.Esta característica del bus es la que determina su desempeño. El ancho del bus de direcciones determina el espacio

39

-

Figura 34: Ejemplo de jerarquía de buses.

de memoria direccionable y el ancho del bus de datos determina la cantidad de accesos a memoria necesarios paratransferir la misma cantidad de información.

A la hora de diseñar un bus uno debe considerar la coordincación entre eventos. Esto impone la temporiza-ción de los eventos. Existen dos tipos de temporización: la Temporización Sincrónica y la TemporizaciónAsincrónica. En la Figura 35 puede verse un diagrama de la temporización sincrónica entre eventos en un bus.Esta temporización utiliza un clock (distinto al del CPU) y usa el ciclo de reloj para desarrollar ciertos eventos.Notemos que cada evento tiene una pendiente ascendiente al comienzo y una descendiente al final. Esta prendienterepresenta un tiempo de estabilización del bus que es necesaria para la correcta lectura o escritura. En la Figura36 puede verse un diagrama de la temporización asincrónica entre eventos en un bus. Notemos que a diferencia dela temporización sincrónica esta no usa un clock central, sino que recibe información de una componente hasta queesta termina y entonces pasa a la siguiente. Esto requiere que hayan ciertas señales que permitan determinar queacciones se están tomando en cada momento. Esto complejiza la administración del bus pero también lo flexibiliza.Notemos que la señal MSYN prendida dispara la colocación de los datos en DATA y la señal SSYN prendida disparala colocación de los datos en MREQ, RD y MSYN.

Consideremos ahora cómo son los protocolos de lectura y de escritura para líneas dedicadas y multiplexadas delbus. Para líneas dedicadas en la escritura la componente que escribe coloca la dirección en el bus de direcciones ylos datos en el bus de datos en un mismo ciclo de reloj y luego notifica este hecho a la componente a escribir. En lalectura, la componente que lee coloca la dirección en el bus de direcciones y notifica este hecho a la componente ala componente a leer en un ciclo de reloj. Luego en el siguiente ciclo de reloj la componente leída coloca los datosen el bus de datos y notifica a la componente que lee.

Para líneas multiplexadas en la escritura la componente que escribe coloca la dirección en el único bus y lonotifica a la componente a escribir en un ciclo de reloj. Luego, la componente a escribir confirma que la direcciónfue leída y en otro ciclo de reloj la componente que escribe coloca los datos en el bus y notifica a la componentea escribir. En la lectura, la componente que lee coloca la dirección en el bus y notifica a la componente a leer enun ciclo de reloj. Luego, la componente a leer coloca los datos en el bus y notifica a la componente que lee en otrociclo de reloj.

Ya que los buses son recursos compartidos y requeridos por muchas componentes al mismo tiempo entoncesdebe existir un método de arbitraje que determine qué componente tiene acceso a cierto bus en un determinadomomento. Un sistema deArbitraje Centralizado requiere de un controlador que implementa la lógica de arbitraje.En este sistema el controlador va a estar al tanto de qué componentes requieren el bus y va a ceder acceso a lasdistintas componentes que lo requieran. Un sistema de Arbitraje Distribuido deja que las componentes tenganun subsistema de control de acceso y que todos estos subsistemas juntos administren el uso del bus. En la Figura37 puede verse un esquema para ambos sistemas de arbitraje de bus. En el arbitraje centralizado notemos que cadacomponente debe hacer un pedido (request) de uso al controlador (bus arbiter) y este se encarga de ceder permisoa solo un dispositivo para que acceda al bus. En el arbitraje distribuido en este caso tenemos a los dispositivos

40

-

Figura 35: Diagrama de la temporización sincrónica entre eventos en un bus.

Figura 36: Diagrama de la temporización asincrónica entre eventos en un bus.

41

-

Figura 37: Esquema de ambos sistemas de arbitraje de bus: centralizado y distribuido.

ordenados de mayor a menor prioridad de uso y entonces los pedidos se conectan entre sí mediante un OR. Luego,el controlador le cede el uso al dispositivo con mayor prioridad y este utiliza el bus si lo requiere y si no le cede elpermiso al siguiente dispositivo de la cadena. De esta forma el controlador no tiene que ocuparse de las prioridades,si no que cada dispositivo tiene una lógica interna que se encarga de ceder el bus si no lo necesita.

9.2. EjemplosVeamos algunos ejemplos de buses que se usan o se usaron en algunas PCs.

PC Bus Este es el primer bus que se diseñó para una PC y fue por IBM para la IBM PC que usaba un procesadorIntel 8088. Este bus consistía de 62 líneas: 20 líneas de direcciones que permitían usar 1 Mb de memoria direccionable,8 líneas de datos con palabras de 1 B y 34 líneas de control entre las que se encuentran líneas de lectura/escritura enmemoria, lectura/escritura en I/O, interrupciones, DMA, etc. Luego de este bus Intel lanza el siguiente procesadorque fue el Intel 80286 con un bus de direcciones de 24 bits y bus de datos de 16 bits. IBM estandariza este bus conel nombre PC-AT.

Bus ISA Este bus (Industrial Standard Architecture) es un rediseño del PC-AT al PC Bus para que sean compa-tibles. Al igual que el PC Bus cuenta con 62 líneas: 24 líneas de direcciones que permitían usar 16 Mb de memoriadireccionable, 16 líneas de datos que permiten palabras de 2 B y 22 líneas de control entre las que se implementaacceso a dos controladores de interrupciones y dos de DMA.

Bus EISA Luego del procesador Intel 80286 vino el procesador Intel 80386 con un bus de datos de 32 bits ydirecciones de 32 bits. Entonces, este nuevo bus que era la evolución del bus ISA termina siendo electrónicamentecomplejo, poco escalable y con una velocidad máxima de 33 MHz, que por más de que fuera muy rápido para laépoca terminaría siendo limitante considerando el aumento de velocidad de procesadores.

VESA Local Bus Este bus se desarrolló por un consorcio de fabricantes de controladores de video frente a laevolución de las pantallas de rayos catódicos a pantallas a color de 16 bits. Este bus es específico para las placas devideo y es una extensión del bus ISA con velocidad entre 25 MHz y 50 MHz.

42

-

Figura 38: Estructura del bus PCI.