Practica 9 Diseño Secuencial (Jeopardy)

-

Upload

elias-aguilar -

Category

Documents

-

view

76 -

download

4

description

Transcript of Practica 9 Diseño Secuencial (Jeopardy)

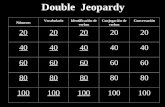

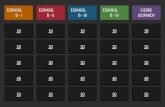

OBJETIVORealizar un circuito, se aplicar la metodologa para disear un sistema secuencial sncrono y se implementar por medio de un lenguaje de descripcin de hardware en un dispositivo lgico programable.HIPTESISSe realizara un circuito de diseo secuencial el cual se basa en una maquina de Moore, con el que se trata de representan el concurso de jeopardy, que funcionara obteniendo tres impulso de entrada y en la salida solo se representara el impulso que se haya obtenido primero. MARCO TERICODiseo secuencial En el sistema secuencial sncrono los valores de salida no dependen nicamente de las combinaciones de entrada, sino tambin de la salida misma. Los cambios de estado estn sujetos a una seal de sincrona de los Flip Flops llamada reloj o Clk como se representa en la figura 1.

Figura 1. Diagrama del proceso del sistema secuencial.Metodologa del diseo secuencial, concluyendo con la implementacin mediante captura esquemtica. 1. Especificar el sistema (diagrama de transicin). 2. Determinar la cantidad de Flip Flops. 3. Asignar los valores a los estados. 4. Determinar las entradas y salidas. a. Entrada de sincrona reloj.b. Entradas combinacionales. c. Salidas combinacionales.d. Salidas registradas (FF).5. Construir una tabla de estados. 6. Minimizar. 7. Obtener diagrama esquemtico. 8. Realizar la implementacin. MATERIAL 7 resistencias de 330 de W 4 push buttons Circuito integrado GAL22V10 1 Circuito integrado SN7414 1 Capacitor electroltico de 220 f 1 Potencimetro de 1 K 8 diodos emisores de luz PROCEDIMIENTOSe realizo un circuito de diseo de secuencia y consiste en el concurso de jeopardy, el cual se construyo en base a la mquina de Moore, el sistema secuencial deber de indicar por medio de uno de los tres focos (Foco A, Foco B, Foco C) cual de los tres participantes en un concurso de preguntas y respuestas es el primero en oprimir el botn (Botn A, Botn B, Botn C), se requiere de un cuarto botn (Botn R) para que el conductor del programa una vez terminada la respuesta, regrese al sistema a condiciones iniciales (Focos apagados). A continuacin se describir el proceso de montaje y realizacin del circuito. Para especificar el comportamiento del sistema se puede emplear el diagrama de transicin, donde se indican entradas, salidas y estados, el resultado se muestra en la figura 2.

Figura 2. Diagrama de transicin.La asignacin de valores a los estados puede ser al azar y corresponde a las combinaciones posibles que generan las salidas Q de los Flip Flops. En el diagrama de bloques (figura 3) se tienen como entradas los botones A, B, C y R adems de la seal de sincrona Clk, como salidas Combinacionales se requieren cada uno de los focos y como salidas secuenciales o registradas dos Flip Flops llamados Q1 y Q0 que sus combinaciones representaran a cada uno de los cuatro posibles estados.

Figura 3. Diagrama de bloques.En la tabla de estados se puede observar el estado en funcin de la posible entrada, se considera en que solo un botn pude presentarse a la vez ya que la frecuencia de operacin del Clk es alta y remotamente se tendrn dos o ms botones en el mismo instante, para mantener una operacin estable del sistema se le asignan indistintamente el valor del estado prximo. La asignacin de valores a los estados puede ser al azar como en la tabla 1:Q1Q0

CL00

FA01

FB10

FC11

Tabla 2. Tabla de estados.Despus de obtener las entradas y salidas, los flip flops y los estados se procede a realizar la programacin en ABEL-HDL. El archivo en formato ABEL-HDL de este sistema secuencial se presenta a continuacin en la figura 4.

Figura 4. Programacin en ispLever.Archivo Reporte Este archivo se genera como resultado de la compilacin (figura 5).

Figura 5. Equations obtenido por el ispLever.Tambin obtuvimos el chip diagram que es el diagrama esquemtico de nuestro GAL22V10, usado en esta prctica y se muestra en la figura 6.Figura 6. Diagrama esquemtico del GAL con sus entradas y salidas.Ya que se tuvo todo lo anterior, pasamos a implementar nuestro circuito sobre la tabla de conexiones en el cual tambin construiremos un generador de pulsos utilizando un circuito integrado SN7414, podemos ver el diagrama esquemtico del generador en la figura 7, la salida de la terminal 2 del SN7414 fue conectado a la terminal 1 del GAL22V10.

Figura 7. Generador de pulsos.RESULTADOSEn la figura 8 se muestra nuestro circuito en fsico en el protoboar, el cual fue el que se presento el da de la entrega de la prctica 9. Figura 4. Circuito de la practica 9 en fsico.Se batallo un poco con la programacin de nuestro diseo secuencial, pero al final se logro obtener el funcionamiento correcto para nuestra presentacin de esta prctica la cual fue la opta para esta prctica.CONLUSIONESDe conclusin podemos decir que se batallo un poco para entender la forma de hacer que se pudiera encender los led al oprimir los push botn, ya que se tena que hacer a conforme la velocidad de la seal del generador de impulso.BIBLIOGRAFAhttp://jagarza.fime.uanl.mx/general/paginas/Laboratorio.htm