PROYECTOS EN VHDL PARA CONTROL DE … · Generación de texto con memoria ROM (3) ... LÍNEA 1...

Transcript of PROYECTOS EN VHDL PARA CONTROL DE … · Generación de texto con memoria ROM (3) ... LÍNEA 1...

PROYECTOS EN VHDL PARA CONTROL

DE MONITOR VGA DESDE UNA FPGA

Sergio Noriega 2017

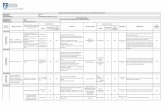

TABLA DE CÓDIGOS ASCII

Internacionalmente se

estandarizó un código para

para la representación de

caracteres visibles para su

visualización y otros no

visibles a modo de control. Se denominó ASCII (American Standard Code for Information Interchange), cuya tabla

contiene 128 caracteres.

Existe un «addendum» de

de este código que incluye

caracteres de otros idiomas

como el español con vocales

con acento, la letra ñ, etc.

Se denomina código ASCII

extendido.

Timming para generación de señales en VGD 640 x 480 60 Hz

AREA VISIBLE

640 16 96 48 33

2

10

4

80

señal de sincronismo horizontal se

ña

l d

e s

incro

nis

mo v

ert

ica

l 1

0

1

0

800 pixeles

52

5 lín

ea

s

PLACA TERASIC MODELO DE0 CON CYCLONE III

Conector DB15 para salida VGA

Pulsador Button1

PLACA TERASIC MODELO DE0 CON CYCLONE III

3 conversores DAC implementados cada uno con 4 salidas digitales y una red

de 6 resistencias.

GND

PLACA TERASIC MODELO DE0 CON CYCLONE III

Se requiere reloj

de 25,175 MHz.

PLACA TERASIC MODELO DE0 CON CYCLONE III

GENERADOR DE SINCRONISMO

+ CONTROL DE MEMORIA

+ PROCESAMIENTO DE STRINGS

ASCII ROM

DIV. DE

FREC. (PLL)

CLK

50MHZ

CLK

25.170MHZ

Fout = Fin x M/N

Fin Fout

Diagrama en bloques del proyecto final

Salida

VGA

syn

c

R

GB

botton1

Fout = Fin x M/n

Fin Fout

Uso de PLL de Cyclone III como divisor fraccional

1007

2000

Configuración de PLL en Cyclone III como divisor fraccional

Configuración de PLL en Cyclone III como divisor fraccional

Configuración de PLL en Cyclone III como divisor fraccional

Configuración de PLL en Cyclone III como divisor fraccional

Mejor aproximación

a 25,175 MHz

M

n

Fin

Fout

PROYECTO GENERADOR_VGA1 Generación de fondos a color

Instanciación del PLL

Basado en https://eewiki.net/pages/

viewpage.action?pageId=15925278

PROYECTO GENERADOR_VGA1

Cada vez que se pulsa button1 se

genera un cambio en el color del

fondo (background).

PROYECTO GENERADOR_VGA1

En esta sección se

generan las señales de

sincronismo para los

trazados horizontal y

vertical.

Esto corresponde para

el formato de 640x480,

respectivamente.

El campo total es de

800x525 pixeles.

CÓMO SE PUEDE

MODIFICAR PARA

OTROS FORMATOS

COMO 1024x768 ??

address(10..4)

address(3..0)

q(7..0)

ascii_rom

clock

00000000,

00000000,

00000000,

00010000,

00111000,

01101100,

01000100,

01000100,

01111100,

01000100,

01000100,

01000100,

01000100,

00000000,

00000000,

00000000,

ascii_rom es una memoria de 2048 x 8 bits.

Almacena 128 caracteres según el código ASCII.

Cada carácter ocupa 16 direcciones de 8 bits cada una.

En total se usan 128 bits ó pixeles por caracter.

Ejemplo:

El carácter «A» está almacenado en 16 posiciones

de memoria desde la 104010 hasta la 105510.

1040 equivale a 65 x 16, donde 65 es el código

ASCII asignado e indica el comienzo de la zona de

16 x 8 pixeles donde es almacenado ese carácter.

El carácter «B» le sigue, desde la posición 1056 a 1071.

Se usa para apuntar

al comienzo de la zona

donde se almacenan los

pixeles de un carácter.

Se usa para seleccionar

uno de los 16 bytes que

forman un caracter.

MEMORIA ROM CON CARACTERES ASCII

MEMORIA ROM CON CARACTERES ASCII

MEMORIA ROM CON CARACTERES ASCII

Memoria de 2048 registros

de 8 bits cada uno.

Almacena 128 caracteres.

Cada carácter está

almacenado en 16

direcciones contiguas,

requiriendo 128x16=2048

direcciones en total.

MEMORIA ROM CON CARACTERES ASCII

MEMORIA ROM CON CARACTERES ASCII

PROYECTO GENERADOR_VGA2 Generación de texto con memoria ROM (1)

Se llena la pantalla del carácter "I"

accediendo a la memoria ascii_rom_vga

PROYECTO GENERADOR_VGA3 Generación de texto con memoria ROM (2)

Se llena la pantalla de un carácter desde

la letra "A" hasta la "Z" cada vez que se

pulsa el botón button1 de la placa.

PROYECTO GENERADOR_VGA4

Generación de texto con memoria ROM (3)

Generación de texto en pantalla con resolución de 640 x 480 pixeles.

Cada carácter de 16 bits (pixeles) de alto x 8 bits (pixeles) de ancho.

El mismo consta de mensajes que están almacenados en la FPGA.

Capacidad de visualización de hasta 30 mensajes (30x16=480) de 80 caracteres cada

uno por pantalla (80x8=640).

Cada mensaje se almacena en la FPGA, escrita en VHDL como una constante formada

por un «string» de 80 caracteres.

Cada línea dura 16 barridos en horizontal. En cada barrido se visualiza uno de

los 16 bytes que forman a cada caracter.

Al iniciar una nueva línea un contador de caracteres (carácter_counter) se va

incrementando cada 8 pixeles que es el ancho que dura cada carácter en horizontal.

Este contador, junto con la función «character’pos» da el valor de código ASCII del

carácter que es apuntado en el «string» que se está leyendo.

Por otro lado, hay un contador que durante toda una línea, cuenta la posición vertical

desde 0 hasta 15, para direccionar uno de los 16 bytes que conforman a cada carácter.

Recordar que los caracteres están almacenados en una memoria ROM donde cada carácter

está formado por 128 bits: 16 de alto x 8 de ancho, donde en este proyecto, un bit es

equivalente a un pixel.

Cada carácter se direcciona con address(10..4) mientras que cada byte de un carácter se

direcciona con addresss(3..0).

Línea 1

Línea 30

A M

Carácter 1 Carácter 80

16

8

0,0

639,479

Display 640 x 480 pixeles

PROYECTO GENERADOR_VGA4 Generación de texto con memoria ROM (3)

PROYECTO GENERADOR_VGA4

Configuración del posicionamiento y

selección de los mensajes a visualizar

PROYECTO GENERADOR_VGA5 Generación de texto con memoria ROM (4)

Proyecto igual a «generador_vga4» con la adición de cambio de fondo de

pantalla presionando el pulsador «button1» (Proyecto: ‘generador_vga1’)

Señal de 3 bits => 8 colores.

Controlador para Módulo LCD 2x16

Sergio Noriega 2017

Módulo Display de caracteres LCD modelo 162F de Displaytech

HD44780

Este módulo permite visualizar en dos líneas hasta 16 caracteres en cada una, comandado desde un microprocesador. Generalmente se emplean 11 líneas entre control (3) y datos (8), pudiendo bajar a 7 si hay restricción en la cantidad de pines a emplear (configura el bus de datos en 4 bits).

El control de la visualización de los 2000 puntos del display y la interface a micro- procesador, la realiza básicamente este chip de la empresa Hitachi. Otro IC es el ST7066U, el cual es similar al HD44780. DDRAM: "Data Display RAM" donde se almacenan los caracteres cargados para ser visualizados. CGRAM: "Character Generator RAM" donde se puede almacenar algunos caracteres definidos por el usuario que no figuren en la ROM del chip para ser visualizados.

HD44780

Pines para uso en modo bus de datos de 4 bits

Adición para uso en modo bus de datos de 8 bits La parte alta del bus de datos es bidireccional (DB7..DB4). Permite que se pueda leer el estado del dispositivo, por ej..

HD44780

El controlador tiene una memoria ROM con caracteres disponibles y algo de RAM para almacenar caracteres definidos por el usuario (CGRAM). Las dimensiones de cada carácter puede ajustarse a 5 x 8 pixeles ó 5 x 10 pixeles. En cada uno de ellos puede visualizarse en la parte inferior, un cursor (en la línea inferior). La selección del carácter se realiza escribiendo en el bus de datos el código ascii correspondiente.

HD44780

HD44780

Las señales "E", "R/-W" y "RS", son de entrada al módulo LCD, mientras que DB0 a DB7 son bidireccionales, en especial DB7 que puede leerse para saber si el módulo está ocupado realizando una operación interna. En esta figura se muestra como se transmiten datos sólo por DB7 a DB4 en la modalidad de bus de 4 bits. Esto permite ahorrarse 4 líneas en total.

HD44780 Con R/-W en "0", se escribe a través del bus de datos (DB7 a DB0 ó DB7 a DB4) y dependiendo de la línea RS se avisa al controlador si es una instrucción (RS="0") o un dato (RS="1"). En la rutina de control es muy importante respetar los tiempos de reatrdo del controlador a fin de que funcione correctamente.

Este dispositivo (el display) es relativamente lento para acceder. Por ejemplo: una vez escrito un carácter se debe esperar 50 us para volver a generar la rutina de mandar otro. Para esto, es útil emplear la opción de leer desde el mismo bus de datos del dispositivo si está o no ocupado (BUSY).

La frecuencia típica del oscilador del chip es de 270 KHz.

continúa

HD44780

Borrar dato en CGRAM ó DDRAM Leer dato desde CGRAM ó DDRAM

Códigos de algunas instrucciones:

Borrar todo display incluyendo la memoria.

Retornar puntero a fila 1 columna 1.

Incremento/decremento/estático

Apagar/prender el display Modos para desplazar el cursor o la información de una línea de carateres.

Ajuste de tamaño de carácter y cantidad de líneas (1 ó 2).

HD44780

HD44780

Como configurar el modo "desplazamiento" (shift function), tamaño de carácter y cantidad de líneas a visualizar (set function).

Modos de visualización de cada carácter + cursor y posibilidad de hacer "blinking" (parpadeo).

Modos de lectura ó escritura de memorias DDRAM y CGRAM.

HD44780

Rutina normal de Inicialización del módulo display. El power-up debe ser mínimo de 40 ms (50 ms para asegurarse). La inicialización tarda unos 2.2 ms (3 ms para asegurarse).

HD44780

El chip es de tecnología CMOS. La entrada de ENABLE es normal, mientras que las de RS y R/-W son con pull-up. Los bits del bus de datos DB0 a DB7 son bidireccionales.

e rs r_nw

data7 . . . . data0

Controlador módulo

LCD

enable

reset

clock

busy

dato_in

CONTROLADOR DE MÓDULO LCD

E RS R/nW

DB7 . . . . DB0

MÓDULO LCD DISPLAYTECH

162F

UN POSIBLE DIAGRAMA DE FLUJO PARA EL CONTROL DEL MÓDULO LCD

Power Up

(Pwup)

Iniciali zación (Ini)

reset=0

Listo (Ready)

Envío (Send)

reset=0

reset=0 50 ms

2,2 ms

50 us enable=1

enable=0

X

X

Por defecto al encender el módulo, éste se configura como: FUNCTION SET : 2-line mode, display on. DISPLAY ON/OFF : display on, cursor off, blink off. ENTRY MODE SET : increment mode, entire shift mode.

Una vez inicializado el LCD, se procede a escribir los datos, usando el bucle: READY -> SEND -> READY …..

e n V H D L . 2 0 1 7

= 65h = 6Eh = 20h = 56h = 48h = 44h = 4Ch = 60h = 20h = 32h = 30h = 31h = 37h

S e m i n a r i o M i c r o

= 53h = 65h = 6Dh = 69h = 6Eh = 61h = 72h = 69h = 6Fh = 20h = 4Dh = 69h = 63h = 72h = 6Fh

LÍNEA 1 LÍNEA 2 LÍNEA 1

LÍNEA 2

Ejemplo de escribir un texto en dos líneas:

Seminario Micro

en VHDL. 2017

LÍNEA 1

LÍNEA 2

Tiempo: 00:00:00

RELOJ CON DISPLAY LCD

Hs Ms Ss Se emplea la placa DE0 de la Cyclone III, la cual posee una salida para comunicación con un display del tipo LCD. Pines empleados: E, RW, RS, Data7…Data0. Se visualiza en el display: Unidades y decenas de Horas. Unidades y decenas de Minutos. Unidades y decenas de Segundos. El circuito de alimenta con un reloj de 50 Mhz y posee dos resets: uno para el display (But1) y otro para el reloj (But0). Además hay una entrada para habilitar o detener el conteo del reloj (But2).

But2 But1 But0

RELOJ CON DISPLAY LCD

RELOJ CON DISPLAY LCD

RELOJ CON DISPLAY LCD

RELOJ CON DISPLAY LCD

RELOJ CON DISPLAY LCD

Disposición de pines en placa DE0 (Cyclone III)