Tesis Poryecto Inversor Pwm

-

Upload

patrocinio-vazquez -

Category

Documents

-

view

95 -

download

3

Transcript of Tesis Poryecto Inversor Pwm

PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE ESCUELA DE INGENIERIA

DISEÑO Y CONSTRUCCIÓN DE UN INVERSOR TRIFÁSICO MULTINIVEL

FELIPE EDUARDO RÍOS DÍAZ

Memoria para optar al título de Ingeniero Civil Industrial, con Diploma en Ingeniería Eléctrica

Profesor Supervisor: JUAN W. DIXON ROJAS

Santiago de Chile, 2003

PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE ESCUELA DE INGENIERIA Departamento de Ingeniería Eléctrica

DISEÑO Y CONSTRUCCIÓN DE UN INVERSOR TRIFÁSICO MULTINIVEL

FELIPE EDUARDO RÍOS DÍAZ

Memoria presentada a la Comisión integrada por los profesores:

JUAN DIXON R.

ÁNGEL ABUSLEME H.

JOSÉ RODRÍGUEZ P.

Para completar las exigencias del título de Ingeniero Civil Industrial, con Diploma en Ingeniería Eléctrica

Santiago de Chile, 2003

A mi Familia, especialmente a mis Padres, Hermanos y Novia, que siempre creyeron y confiaron en mí.

ii

AGRADECIMIENTOS

Quiero agradecer a mi Familia por el apoyo brindado en todo sentido durante estos años de estudio. Gracias por su paciencia y amor.

Mención especial merece el profesor Juan Dixon por su guía y apoyo en este interesante proyecto que hemos emprendido juntos.

No puedo dejar de lado a mi Novia y amigos que siempre estuvieron ahí cuando más lo necesitaba. Gracias.

Agradezco también la disposición y ayuda de los funcionarios del departamento de ingeniería eléctrica, que brindaron su apoyo incondicional en todo momento. Entre ellos menciono a Eduardo Cea, Betty Andonaegui, Elena Garrido, Sra. Virginia Meza y don Carlos Álvarez.

iii

INDICE GENERAL

Pág.

AGRADECIMIENTOS ................................................................................................ iii

INDICE DE TABLAS ................................................................................................. vii

INDICE DE FIGURAS..................................................................................................ix

RESUMEN...................................................................................................................xvi

ABSTRACT............................................................................................................... xvii

I. INTRODUCCIÓN.................................................................................................1 1.1. Los Inversores Multinivel .............................................................................2

1.1.1. Inversor Acoplado por Diodos (Diode-Clamped Inverter).................5 1.1.2. Inversor Acoplado por Capacitor (Capacitor-Clamped Inverter).......8 1.1.3. Inversor con Puentes “H” en Cascada (Cascade H-Bridges

Inverter) ............................................................................................11 1.2. Los inversores Multinivel versus otros tipos de inversores ........................18 1.3. Objetivos de la memoria .............................................................................22

II. CARACTERÍSTICAS DE UN INVERSOR DE CUATRO ETAPAS Y OCHENTA Y UN NIVELES. .............................................................................24 2.1. Introducción ................................................................................................24 2.2. Características del Prototipo .......................................................................30 2.3. Control del Inversor ....................................................................................33 2.4. Aplicaciones del Inversor Multinivel Construido.......................................35

III. SIMULACIONES DEL INVERSOR CONSTRUIDO .......................................39

IV. DISEÑO Y CONSTRUCCIÓN DEL PROTOTIPO...........................................48 4.1. Introducción ................................................................................................48

4.1.1. Elección de Semiconductores y Circuito de Disparo .......................49 4.1.2. Características Técnicas del Prototipo..............................................50

4.2. Diseño Térmico Circuito de Potencia .........................................................52

iv

4.2.1. Diseño Térmico del Disipador..........................................................52 4.2.2. Diseño y Construcción del Disipador ...............................................54

4.3. Diseño y Construcción de la Tarjeta del Inversor.......................................56 4.4. Diseño y Construcción de las Fuentes DC de los Esclavos ........................61

4.4.1. Diseño y Construcción de las Fuentes ..............................................62 4.4.2. Diseño Térmico de las Fuentes.........................................................66

4.5. Distribución de Componentes .....................................................................66

V. RESULTADOS EXPERIMENTALES ...............................................................72 5.1. Introducción ................................................................................................72 5.2. Tensiones de salida del inversor de 81 niveles ...........................................72 5.3. Corrientes de salida del inversor de 81 niveles...........................................75

VI. CONCLUSIONES Y TRABAJO FUTURO .......................................................79

BIBLIOGRAFÍA...........................................................................................................81

Anexo A: Lista de Componentes Principales Utilizados en la Construcción del Inversor. ...............................................................................................................86

Anexo B: Programa de Control del Inversor ................................................................89

Anexo C: Diseño de las Fuentes DC por medio de Reguladores de Voltaje ..............101

Anexo D: Cálculo de los Transformadores de las Fuentes DC...................................108

Anexo E: Hoja de Datos Mosfet IRF 540 ...................................................................124

Anexo F: Hoja de Datos Mosfet IRFP 250 .................................................................127

Anexo G: Hoja de Datos Driver IR 2113....................................................................131

Anexo H: Hoja de Datos Optocupla 6N 137...............................................................135

Anexo I: Hoja de Datos Regulador LM 78XX ...........................................................140

Anexo J: Hoja de Datos Regulador LM 317...............................................................144

v

Anexo K: Hoja de Datos Regulador LM 338 .............................................................148

Anexo L: Hoja de Datos Negador 74LS04 .................................................................152

Anexo M: Cálculo de Temperaturas ...........................................................................155

Anexo N: Consideraciones Tarjeta de dISPARO .......................................................167

Anexo O: Detalle de la Distribución de Componentes y Conexiones Eléctricas .......171

Anexo P: Detalle de la Construcción del Disipador de Potencia................................177

vi

INDICE DE TABLAS

Pág.

Tabla 1.1: Voltaje de salida para cada conmutación.....................................................13

Tabla 1.2: Voltajes y correspondientes estados de los semiconductores de un Inversor Puente “H” Acoplado por Diodos de 5 Niveles ....................................14

Tabla 1.3: Voltajes y correspondientes estados de los semiconductores de un Inversor Acoplado por Capacitor de 5 Niveles ...................................................15

Tabla 1.4: Voltaje de salida para Vdc1 = Vdc2 = E ....................................................20

Tabla 1.5: Voltaje de salida para Vdc1 = 2*Vdc2 = 2E ...............................................20

Tabla 1.6: Voltaje de salida para Vdc1 = 3*Vdc2 = 3E ...............................................20

Tabla 1.7: Voltaje de salida para Vdc1 = 4*Vdc2 = 4E ...............................................20

Tabla 2.1: Tabla de estado de los puentes para obtener todos los voltajes. ..................34

Tabla 4.1: Voltajes, Corriente continua media, y Potencias Aparentes de cada puente...................................................................................................................49

Tabla 4.2: Características de los reguladores usados....................................................62

Tabla 4.3: Diseño térmico de los reguladores...............................................................66

Tabla 5.1: Resumen de las bobinas empleadas en las pruebas .....................................75

Tabla A.1: Componentes necesarios para el inversor ...................................................86

Tabla C.1: Valores de las resistencias para las distintas fuentes. ...............................104

Tabla C.2: Resumen de resistencias y rangos de voltaje ............................................105

Tabla D.1: Resumen de los transformadores ocupados ..............................................122

vii

Tabla M.1: Resumen de los datos para calcular la potencia disipada.........................156

Tabla M.2: Resumen de los valores obtenidos. ..........................................................156

Tabla M.3: Resumen de los valores obtenidos prácticamente. ...................................158

Tabla M.4: Resumen de los valores obtenidos para el regulador de 21V...................163

viii

INDICE DE FIGURAS

Pág.

Figura 1.1: Esquema de un Inversor de (a) dos niveles, (b) tres niveles y (c) m niveles. ...................................................................................................................3

Figura 1.2: Ejemplo de una onda de voltaje multinivel, usando 11 niveles ...................4

Figura 1.3: Inversor tipo Acoplado por Diodos de m niveles.........................................5

Figura 1.4: Configuración de un Inversor Acoplado por Diodos de 3 niveles. ..............6

Figura 1.5: Inversor tipo Acoplado por Capacitor de m niveles.....................................8

Figura 1.6: Configuración de un Inversor Acoplado por Capacitor de 3 niveles. ..........9

Figura 1.7: Puente “H” Generalizado, con n fuentes y m = 2n+1 niveles. ...................11

Figura 1.8: Configuración de un puente “H” de tres niveles. .......................................12

Figura 1.9: Configuración de un Puente “H” Acoplado por Diodos de 5 niveles. .......13

Figura 1.10: Configuración de un Inversor Puente “H” Acoplado por Capacitor de 5 niveles. .........................................................................................................14

Figura 1.11: Formación de una onda de voltaje en un Inversor Multinivel del tipo puentes “H” en cascada de 9 niveles (4 etapas). ..........................................16

Figura 1.12: Salida de un Inversor PWM de dos Niveles.............................................18

Figura 1.13: Esquema de un inversor multinivel usando sólo dos puentes “H”...........19

Figura 2.1: Inversor de tipo puentes “H” en cascada, de 4 etapas y 81 niveles (una fase). ............................................................................................................25

Figura 2.2: Frecuencias de conmutación de los 4 puentes en el inversor de 81 niveles. .................................................................................................................26

ix

Figura 2.3: Comparación de ondas de salida de inversores de 3, 11, 21, 31 y 81 niveles. .................................................................................................................27

Figura 2.4: El efecto de la modulación por amplitud....................................................28

Figura 2.5: Esquema de un inversor con transformadores de salida.............................29

Figura 2.6: Distribución de potencias para una carga puramente resistiva (Cosϕ=1)..............................................................................................................30

Figura 2.7: Distribución de potencias para distintitas frecuencias en un motor de inducción de 20 kW por fase. ..............................................................................32

Figura 2.8: Esquema de una fuente DC-DC bidireccional............................................32

Figura 2.9: Esquema del Puente “H” usado. .................................................................35

Figura 2.10: Sistema para alimentar motores con fuentes independientes. ..................36

Figura 2.11: Sistema para alimentar motores con fuentes DC-DC bidireccionales. ....................................................................................................37

Figura 2.12: Diagrama de un motor con bobinas independientes.................................38

Figura 3.1: Modulación de voltaje de los cuatro puentes “H” del inversor multinivel.............................................................................................................39

Figura 3.2: Formación de la onda de voltaje alterna del inversor de 81 niveles...........40

Figura 3.3: Corrientes de los puentes “H” para una carga (a) resistiva e (b) inductiva. .............................................................................................................41

Figura 3.4: Corrientes de salida del inversor para una carga (a) resistiva e (b) inductiva. .............................................................................................................42

Figura 3.5: Diagrama en PSIM de los inversores usados para las simulaciones. ........43

x

Figura 3.6: Voltajes de Salida de los Inversores; en rojo: PWM; en azul 81 niveles. .................................................................................................................44

Figura 3.7: Corrientes de Salida de los Inversores PWM (arriba) y Multinivel (abajo). .................................................................................................................45

Figura 3.8: Modelo del motor de inducción utilizado para las simulaciones. ..............46

Figura 3.9: Formas de onda generadas por el inversor multinivel: a) voltaje y corriente del motor de inducción, b) potencia del motor en una fase..................46

Figura 3.10: Formas de onda generadas por el Inversor PWM: a) voltaje y corriente del motor de inducción, b) potencia del motor en una fase..................47

Figura 4.1: Diagrama de las Actividades Realizadas....................................................48

Figura 4.2: Perfil de sección rectangular usado como disipador. .................................50

Figura 4.3: Modelo térmico. .........................................................................................53

Figura 4.4: Diseño de uno de los Puentes “H”..............................................................55

Figura 4.5: Esquema de conexiones entre disipadores de una fase. .............................55

Figura 4.6: Fotografía del sistema disipador terminado, para una fase. .......................56

Figura 4.7: Esquema de un puente “H” con sus circuitos de disparo. ..........................57

Figura 4.8: Configuración del “driver” IR2113 para dos transistores. .........................57

Figura 4.9: Circuito de Disparo con aislamiento mediante optocuplas. .......................58

Figura 4.10: Tarjeta de disparo para un par de MOSFETs. ..........................................59

Figura 4.11: Tarjeta de disparo para una Fase. .............................................................60

Figura 4.12: Foto de la Tarjeta de disparo ya instalada en el Disipador de Potencia ...............................................................................................................61

xi

Figura 4.13: Esquema de las Fuentes DC para cada Esclavo. ......................................63

Figura 4.14: Tarjeta de las fuentes DC. ........................................................................64

Figura 4.15: Fotografía de la tarjeta de las fuentes antes de ser armada. .....................64

Figura 4.16: Fotografía de la tarjeta de las fuentes ya terminada. ................................65

Figura 4.17: Vista en planta del prototipo completo.....................................................67

Figura 4.18: Fotografía del Sistema Completo. ............................................................68

Figura 4.19: Fotografía del Sistema Completo desde distintas Vistas..........................69

Figura 4.20: Fotografías del Inversor instalado en su estructura definitiva..................70

Figura 5.1: Voltaje de salida escalonado del inversor ..................................................72

Figura 5.2: Semiciclo positivo del Voltaje de Salida....................................................73

Figura 5.3: Detalle de los peldaños de la onda de voltaje alterna de salida..................74

Figura 5.4: Corriente y Voltaje de la carga R-L antes descrita.....................................76

Figura 5.5: Simulaciones de Corriente y Voltaje de la carga R-L antes descrita. ........76

Figura 5.6: Comparación cualitativa entre tecnología PWM y multinivel (81 niveles).................................................................................................................77

Figura A.1: Componentes ocupados en el Inversor. .....................................................87

Figura C.1: Esquema para las Fuentes de 5 y 15 Volts...............................................101

Figura C.2: Esquema del circuito R-C de los reguladores ajustables para los Esclavos. ............................................................................................................102

Figura C.3: Esquema del circuito R-C modificado de los reguladores ajustables......103

Figura C.4: Gráfico de la Corriente de Ajuste vs. Temperatura. ................................104

xii

Figura C.5: Esquema de las Fuentes DC para cada Esclavo.......................................105

Figura D.1: Circuito Simulado para la Fuente de 2,33 Volts (VAC = 10V). .............108

Figura D.2: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................109

Figura D.3: Circuito Simulado para la Fuente de 2,33 Volts (VAC = 9V). ...............110

Figura D.4: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................110

Figura D.5: Circuito Simulado para la Fuente de 7 Volts (VAC = 15V). ..................112

Figura D.6: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................112

Figura D.7: Circuito Simulado para la Fuente de 7 Volts (VAC = 15V). ..................113

Figura D.8: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................113

Figura D.9: Circuito Simulado para la Fuente de 21 Volts (VAC = 30V). ................114

Figura D.10: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................115

Figura D.11: Circuito Simulado para la Fuente de 21 Volts (VAC = 28V). ..............116

Figura D.12: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................116

Figura D.13: Circuito Simulado para la Fuente de 15 Volts (VAC = 15V). ..............117

Figura D.14: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................118

Figura D.15: Circuito Simulado para la Fuente de 5 Volts (VDCin = 15V). .............119

xiii

Figura D.16: a) Voltaje de Entrada del Regulador, b) Corriente de Entrada del Rectificador .......................................................................................................119

Figura D.17: Circuito Simulado para la Fuente de 5 y 15 Volts (VAC = 15V). ........120

Figura D.18: a) Voltaje de Entrada a los dos Reguladores (Rojo: 15 y Azul: 5), b) Corriente de Entrada del Rectificador...........................................................121

Figura M.1: Circuito térmico a resolver......................................................................157

Figura M.2: Curva Potencia disipada versus Temperatura .........................................158

Figura M.3: Esquema usado para las Fuentes DC ......................................................159

Figura M.4: Cálculo de RDA equivalente. .................................................................162

Figura M.5: Curva de Temperatura versus Potencia para calcular RDA....................164

Figura M.6: Disipadores Usados para las fuentes DC. ...............................................165

Figura N.1: Tarjeta Inversora para una Fase...............................................................167

Figura N.2: a) Disposición del MOSFET que será colocado en el Inversor b) Esquema de la forma de apoyar la tarjeta sobre el disipador ............................168

Figura O.1: Esquema de la Estructura de Aluminio usada. ........................................171

Figura O.2: Vista Superior de la disposición utilizada. ..............................................172

Figura O.3: Bornes para alimentación externa de los Maestros. ................................173

Figura O.4: Bornes para voltaje de salida alterno.......................................................174

Figura O.5: Esquema de conexión a la red eléctrica...................................................174

Figura P.1: Diseño de un Puente. ................................................................................177

Figura P.2: Esquema de la unión de perfiles para el disipador. ..................................178

xiv

Figura P.3: a) Materiales para un disipador b) Disipador Terminado ........................178

Figura P.4: Esquema de conexiones entre Disipadores. .............................................179

Figura P.5: Conexión de dos puentes en cascada........................................................180

Figura P.6: Esquema de conexiones entre Disipadores. .............................................181

Figura P.7: Esquema de circuito para calcular RDA. .................................................181

Figura P.8: Curva de Temperatura versus Potencia para calcular RTH. ....................182

xv

RESUMEN

Las técnicas de modulación PWM (Pulse-Width Modulation), usadas actualmente en casi todos los convertidores estáticos, como compensadores de reactivos, accionamientos para máquinas eléctricas, rectificadores de cuatro cuadrantes o filtros activos de potencia, no generan una onda de voltaje y corriente perfectas. Una de las principales causas de este efecto es la frecuencia de conmutación a la que trabajan los semiconductores.

Los inversores multinivel son inversores de última tecnología que pueden generar corrientes o incluso voltajes sinusoidales con mucho menor contenido armónico. Si el número de niveles es lo suficientemente alto, se puede obtener un voltaje (o corriente) casi perfecto. Más aún, se puede modular en amplitud en vez de ancho de pulso (PWM), por lo que las pérdidas generadas por las armónicas de corriente pueden ser eliminadas. Además, la frecuencia de conmutación y el nivel de potencia de los semiconductores se reducen considerablemente. Dentro del contexto de utilizar los inversores multinivel para obtener un bajo contenido armónico, se diseñó y construyó un inversor trifásico de 81 niveles para controlar motores de corriente alterna. Este inversor consta de cuatro puentes (un Maestro, y tres Esclavos), con sus voltajes escalados en potencia de tres, lo que permite obtener el elevado número de niveles ya mencionado.

El inversor diseñado es capaz de manejar corrientes de aproximadamente 14 A por fase, con un voltaje de salida de 66 Vaceff, dando una potencia nominal de casi un kVA por fase. Para llevar a cabo este proceso, se tuvo que diseñar un sistema de potencia muy compacto con inversores individuales aislados galvánicamente, con sus sistemas de control de encendido y fuentes de alimentación independientes.

En síntesis, en esta Memoria se describe el proceso de diseño y fabricación de un inversor trifásico multinivel. Una vez terminado y probado, satisfizo todos los requerimientos especificados.

xvi

ABSTRACT

PWM techniques used today to control modern static converters such as machine drives, power factor compensators or active power filters, do not yield perfect waveforms, which strongly depend on switching frequency of the power semiconductors.

Multilevel converters are a state-of-the-art converter technology, its way of operation allows having almost perfect currents, and very good voltage waveforms, eliminating most of the undesirable harmonics. If the number of levels is high enough, the voltage (o current) waveform become almost perfect. Even more, multilevel converters work more like amplitude modulation rather than pulse modulation, and this fact makes the outputs of the converter very much cleaner. Also, the switching frequency and power level of each semiconductor are reduced. In the context of using multilevel converter to obtain low harmonic contamination, a 81-level converter prototype was designed to operate a three phase motor drive. This converter has four bridges or stages (one Master and three Slaves), with its dc supplies scaled with levels of voltage in power of three, to obtain the 81-level.

The converter designed is able to handle currents of 14 A per phase, with an ac voltage output of 66 Vaceff, thus yields a 1 KVA of nominal power per phase. To put into practice this converter, a compact design is necessary, with four independent “H”-bridge converters, their control systems and independent dc power supplies.

In this work, the process of design and implementation of a three-phase multilevel converter, is described. The work has been satisfactorily ended, and laboratory experiments have demonstrated the excellent characteristics of this type of converter.

xvii

1

I. INTRODUCCIÓN

La técnica de modulación PWM (Pulse-Width Modulation) usada actualmente en los convertidores estáticos, no entrega ondas limpias. Esta suciedad es causada por las armónicas que producen las altas frecuencias de conmutación de los semiconductores. Así, voltajes y corrientes no son los esperados. Esto significa que existe contaminación producto de armónicas, pérdidas adicionales, rizado en la corriente y gran cantidad de ruido que puede a llegar a contaminar los sistemas de control [1]. Esto ha llevado a muchas investigaciones en el campo de la modulación PWM [2, 3, 4, 5].

Los convertidores estáticos actuales, aplicados al control de motores eléctricos, emplean un sistema de rectificación - inversión para manejar la frecuencia y el voltaje. Daños y fallas en los motores han sido denunciados por la industria debido a las altas frecuencias PWM de los inversores. Los principales problemas denunciados son “fallas en los rodamientos del motor” y “pérdida de la aislación en las bobinas del motor” causadas por corrientes circulantes, desgaste dieléctrico, sobretensión y descargas corona [6, 7, 8]. Las corrientes circulantes son generadas por capacidades parásitas que se generan en las distintas capas de las bobinas del motor. Los bruscos cambios de voltaje (dV/dt) inducen corrientes y descargas corona en las bobinas del motor lo que provoca su desgaste prematuro. Otro punto negativo del control PWM actual es la eficiencia, debido a las pérdidas por conmutación de los semiconductores por las altas frecuencias con las que operan.

La función principal de los convertidores multinivel es mejorar la onda de voltaje alterno generada, usando diferentes niveles de voltaje continuo. Su funcionamiento es tal que, al aumentar el número de niveles, el voltaje de salida, que está formado por escalones de tensión, tiene mayor resolución porque aumenta el número de escalones, acercándose a una onda sinusoidal con mayor precisión. A mayor cantidad de escalones (o niveles) en la onda de salida, menos distorsión armónica tiene la onda.

Los convertidores multinivel, diseñados para generar un gran número de niveles, pueden trabajar con las técnicas convencionales de PWM, pero además

2

pueden ser modulados en amplitud, lo que produce salidas mucho más limpias. Este método de operación permite obtener muy buenas ondas de voltaje y corriente, eliminando la mayoría de las indeseadas armónicas. Mejor aún, cada puente del convertidor funciona a baja frecuencia de conmutación, lo cual da la posibilidad de poder trabajar con semiconductores de menor velocidad, generando menos pérdidas por conmutación y haciendo más eficiente el convertidor estático. Estas características han dado pie a numerosas investigaciones en este campo, entre las cuales está el trabajo realizado en esta memoria.

otores eléctricos, filtros activos de potencia y rectificadores de cuatro cuadrantes.

rtidores PWM convencionales, pueden controlar flujos de potencia activa y reactiva.

esidad de contar con fuentes de tensión independientes para cada puente inversor.

1.1. Los Inversores Multinivel

e salida alterno, con niveles de tensión escalonados utilizando Inversores Multinivel.

de los semiconductores permiten la suma o resta de las distintas fuentes de voltaje

Por estas razones, los inversores multinivel están siendo investigados en los últimos años por sus ventajas en la calidad de las ondas de voltaje y corriente, por sus bajas pérdidas de conmutación y por su capacidad de trabajar en alto voltaje. Algunas aplicaciones de los inversores multinivel incluyen compensadores de reactivos, control de velocidad en m

Además, los inversores multinivel pueden ser usados para enlazar sistemas de distinta frecuencia y enlazar tensiones de corriente continua con tensiones alternas de cualquier frecuencia. También, y al igual que los conve

Las principales desventajas de este tipo de tecnología son la gran cantidad de semiconductores requeridos y la nec

La función principal de los inversores es generar un voltaje alterno a partir de una fuente de voltaje continua. Ahora, si esa fuente de voltaje continua se dividiese en varias fuentes de menor valor, sería posible generar un voltaje d

Los inversores multinivel, incluyen un arreglo de semiconductores y fuentes de voltaje, para formar un voltaje de salida escalonado. Las conmutaciones

3

continuo, generando una onda de voltaje de amplitud variable. Así también, los semiconductores trabajan con voltajes más reducidos.

La Figura 1.1 muestra algunos diagramas esquemáticos de inversores con diferente número de niveles, en los cuales, la acción del semiconductor está representada por un interruptor ideal con distintas posiciones. Un inversor de dos niveles, como el mostrado en la figura 1.1(a), genera una salida de voltaje con dos valores (niveles) distintos, VC y Cero, con respecto al terminal negativo de la fuente (“0”), mientras que un módulo de tres niveles genera tres voltajes distintos a la salida (2·VC, VC y Cero), y así sucesivamente. Las distintas posiciones del interruptor ideal se implementan en la práctica con una cantidad de semiconductores que está en directa relación con el número de niveles.

0

Va

a

Vc

Vc

0

Va

aVc

(a) (b)0

Va

a...

Vc (1)

(c)

Vc (m-1)

Vc (m)

Figura 1.1: Esquema de un Inversor de (a) dos niveles, (b) tres niveles y (c) m niveles.

Como se dijo anteriormente, los inversores multinivel constan de pequeñas fuentes DC, las que son usadas para formar una onda AC escalonada que se parezca a la onda deseada. Por ejemplo, si se tienen diez fuentes DC de magnitudes iguales a 20 V cada una, se puede obtener una onda compuesta de 11 niveles (cinco positivos, cinco negativos y cero, con respecto a un punto intermedio entre las diez fuentes) que se aproxima a una onda sinusoidal de amplitud 100V como muestra la figura 1.2:

4

Figura 1.2: Ejemplo de una onda de voltaje multinivel, usando 11 niveles

Con esto se puede concluir, que a mayor número de niveles del inversor, mayor es la cantidad de niveles de la onda, obteniendo menor distorsión armónica.

Algunas características de los Inversores Multinivel son [15]:

a) Pueden generar voltajes de salida con muy poca distorsión y bajo dv/dt.

b) Las corrientes de entrada son de muy baja distorsión.

c) Generan pequeños voltajes de modo común, protegiendo los motores. Más aún, utilizando sofisticados métodos de modulación, el voltaje de modo común puede ser eliminado.

d) Pueden operar con baja frecuencia de conmutación.

5

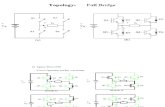

Para construir inversores multinivel como los mostrados en la figura 1.1, existen dos topologías principales que veremos a continuación: Inversor Acoplado por Diodos (Diode-Clamped Inverter) e Inversor Acoplado por Condensadores (Capacitor-Clamped Inverter).

1.1.1. Inversor Acoplado por Diodos (Diode-Clamped Inverter)

Este inversor, también conocido como inversor de punto neutro (NPC por sus siglas en inglés) consiste en una cadena de semiconductores en serie, en paralelo con una cadena de condensadores, también en serie. Los condensadores permiten generar una cadena de fuentes de tensión en serie a partir de una sola fuente continua de alimentación. Existe una unión con diodos entre estas dos cadenas, que conecta semiconductores superiores e inferiores tal como muestra la figura 1.3, para un convertidor de m niveles.

C (m -1 )

C (m -2 )

S a ´1

D a ´1

S a ´2

S a ´(m -2 )

S a ´(m -1 )

V d c

V d cm -1

S a 1

S a 2

S a (m -2 )

S a (m -1 )

C 1

C 2

.

.

.

.

.

.

.

.

D a (m -2 )

D a ´2

.

.

.

.

.

.

D a ´(m -3 )

D a ´(m -2 )

D a (m -3 )

D a 2

D a 1

V d cm -1

V d cm -1

V d cm -1

. . . .

. . . .

+

-

aC m /2

C (m -1 )/2

n

Figura 1.3: Inversor tipo Acoplado por Diodos de m niveles.

6

Una de las configuraciones más utilizadas con esta topología es la del inversor de tres niveles, mostrada en la figura 1.4. Como se dijo anteriormente, los condensadores actúan como fuentes DC, dividiendo el voltaje común en partes iguales. Así, en el diagrama de la Figura 1.4, cada condensador acumula ½Vdc pudiendo dar voltajes de salida de -½Vdc, Cero ó ½Vdc para Van. El punto medio n de los dos condensadores se puede definir como el punto neutro, donde puede retornar la carga.

S=

C1

C2

Sa1

Da1

Da´1

Sa2

Sa´1

Sa´2

Vdc

½Vdc

½Vdc

an

Figura 1.4: Configuración de un Inversor Acoplado por Diodos de 3 niveles.

Se puede apreciar que, los pares de semiconductores de la primera rama, es decir (Sa1 y Sa’1) y (Sa2 y Sa’2), son complementarios, así, cuando Sa1 está conduciendo (Sa1=1), Sa’1 está bloqueado (Sa’1=0), y así para Sa2 y Sa’2.

Este tipo de inversor tiene algunas desventajas. Suponiendo diodos iguales, el uso de diodos extras se transforma en impracticable si se quiere aumentar el número de niveles, requiriendo (m-1)*(m-2) diodos por rama [9]. Por ejemplo, en la Figura 1.3 el diodo Da2 requiere la conexión de dos diodos en serie ya que debe bloquear el voltaje de dos condensadores, y Da(m-2) requiere (m-2) diodos en serie para bloquear (m-2) voltajes de condensadores. Además, los condensadores no comparten la misma corriente de carga y descarga provocando un desbalance de voltaje en los condensadores en serie [10].

7

A continuación se presenta un resumen de las ventajas y desventajas de este tipo de topología [9]:

Ventajas:

• A mayor número de niveles, menor es la distorsión armónica.

• Todas las ramas comparten el mismo bus DC.

• El flujo de potencia Reactiva puede ser controlado.

• Alta eficiencia por la menor frecuencia de conmutación.

• El sistema de control es relativamente simple.

Desventajas:

• Cantidad excesiva de diodos: se requieren (m-1)*(m-2) por fase.

• El flujo de potencia Activa es complejo por el desbalance de los condensadores.

• Se requieren diferentes rangos de corriente para cada semiconductor debido a sus diferentes ciclos de operación.

8

1.1.2. Inversor Acoplado por Capacitor (Capacitor-Clamped Inverter)

Este inversor (conocido también como capacitor volante o “flying-capacitor”) tiene una estructura similar al inversor acoplado por diodos. Al igual que la topología de inversores acoplados por diodos antes descrita, los condensadores en serie actúan como fuentes DC, dividiendo el voltaje común en partes iguales. Sin embargo, esta topología permite mayor flexibilidad en la formación de la onda sinusoidal y en el balance de voltaje en los condensadores en paralelo a Vdc. En la Figura 1.5 se presenta un inversor de m niveles con esta topología:

S a´1

S a´2

S a´(m -2)

S a´(m -1)

V dc

S a1

S a2

S a(m -2)

S a(m -1)

.

.

.

.

.

.

C a1C a2C a(m -3)C a(m -2)

… … … ..

… … … ..

+

-

an

C 1

C 2

Figura 1.5: Inversor tipo Acoplado por Capacitor de m niveles.

9

Análogamente como ocurre con el Inversor Acoplado por Diodo, el Inversor Acoplado por Capacitor requiere un gran número de condensadores para acoplar el voltaje. De esta forma, siempre que el rango de voltaje de cada condensador usado sea el mismo, un inversor de m-niveles requerirá un total de ½*(m-1)*(m-2) condensadores de acople por fase, además de 2 condensadores principales conectados a la barra DC.

La figura 1.6 ilustra un inversor multinivel Acoplado por Capacitor de 3 niveles.

Vdc

C1

C2

Sa1

Sa2

Sa´2

Sa´1

½Vdc

½Vdc

Ca1

S=an

Figura 1.6: Configuración de un Inversor Acoplado por Capacitor de 3 niveles.

A continuación se presenta un resumen de las ventajas y desventajas de este tipo de topología [9]:

10

Ventajas:

• A mayor número de niveles, los condensadores acumulan energía extra durante largos transitorios de descarga.

• Permite formas flexibles de disparar los semiconductores, para obtener un mejor balance de voltaje en los condensadores.

• A mayor número de niveles, menor es la distorsión armónica.

• Los Flujo de potencia Activa y Reactiva pueden ser controlados.

Desventajas:

• Requiere una cantidad excesiva de condensadores, pues se requieren ½*(m-1)*(m-2) por fase, y como son más grandes y caros que los diodos, resulta menos atractivo que el de acoplamiento por diodo.

• Un complejo sistema de control es necesario para mantener balanceados los voltajes de los condensadores.

• Presentan baja eficiencia para transmisión de flujo Real.

Una característica común de las dos tecnologías descritas anteriormente es que persiguen emular la topología básica mostrada en la figura 1.1. Esto es, un convertidor o inversor alimentado con voltajes iguales conectados en serie. La topología de acoplamiento por diodos lo logra manteniendo la cadena de condensadores ecualizada, en tanto que la topología de acoplamiento por condensadores lo hace manteniendo cargados los condensadores Cai a niveles de voltaje crecientes, de modo de emular el efecto de fuentes de alimentación en serie de igual voltaje. El problema con la topología básica de la figura 1.1 y sus correspondientes estructuras de implementación práctica, es que se limita el número de niveles a n+1, en donde n representa el número de fuentes de tensión conectadas en serie.

11

La limitación en el número de niveles mencionada anteriormente puede subsanarse utilizando dos estrategias topológicas combinadas: el Puente “H” y la conexión en cascada de estos mismos.

1.1.3. Inversor con Puentes “H” en Cascada (Cascade H-Bridges Inverter)

Se puede aumentar el número de niveles de las topologías anteriores sin hacer crecer el número de fuentes de voltaje, utilizando la estrategia de los Puentes “H”. Estos puentes se construyen utilizando dos inversores multinivel idénticos, de alguno de los tipos mostrados en la figura 1.1. Esto permite a la carga evitar el retorno directo hacia las fuentes de tensión continua y elevar el número de niveles de n+1 a 2n+1. Una configuración generalizada de un puente “H” como el mencionado se ilustra en la figura 1.7.

CARGA

Figura 1.7: Puente “H” Generalizado, con n fuentes y m = 2n+1 niveles.

12

El puente “H” más sencillo es aquél formado por ramas de dos niveles y una sola fuente, como el mostrado en la figura 1.8. Puede observarse que este puente genera tres niveles sin necesidad de contar con una fuente de tensión de punto medio. La configuración de este puente “H” se muestra en la figura 1.8.

Vdc

S1

S3

S2

S4

Vab

+

-

Figura 1.8: Configuración de un puente “H” de tres niveles.

El puente “H” de la Figura 1.8, genera tres voltajes de salida (Vab) diferentes, +VDC, 0 y –VDC, conectando el voltaje de entrada al de salida con diferentes combinaciones de los cuatro semiconductores S1, S2, S3 y S4. Para obtener +VDC, los semiconductores S1 y S4 se ponen en conducción (1), mientras que S2 y S3 están en estado de no conducción (0). Encendiendo los semiconductores S2 y S3 y apagando S1 y S4, se obtiene –VDC. Con las combinaciones S1 y S2 ó S3 y S4 en estado encendido se obtiene un voltaje de salida de amplitud Cero. Cualquier otra combinación no es permitida pues provocará un cortocircuito en la fuente DC del módulo.

El funcionamiento de este puente “H” se resume en la tabla 1.1, con estado uno (1) si el semiconductor está conduciendo, y cero (0) si no lo está:

13

Tabla 1.1: Voltaje de salida para cada conmutación

S1 S2 S3 S4 Vab

1 0 0 1 +VDC

1 1 0 0 0

0 0 1 1 0

0 1 1 0 -VDC

La figura 1.9 muestra un inversor Puente “H” de 5 niveles usando una de las topologías descritas anteriormente de puente Acoplado por Diodos.

C1

C2

Sa1

Da1

Da´1

Sa2

Sa´1

Sa´2

Vdc

½Vdc

½Vdc

Sb1

Db1

Db´1

Sb2

Sb´1

Sb´2

a bn VOUT

Figura 1.9: Configuración de un Puente “H” Acoplado por Diodos de 5 niveles.

Para controlar este Puente “H” (de cinco niveles) es necesario controlar los semiconductores como se muestra en la Tabla 1.2:

14

Tabla 1.2: Voltajes y correspondientes estados de los semiconductores de un Inversor Puente “H” Acoplado por Diodos de 5 Niveles

Sa1 Sa2 Sa’1 Sa’2 Sb1 Sb2 Sb’1 Sb’2 Vab 0 0 1 1 1 1 0 0 -Vdc 0 0 1 1 0 1 1 0 -½Vdc 1 1 0 0 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 1 ½Vdc 1 1 0 0 0 0 1 1 Vdc

El mismo puente “H” de cinco niveles puede implementarse también con la configuración de acoplamiento por capacitor que muestra la figura 1.10.

Vdc

C1

C2

Sa1

Sa2

Sa´2

Sa´1

½Vdc

½Vdc

Sb1

Sb2

Sb´2

Sb´1

a bn

Ca1 Cb1VOUT

Figura 1.10: Configuración de un Inversor Puente “H” Acoplado por Capacitor de 5 niveles.

Para controlar este inversor (de cinco niveles) es necesario controlar los semiconductores como se muestra en la siguiente tabla (Tabla 1.3):

15

Tabla 1.3: Voltajes y correspondientes estados de los semiconductores de un Inversor Acoplado por Capacitor de 5 Niveles

Sa1 Sa2 Sa’1 Sa’2 Sb1 Sb2 Sb’1 Sb’2 Vab 0 0 1 1 1 1 0 0 -Vdc 0 0 1 1 0 1 0 1 -½Vdc 0 1 0 1 1 1 0 0 -½Vdc 0 1 1 1 1 1 0 0 -½Vdc 1 1 0 0 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 0 1 1 ½Vdc 1 1 0 0 0 1 0 1 ½Vdc 1 0 1 0 0 0 1 1 ½Vdc 1 1 0 0 0 0 1 1 Vdc

Se puede apreciar que para generar la onda de salida, no se está obligado a seguir un patrón rígido, como es el caso del Inversor Puente “H” Acoplado por Diodo. El voltaje de salida puede ser formado usando diferentes combinaciones de conmutaciones. De hecho, las conmutaciones pueden ser elegidas para cargar o descargar los condensadores entre los semiconductores, lo que ayuda al balance de voltaje.

Otro paso adelante para aumentar aún más el número de niveles sin hacer crecer el número de fuentes de tensión independientes en forma desmesurada, es haciendo uso de una topología de Convertidores en Cascada, es decir, la aplicación combinada de inversores Puente “H”. La onda de salida del inversor se forma mediante arreglos de conmutación en el tiempo de varios puentes “H” conectados en cascada. Así, el voltaje de salida corresponde a la suma (o también diferencia) de los voltajes de cada uno de los módulos puente “H”.

Por ejemplo, la figura 1.11 muestra un inversor monofásico, compuesto por cuatro puentes “H” conectados en serie, y su respectiva onda de salida de voltaje, que está formada por la suma de los distintos voltajes generados por los cuatro

16

módulos del inversor. Puede observarse que la tensión de salida generada resulta de 9 niveles: cuatro positivos, cuatro negativos y cero.

Vdc

-4Vdc

4Vdc

Vac

Vdc

Vdc

Vdc

Vdc

Figura 1.11: Formación de una onda de voltaje en un Inversor Multinivel del tipo puentes “H” en cascada de 9 niveles (4 etapas).

Los inversores puentes “H” en cascada usan fuentes DC independientes para cada etapa, como se muestra en la Figura 1.11. Como se dijo anteriormente, la salida de cada puente “H” genera tres voltajes diferentes, que combinados con el resto de los puentes H, genera una onda de salida sinusoidal escalonada.

Las fuentes DC independientes de cada etapa pueden ser de dos tipos: iguales o escaladas. Un ejemplo de etapas con fuentes iguales (o no escaladas) fue presentado en la figura 1.11, donde cada puente “H” está alimentado por una fuente de igual magnitud. La opción de puentes con fuentes escaladas presenta la ventaja de

17

poder obtener una mayor cantidad de niveles. Por ejemplo, si las fuentes DC de la figura 1.11 fueran escaladas en potencias de dos, se obtendrían hasta 31 niveles de voltaje, si se opta por un escalonamiento en potencias de tres, se pueden obtener hasta 81 niveles. Sin embargo, el escalonamiento elegido para las fuentes no es al azar y requiere de un estudio previo que será presentado en la sección 1.3 de esta memoria.

A continuación se presenta un resumen de las ventajas y desventajas de este tipo de topología [9]:

Ventajas:

• Dado que cada puente tiene la misma estructura, permite la modularización de cada uno, lo que reduce tiempo y costo para quienes los construyan. Esto es válido para inversores con puentes “H” no escalados en voltaje. De otro modo, cada módulo es distinto.

• Requiere de menos componentes, ya que no se necesitan Diodos ni Condensadores en paralelo con los semiconductores.

• A mayor número de niveles, menor es la distorsión armónica.

• Los Flujos de potencia Activa y Reactiva pueden ser controlados.

Desventajas:

• La cantidad de Fuentes DC independientes (si se quiere controlar flujo Activo y Reactivo, esas fuentes deben ser Bidireccionales).

18

1.2. Los inversores Multinivel versus otros tipos de inversores

Hemos dicho que los inversores multinivel generan un bajo contenido armónico, lo que los hace muy apetecidos. Sin embargo, esa no es la única ventaja que tienen sobre los inversores tradicionales generalmente modulados en ancho de pulso (PWM).

Por ejemplo, los inversores de tensión utilizando ramas de dos niveles son los más usados para aplicaciones en media y baja potencia. Estos inversores tienen una forma de onda que dista mucho de ser sinusoidal (Figura 1.12) por lo que su contenido armónico es alto. Además, normalmente emplean frecuencias de conmutación del orden de los 10 KHz o más, con el objeto de generar ondas de corriente con poca distorsión armónica, lo que restringe su aplicación para grandes potencias debido a la lenta velocidad de operación de grandes semiconductores como el GTO y a las elevadas pérdidas por conmutación involucradas.

Vdc

-Vdc

VDC

Figura 1.12: Salida de un Inversor PWM de dos Niveles

Un inversor trifásico construido con la topología anterior permite tres niveles de voltaje en la tensión fase-neutro de la carga. Una mejora a lo anterior son

19

los inversores construidos con ramas de tres niveles, obteniéndose cinco niveles de voltaje en la carga en relación al neutro: +VDC, +½VDC, Cero, -½VDC y -VDC. Ello representa una mejora pero dista mucho de tener la capacidad de generar una onda sinusoidal sin la ayuda de la modulación PWM. Si el número de niveles puede llevarse a valores elevados manteniendo cierta simplicidad en la topología, entonces se puede pensar en modular en amplitud, dejando de lado el PWM. Aquí entonces aparece otra ventaja: baja frecuencia de conmutación para los semiconductores.

Como se dijo anteriormente, los inversores multinivel utilizando puentes “H” en cascada, pueden ocupar fuentes con voltajes iguales o escalados. Para ver la importancia que tiene la elección de estos voltajes, se hará un análisis sobre un puente en cascada de dos etapas (sólo dos puentes “H”), en función de los valores relativos de sus fuentes Vdc1 y Vdc2. El puente de dos etapas se muestra en la figura 1.13 y los resultados de este análisis, para diferentes escalamientos de voltaje, se muestran en las Tablas 1.4, 1.5, 1.6 y 1.7.

S1

S3

S2

S4

Vdc2

S1

S3

S2

S4

Vdc1

Vout = V1 + V2

V1

V2

Figura 1.13: Esquema de un inversor multinivel usando sólo dos puentes “H”.

20

Tabla 1.4: Voltaje de salida para Vdc1 = Vdc2 = E

Vout V1 V2 2E E E

E 0 E

0 E E -E 0 0 0 -E E -E 0

-E 0 -E

-2E -E -E

Tabla 1.5: Voltaje de salida para Vdc1 = 2*Vdc2 = 2E

Vout V1 V2 3E 2E E 2E 2E 0

2E -E E

0 E 0 0 0

-2E E -E

0 -E -2E -2E 0 -3E -2E -E

Tabla 1.6: Voltaje de salida para Vdc1 = 3*Vdc2 = 3E

Vout V1 V2 4E 3E E 3E 3E 0 2E 3E -E E 0 E 0 0 0 -E 0 -E -2E -3E E -3E -3E 0 -4E -3E -E

Tabla 1.7: Voltaje de salida para Vdc1 = 4*Vdc2 = 4E

Vout V1 V2 5E 4E E 4E 4E 0 3E 4E -E 2E - - E 0 E 0 0 0 -E 0 -E -2E - - -3E -4E E -4E -4E 0 -5E -4E -E

21

La tabla 1.4 muestra el caso en que Vdc1 = Vdc2 = E (inversor multinivel con tensiones no escaladas). Se puede apreciar que en este caso sólo pueden generarse cinco niveles: dos positivos, dos negativos y el cero. Además existe redundancia en la forma en que pueden generarse algunos niveles, como por ejemplo el “cero” que puede generarse de tres formas diferentes. Para la tabla 1.5, donde Vdc1 = 2·Vdc2 = 2E, se pueden formar siete niveles: tres positivos, tres negativos y el cero. En este caso también existe redundancia en la formación de un nivel, el E. Para la tabla 1.6, en que los voltajes se escalan multiplicados por tres, se pueden obtener nueve niveles: cuatro positivos, cuatro negativos y el cero. En este caso en particular, no existe redundancia. Por último, para la tabla 1.7, en que un voltaje es cuatro veces mayor que el otro, también pueden formarse nueve niveles: cuatro positivos, cuatro negativos y el cero, sin existir tampoco existen redundancias. Sin embargo, los niveles de voltaje 2E y -2E no pueden ser generados. Cabe recordar sin embargo, que en cada puente “H” individual, existe redundancia interna para generar el nivel cero, lo que quedó de manifiesto en la Tabla 1.1, donde se ve que éste puede ser generado de dos formas diferentes.

Entonces se puede concluir que hay una razón óptima de tensiones entre cada puente, representada por la tabla 1.6. Basta con mirar la Tabla 1.7 para darse cuenta que no se puede generar el nivel de voltaje 2E, por lo que esa configuración de relaciones de voltaje no es apropiada. La siguiente ecuación (Ecuación 1.1) es válida para encontrar la razón entre los voltajes que maximiza el número de niveles, dado el número de estados de cada puente [11]:

( 1)

1

1 , 1,3,....( 1)( 1)

donde,: número de puentes "H" del inversor: número de niveles de voltaje que puede entregar el i-esimo puente

: Fuente DC del i-esimo puente

i iidc dc

i i

ii

dc

nV V i Nn n

Nn

V

−

−

−= ⋅ = −

⋅ −

(1.1)

De acuerdo con la ecuación anterior, para un inversor compuesto sólo de módulos de tres estados (+Vdc, 0 y –Vdc) en cascada, como los puentes “H”, ni = 3, ni-1 = ni, el número de niveles puede ser maximizado si 3·Vdc

(i-1)= Vdci, es decir,

22

fuentes escaladas en potencias de tres. De este análisis se desprende que los inversores multietapa con tensiones no escaladas no son aprovechados al máximo, por lo que es preferible que las diferentes etapas sean escaladas en tensión, lográndose el óptimo de niveles cuando los puentes se escalan en potencias de tres. En este último caso, para una cascada de N puentes, el número de niveles resultantes se eleva a los 3N.

1.3. Objetivos de la memoria

Esta memoria trata sobre el diseño y construcción de un inversor trifásico multinivel. Se utilizó la tecnología de puentes “H” en cascada, con tensiones de alimentación escaladas en potencia de tres para maximizar el número de niveles. El inversor desarrollado consta de cuatro etapas por fase (N = 4), por lo que el número de niveles se eleva a 81 (34): cuarenta niveles de tensión positivos, cuarenta negativos y el nivel “cero”. Como puede apreciarse, el número de niveles logrados es enorme en relación a las fuentes independientes utilizadas en cada fase (sólo cuatro), lo que permitirá el control de la tensión de este inversor sin usar modulación PWM, es decir, sólo modulado por amplitud. De esta forma, se podrán aprovechar ventajas tales como baja frecuencia de conmutación y fuentes de voltaje pequeñas utilizando el escalamiento de las tensiones de alimentación.

Los capítulos siguientes explican las diferentes etapas de diseño, construcción simulaciones y pruebas experimentales relacionados con el prototipo de 81 niveles anteriormente indicado.

En el Capítulo II se muestran las características del inversor construido, el cual puede generar ochenta y un niveles de tensión diferentes. Se verá la importancia que tiene el escalamiento en potencia de tres, tanto para las frecuencias de conmutación como para la posibilidad de ligar las fuentes escaladas de baja tensión.

En el Capítulo III se presentan algunas simulaciones computacionales para mostrar el funcionamiento del inversor, tales como formas de onda de corrientes voltajes y potencias en cada puente, para alimentar la carga trifásica. También se

23

hacen comparaciones con la modulación PWM para apreciar las enormes ventajas que presenta esta nueva topología.

En el Capítulo IV se describen las diferentes etapas de diseño y construcción del inversor antes mencionado, mostrando cada etapa de su elaboración con figuras y fotografías.

En el Capítulo V se muestran los resultados experimentales obtenidos, y se comparan con simulaciones bajo las mismas características de operación.

Finalmente, en el Capítulo VI se presentan las conclusiones del trabajo realizado y se proponen trabajos a futuro con la tecnología multinivel.

24

II. CARACTERÍSTICAS DE UN INVERSOR DE CUATRO ETAPAS Y OCHENTA Y UN NIVELES.

2.1. Introducción

Como se dijo en el capítulo anterior, los inversores multinivel pueden, si el número de niveles es elevado, trabajar sólo con modulación de amplitud y prescindir del PWM, permitiendo frecuencias de modulación de los semiconductores muy bajas. Un elevado número de niveles de escalonamiento de tensión hace, además, la salida del inversor más limpia, obteniendo ondas de corriente y voltaje casi perfectas, reduciendo a valores despreciables las indeseadas armónicas.

Debido a que esta Memoria trata en particular sobre el diseño y construcción de un inversor trifásico de 4 etapas y 81 niveles, se ha dedicado este capítulo a explicar sus características relevantes. Un inversor del tipo puentes “H” en cascada de cuatro etapas, es uno que consta de cuatro puentes “H” en serie, con una fuente DC independiente para cada uno, como muestra la Figura 2.1. En la sección 1.3 de esta memoria, se habló de la maximización de los niveles en relación al escalonamiento de los voltajes de un inversor multinivel, utilizando puentes “H” en cascada y se dedujo que lo óptimo es utilizar una relación 3·Vdc

(i-1)= Vdci. Aplicando

este escalonamiento en potencia de 3, con N = 4 puentes se obtienen 81 (34) niveles de voltaje diferentes: 40 positivos, 40 negativos y el cero.

Debido al escalonamiento en potencia de tres, las fuentes de tensión que alimentan los sucesivos puentes “H” de la cadena, decrecen rápidamente y con ello la potencia que estos puentes entregan a la carga. De hecho, y como se verá mas adelante, sólo un puente de la cadena maneja más del 80 % de la potencia transferida, por lo que este puente en particular recibirá el nombre de Maestro. El Maestro es el puente “H” que está en la parte inferior de la Figura 2.1, ya que justamente es el que tiene el mayor voltaje. El resto de los puentes “H” serán llamados Esclavos. El Maestro, además, es el que trabaja a menor frecuencia de conmutación, mientras que el Esclavo superior de la cadena presenta las características inversas, es decir, la mayor frecuencia de conmutación, pero el menor voltaje, lo que es una ventaja en este tipo de topologías.

25

Vac

27·Vdc

9·Vdc

3·Vdc

Vdc

Esclavo 2

Esclavo 3

Esclavo 1

Maestro

Figura 2.1: Inversor de tipo puentes “H” en cascada, de 4 etapas y 81 niveles (una fase).

La Figura 2.2 muestra las frecuencias de conmutación resultantes en cada uno de los cuatro puentes de una fase del inversor, para una salida de tensión sinusoidal con 81 escalones. Si las tensiones de la figura se suman, se obtendrá una forma de onda aproximadamente sinusoidal, con 40 escalones positivos, 40 negativos y un nivel cero Volts.

26

Figura 2.2: Frecuencias de conmutación de los 4 puentes en el inversor de 81 niveles.

Nótese en la figura 2.2 el escalonamiento de tensiones. La simulación muestra para el Maestro, un nivel máximo de alrededor de 60 Volts, para el Esclavo 1, de alrededor de 20 Volts, para el 2 en el entorno de 7 Volts y para el 1 de poco mas de 2 Volts, es decir se aprecia claramente el escalonamiento en potencia de 3 de las tensiones, en los cuatro puentes de la cascada. Con 81 niveles de voltaje, el inversor puede obtener una onda sinusoidal casi perfecta, como se aprecia en la Figura 2.3, en la que además se muestra el resultado con inversores de menor número de niveles.

27

11 Niveles

-150,00

-100,00

-50,00

0,00

50,00

100,00

150,00

0,00 0,01 0,01 0,02 0,02

31 Niveles

-150,00

-100,00

-50,00

0,00

50,00

100,00

150,00

0,00 0,01 0,01 0,02 0,02

3 Niveles

-150,00

-100,00

-50,00

0,00

50,00

100,00

150,00

0,00 0,01 0,01 0,02 0,02

81 Niveles

-150

-100

-50

0

50

100

150

0 0,005 0,01 0,015 0,02

21 Niveles

-150,00

-100,00

-50,00

0,00

50,00

100,00

150,00

0,00 0,01 0,01 0,02 0,02

T H D = 24,6 % T H D = 4,6 %

T H D = 1,1 %T H D = 1,9 %

T H D = 0,3 %

Figura 2.3: Comparación de ondas de salida de inversores de 3, 11, 21, 31 y 81 niveles.

28

De la figura 2.3 se puede constatar lo que se dijo en 1.1: que a mayor número de niveles, mejor es la forma de la onda y, por lo tanto, menor distorsión armónica, por lo que los 81 niveles sintetizados en el inversor construido son suficientes para mostrar las ventajas de esta topología. En la Figura 2.4, se aprecia la modulación de amplitud de un convertidor de 81 niveles obtenida mediante el apagado o encendido de cada uno de los cuatro puentes “H” que lo conforman. Las formas de onda de las frecuencias de conmutación mostradas en la Figura 2.2 correspondían a una modulación del 100%.

VAC [%]100 %

75 %

50 %

25 %

VAC [%]100 %

75 %

50 %

25 %

Figura 2.4: El efecto de la modulación por amplitud.

Otra configuración posible para un inversor de cuatro etapas y 81 niveles, es la que se muestra en la figura 2.5, en la que el uso de transformadores independientes con sus secundarios conectados en serie es presentada. La ventaja principal de esta configuración es que no requiere de fuentes independientes de tensión continua. Todos los puentes, incluyendo las tres fases, pueden ir conectados a una única fuente de alimentación continua Vdc.

29

a:27

Vdc

a:9

a:3

a:1

Vac

Figura 2.5: Esquema de un inversor con transformadores de salida.

Se observa en esta topología que el escalamiento en potencia de tres de los voltajes continuos de alimentación queda ahora transferido a la relación primario/secundario de los transformadores de cada uno de los puentes “H”. La diferencia principal con el sistema mostrado en la Figura 2.1 es que esta configuración es apta para sistemas de frecuencia fija (50 ó 60 Hz) por lo que se presta perfectamente para ser ocupada como rectificador de frente activo, compensador de reactivos o como filtro activo [1]. Detalles de esta configuración pueden ser encontrados en la referencia [12].

30

2.2. Características del Prototipo

Debido a la relación de potencia de tres entre los sucesivos voltajes de los cuatro puentes o etapas, el inversor multinivel construido ha maximizado la cantidad de niveles posibles, lográndose 81 niveles con sólo cuatro puentes “H” en cascada.

Debido a que el puente que maneja mayor voltaje, opera a frecuencias menores, y viceversa (figura 2.2), la distribución de potencia no es igual para todos los puentes. Más aún, la mayor parte de esta se la lleva el Maestro, razón por la cual lleva ese nombre. Para apreciar esta característica, la Figura 2.6 muestra las potencias de los distintos puentes para una carga puramente resistiva. La explicación de este fenómeno en la distribución de potencia se debe a que los esclavos modulan la tensión de tal forma que entregan y reciben potencia activa desde su fuente de tensión muchas veces en un período, lo que da como resultado potencias medias muy reducidas en los esclavos, las que incluso pueden llegar a ser negativas bajo ciertas condiciones de la carga (inductiva, negativa, etc.).

Figura 2.6: Distribución de potencias para una carga puramente resistiva (Cosϕ=1)

31

Como la potencia es tan desigualmente distribuida, se constata que las fuentes DC requeridas por los Esclavos resultan ser pequeñas. Esta característica permite pensar en el uso de fuentes de tensión para los Esclavos, alimentadas desde la misma fuente del Maestro (fuentes conmutadas DC-DC). No obstante, y como ya se ha mencionado, la potencia en los Esclavos fluye bidireccionalmente. Además, las fuentes de cada uno de los cuatro puentes “H” deben ser independientes, es decir, sin referencia común, pues lo que en principio se está haciendo con este inversor es sumar, restar o sacar cada una de estas fuentes para ir generando la corriente alterna escalonada. Por lo tanto, estas pequeñas fuentes DC-DC para alimentar los Esclavos desde el Maestro, deben ser bidireccionales y al mismo tiempo aisladas galvánicamente del Maestro y de los mismos Esclavos entre sí.

En el siguiente gráfico de la Figura 2.7 se pueden apreciar las potencias de cada uno de los puentes, para distintas frecuencias de operación de un motor de inducción. Del gráfico, y tal como se hizo ver anteriormente, se puede apreciar que existen circunstancias donde las fuentes absorben potencia en vez de entregarla (en el gráfico se aprecian como valores negativos). Es por esto que el uso de fuentes DC-DC bidireccionales, para alimentar a los Esclavos, es una exigencia ineludible. Además, como los Esclavos manejan potencias relativamente bajas en relación al Maestro, la utilización de estas fuentes no involucra nuevos componentes pesados y costosos. La Figura 2.8 muestra una fuente DC-DC bidireccional que puede ser usada para este propósito. Este diseño cumple con el otro requisito obligatorio de tener aislación galvánica (a través de un transformador de alta frecuencia), para mantener las referencias independientes.

Debido a que en este trabajo de memoria las fuentes que se diseñaron y construyeron no son bidireccionales, es necesario por ahora no operar el inversor donde las fuentes absorban potencia, es decir, con factores de potencia pequeños o con cargas que entreguen potencia hacia el lado de tensión continua. No obstante, en otro trabajo de memoria se está trabajando en estas fuentes bidireccionales para permitir al inversor operar con todas sus capacidades.

32

-5000

0

5000

10000

15000

20000

0 10 20 30 40 50 60 70 80 90 10

Frecuency (Hz)

Pow

er (W

atts

)

0

Total PowerMasterSlave 1Slave 2Slave 3

Figura 2.7: Distribución de potencias para distintitas frecuencias en un motor de inducción de 20 kW por fase.

Entrada DCdel Maestro

Salida DCpara Esclavo

a:1

Figura 2.8: Esquema de una fuente DC-DC bidireccional.

33

2.3. Control del Inversor

A pesar que este tema está fuera del alcance de esta memoria, se hará una pequeña explicación del control que se desarrolló para poner en funcionamiento el inversor. Para esto se programó un DSP (Digital Signal Processor) de Texas Instruments, modelo TMS320F241, el cual se encarga de generar las señales de encendido de los transistores en los puentes “H”, para sintetizar la onda sinusoidal deseada.

El control se basa en sacar una tabla predeterminada de 16 bits (uno para cada uno de los cuatro transistores de los cuatro puentes “H”), grabada en la memoria del DSP, por los puertos de salida de éste, a una frecuencia fija, dada por interrupciones de timer. Debido a que los puertos del DSP son de 8 bits, se tuvo que ocupar dos de estos para sintetizar la onda.

Como los puentes tienen tres estados (+Vdc, 0 y –Vdc) y están escalados en potencia de 3, la tabla grabada en la memoria fue diseñada tal como muestra la Tabla 2.1. Los valores de voltaje de salida que se observan en la tabla son porque se ha elegido para el Maestro una fuente de voltaje DC de 63 volts. De allí resulta el escalamiento de 63, 21, 7 y 2,33 volts. Los “peldaños” de la tensión resultante son iguales a la tensión más pequeña que corresponde al Esclavo 3, es decir, de 2,33 volts. También el valor 2,33 es el valor más pequeño de tensión que se puede generar después del cero. El valor máximo de tensión en la salida, es igual a la suma de las tensiones continuas de los cuatro puentes, es decir, 63+21+7+2,33=93,33 volts. El mismo valor mínimo negativo se alcanza cuando los cuatro puentes entregan las tensiones continuas invertidas hacia la carga. Con la configuración de tensiones en “base tres” (potencia de tres) implementada, cualquier valor de voltaje a la salida, entre 93,33 y -93,33 volts, con escalones de 2,33 volts puede ser generado. Por lo tanto, lo que hace el DSP es aproximar el valor análogo de una referencia al valor escalonado más cercano posible. Por ejemplo, si la referencia instantánea es 54%, este porcentaje corresponde a un valor de 93,33·0,54=50,4 volts. El escalón más cercano a este valor es el 51,33, que es igual a 63-21+7+2,33 y tiene una diferencia con la referencia de sólo 0,93 volts. Por lo tanto, el DSP generará una señal de salida instantánea en la que se ordena al Maestro generar 63 volts, al Esclavo 1 -21 volts, al Esclavo 2 7 volts y al Esclavo 3 2,33 volts.

34

Tabla 2.1: Tabla de estado de los puentes para obtener todos los voltajes.

Voltaje de Salida (V) Maestro Esclavo 1 Esclavo 2 Esclavo 3 0 0 0 0 0 2,33 0 0 0 1 4,66 0 0 1 -1 7 0 0 1 0 9,33 0 0 1 1 11,66 0 1 -1 -1 14 0 1 -1 0 16,33 0 1 -1 1 18,66 0 1 0 -1 21 0 1 0 0 . .

.

. . .

.

. . .

51,33 1 -1 1 1 · ·

· ·

· ·

· ·

· ·

93,33 1 1 1 1

En base a esta tabla, se construye a su vez, la tabla binaria del DSP para encender o apagar los semiconductores de cada puente “H”. La figura 2.9 muestra nuevamente uno de los cuatro puentes “H” de la cascada, en donde los semiconductores aparecen como S1, S2, S3 y S4. Para obtener una salida positiva en el puente respectivo, se deben cerrar sólo las válvulas S1 y S4; para obtener una salida cero, se deben cerrar S1 y S2 (ó S3 y S4) y para obtener una salida negativa se deben cerrar sólo las válvulas S2 y S3. En el ejemplo del párrafo anterior, el DSP ordenará al Maestro, al Esclavo 2 y al Esclavo 3 cerrar sus respectivas válvulas S1 y S4, en tanto que ordenará al Esclavo 1 a cerrar (o encender) sus válvulas (o transistores) S2 y S3.

35

Vdc

S1

S3

S2

S4

Vab

+

-

Figura 2.9: Esquema del Puente “H” usado.

El detalle del programa, realizado en lenguaje ASSEMBLER, se adjunta en el Anexo B de esta memoria.

2.4. Aplicaciones del Inversor Multinivel Construido

Filtros activos de potencia, rectificadores de corriente sinusoidales, accionadores de motores y compensadores de reactivos son algunas de las aplicaciones de los inversores multinivel. Sin embargo, el inversor fue diseñado específicamente para accionamientos trifásicos, sean estos con máquinas de inducción o síncronas.

Una posible configuración para este tipo de aplicación es la que se muestra a continuación (Figura 2.10)

36

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

V3S3

V3S2

V3S1

V3M

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

V2S3

V2S2

V2S1

V2M

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

V1S3

V1S2

V1S1

V1M

Motor

Figura 2.10: Sistema para alimentar motores con fuentes independientes.

Como se puede apreciar, el sistema consta de tres inversores independientes, donde cada uno de los cuatro puentes “H” que forman una fase está alimentado por fuentes DC independientes. Debido a esta característica, las bobinas del motor usado pueden estar conectadas en estrella (neutro común) debido a la independencia de las tierras de los tres inversores. Sin embargo, esta configuración tiene un gran problema: la cantidad de fuentes DC independientes que se requieren. Ahora, si se contara con las fuentes DC-DC bidireccionales antes propuestas en la Figura 2.8, el sistema podría simplificarse y utilizar una sola fuente común de tensión continua como el mostrado en la figura 2.11.

37

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Motor

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Figura 2.11: Sistema para alimentar motores con fuentes DC-DC bidireccionales.

Efectivamente se puede apreciar que con esta configuración sólo es necesaria una fuente DC para todo el sistema, siendo reemplazadas todas las fuentes DC independientes de la Figura 2.10, por fuentes DC-DC bidireccionales, aisladas galvánicamente. Sin embargo, el uso de fuentes DC-DC bidireccionales en los Maestros no debe permitirse, pues como ya se ha visto, ellos manejan más del 80% de la potencia, lo que significaría construir enormes y costosas fuentes bidireccionales. Una forma de eliminar estas fuentes es utilizando motores con sus devanados trifásicos independientes, como se observa en la figura 2.12, lo que permite que los Maestros de las tres fases sean directamente alimentados de la misma fuente de tensión, sin necesidad de aislación galvánica.

38

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Esclavo 3

Esclavo 2

Esclavo 1

Maestro

Motor

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

Fuente DC-DCBidireccional

VMaster

Figura 2.12: Diagrama de un motor con bobinas independientes.

El sistema que se construyó en esta memoria, es capaz de utilizar cualquiera de las configuraciones anteriores. Actualmente, y provisoriamente, se tiene un sistema con fuentes DC fijas e independientes como el mostrado en 2.10, pero una vez que se construyan las fuentes bidireccionales se puede ocupar cualquiera de las configuraciones anteriores.

El próximo capítulo mostrará algunas simulaciones computacionales realizadas en un inversor de cuatro etapas y 81 niveles como el que se ha descrito en este capítulo. Allí se podrán apreciar las virtudes que posee este tipo de topología frente a otras más convencionales.

39

III. SIMULACIONES DEL INVERSOR CONSTRUIDO

En este capitulo, se presentan algunas simulaciones de la topología propuesta. Estas simulaciones fueron obtenidas usando el programa PSIM (Power Electronics Simulator), el cual presenta ventajas de velocidad de procesamiento en relación al PSpice y también mayor número de componentes especializados [13].

En la sección 2.1 de esta memoria, se habló sobre la modulación de voltaje de los inversores multinivel. También se mostró la modulación de voltaje de cada uno de los cuatro puentes “H”, en la que se observaba el escalamiento en potencia de 3 de las tensiones. Estos voltajes se muestran nuevamente en la Figura 3.1 con el objeto de apreciar, en la Figura 3.2, cómo la suma de estos cuatro oscilogramas genera la tensión sinusoidal escalonada.

Figura 3.1: Modulación de voltaje de los cuatro puentes “H” del inversor multinivel.

40

Figura 3.2: Formación de la onda de voltaje alterna del inversor de 81 niveles.

La figura 3.2(a) muestra la salida del inversor si sólo fuese formada por la fuente DC del Esclavo 3. Si a esa onda, se le suma el voltaje de salida del Esclavo 2 (característica de la configuración puentes “H” en cascada), se obtiene la figura 3.2(b). Ahora, si a la onda de la figura 3.2(b) se le suma la salida de voltaje del Esclavo 1, se obtiene la forma de onda de la figura 3.2(c). Por último, si a esa onda

41

se le suma el voltaje del Maestro se obtiene la onda sinusoidal que se muestra en 3.2(d).

Las corrientes en el lado de la fuente DC de cada uno de los puentes “H” se muestran en la figura 3.3, donde se comparan las corrientes para una carga puramente resistiva con las corrientes de una carga R-L (f.p.=0,11). Hay que destacar que los sistemas que se comparan, tienen el mismo valor de potencia activa.

Figura 3.3: Corrientes de los puentes “H” para una carga (a) resistiva e (b) inductiva.

La potencia de cada uno de los puentes “H”, tiene la misma forma de onda que la figura 3.3 con la diferencia que cada una de las corrientes está amplificada por un valor constante, que corresponde al valor de la fuente de alimentación DC del puente respectivo. Se puede demostrar que las potencias de los puentes “H” cambian de forma con la carga, pero los porcentajes de participación de cada puente sobre la potencia total no. El puente Maestro coopera con casi el 81%, el

42

Esclavo 1 con casi el 16%, el Esclavo 2 con menos del 3% y el Esclavo 3 con menos del 0,5%.

La forma de la corriente resultante para cada caso de la Figura 3.3 se puede apreciar en la figura 3.4.

Figura 3.4: Corrientes de salida del inversor para una carga (a) resistiva e (b) inductiva.

A pesar de que el intervalo de graficado es el mismo, se puede apreciar que hay diferencias esperadas entre las corrientes: 1) el retraso de fase que presenta la corriente inductiva y 2) el alisamiento de la corriente en el segundo caso por efecto de filtrado de la carga inductiva.

Para ver las ventajas del inversor construido en relación a técnicas más convencionales, se realizó una comparación bajo las mismas características, entre un

43

inversor monofásico PWM y una fase del inversor de 81 niveles construido. Ambos diagramas de simulación generados para el PSIM se muestran en la Figura 3.5.

Figura 3.5: Diagrama en PSIM de los inversores usados para las simulaciones.

La Figura 3.6 presenta una comparación entre los voltajes de salida de ambos inversores. La curva de voltaje de color rojo, corresponde al inversor PWM y la azul al inversor Multinivel.