consulta1_completa

-

Upload

carlos-paul-yanchapaxi -

Category

Documents

-

view

176 -

download

0

Transcript of consulta1_completa

Escuela Politcnica Nacional

Sistemas Digitales

OTROS TIPOS DE LGICA INTRODUCCION A LA LOGICA Que es la lgica. La Lgica proviene de los trminos griegos, logos, 'palabra' y 'proposicin', 'razn', es una disciplina y rama de la filosofa que estudia los principios formales del conocimiento humano. Su principal anlisis se centra en la validez de los razonamientos y argumentos, por lo que se esfuerza por determinar las condiciones que justifican que el individuo, a partir de proposiciones dadas, llamadas premisas, alcance una conclusin derivada de aqullas. La validez lgica depende de la adecuada relacin entre las premisas y la conclusin, de tal forma que si las premisas son verdaderas la conclusin tambin lo ser. Por ello, la lgica se encarga de analizar la estructura y el valor de verdad de las proposiciones, y su clasificacin. La validez de una proposicin se tomar de la veracidad de la conclusin. Si una de las premisas, o ms, es falsa, la conclusin de una proposicin vlida ser falsa. Por ejemplo: Todos los mamferos son animales de cuatro patas, todos los hombres son mamferos, por lo tanto, todos los hombres son animales de cuatro patas es una proposicin vlida que conduce a una conclusin falsa. Por otro lado, una proposicin nula puede, por casualidad, llegar a una conclusin verdadera: Algunos animales tienen dos patas; todos los hombres son animales, por lo tanto todos los hombres tienen dos patas representa una conclusin verdadera, pero la proposicin no lo es. Por lo tanto, la validez lgica depende de la forma que adopta la argumentacin, no su contenido. Si la argumentacin fuera vlida, cualquier otro trmino podra sustituir a cualquiera de los casos utilizados y la validez no se vera afectada. Al sustituir cuatro patas por dos patas se comprueba que ambas premisas pueden ser verdaderas y la conclusin falsa. Por lo tanto, la proposicin no es correcta aunque posea una conclusin verdadera. De que trata la lgica. En una primera aproximacin al tema, podremos dar la siguiente definicin: La lgica investiga la relacin de consecuencia que se da entre una serie de premisas y la conclusin de un argumento correcto. Se dice que un argumento es correcto (valido) si su conclusin se sigue o es consecuencia de sus premisas; de otro modo es incorrecto. Por un argumento entendemos un sistema de enunciados, de un lenguaje determinado. Uno de esos enunciados es designado como la conclusin y el resto como las premisas. Un enunciado se define como una expresin lingstica que establece un pensamiento completo: Interrogativos, Imperativos, Declarativos. Introduccin histrica. La lgica matemtica surge como el resultado de la convergencia de cuatro lneas de pensamiento: La lgica antigua (Aristteles, megrico-estoica). La idea de un lenguaje completo y automtico para el razonamiento. Los nuevos progresos en algebra y geometra acaecidos despus de 1825.Wladimir Ortiz Fernndez-

1 -

Escuela Politcnica Nacional

Sistemas Digitales

La idea de que hay partes de la matemtica que son sistemas deductivos, esto es, cadenas de razonamientos que se conforman a las reglas de la lgica. Forma de presentacin de los sistemas lgicos. Los diferentes sistemas lgicos elementales tienen en comn, en su presentacin, una etapa previa de simbolizacin que suele hacerse a dos niveles: Lgica proposicional: Frases declarativas simples, enunciados y proposiciones. Lgica de predicados: Se toma como base los componentes de una proposicin, trminos, cuantificadores.

Dentro de cada uno de estos niveles de representacin del lenguaje, se pueden considerar dos formas de presentar las estructuras deductivas correctas: Sintctica: Definicin axiomtica de una serie de estructuras deductivas correctas y de reglas para obtener nuevas estructuras deductivas correctas a partir de aquellas: Teora de la demostracin y deduccin natural. Semntica: Definicin de significados (Verdadero, Falso), definicin de las estructuras deductivas correctas a partir de la relacin de significados de los elementos de la deduccin: Teora de modelos.

APLICACIONES Aplicada a los procesos La lgica es el "proceso de reflejo del mundo objetivo en la conciencia del hombre y de verificacin de la correccin de este reflejo por la prctica, es generada histricamente por la vida de los hombres concretos, cuando se separan de los fenmenos de la naturaleza", sus categoras son escalones y puntos focales del conocimiento de la naturaleza objetivamente existente, lo que caracteriza la conciencia del hombre que se desprende de la naturaleza objetivamente existente. Aplicada a las matemticas El hombre de hoy se relaciona ms frecuentemente con la lgica matemtica que se refiere a un sistema deductivo en el que existen ciertos axiomas bsicos y ciertas reglas de deduccin. Ese sistema est formado por un conjunto de expresiones (o smbolos) que permiten construir determinadas proposiciones (o secuencias de signos dotables de significado), las reglas deductivas permiten reconocer cuales son las afirmaciones deducibles de los axiomas mediante las reglas de deduccin y cules no. Aplicada a la electrnica Gracias a la lgica, la electrnica a tenido un gran desarrollo, ya que con el anlisis y diseo de circuitos lgicos se ha logrado fabricar desde simples relojes y calculadoras hasta sofisticados procesadores. 1.1 FPGAs INTRODUCCION Cuando se aborda el diseo de un sistema electrnico y surge la necesidad de implementar una parte con hardware dedicado son varias las posibilidades que hay. En la _gura 1 se han representado las principales aproximaciones ordenandolas en funcin de los parmetros coste, flexibilidad, prestaciones y complejidad. Como se puede ver, las mejores prestaciones las proporciona un diseo full-custom, consiguindose a costa de elevados costes y enorme complejidad de diseo. En el otro extremo del abanico de posibilidades se encuentra la implementacin software, que es muy barata yWladimir Ortiz Fernndez WOF-

2-

Escuela Politcnica Nacional

Sistemas Digitales

flexible, pero que en determinados casos no es vlida para alcanzar un nivel de prestaciones relativamente alto.

Figura 1: Diferentes soluciones para el diseo de circuitos digitales

Entre estas dos opciones se puede elegir la fabricacin de un circuito electrnico realizado mediante diseo semi-custom, utilizando clulas estndar, o recurrir a un circuito ya fabricado que se pueda \programar" in situ, como son las FPGAs. De estas dos opciones la primera proporciona mejores prestaciones, aunque es ms cara y exige un ciclo de diseo relativamente largo. Por otro lado, los dispositivos lgicos programables constituyen una buena oferta para realizar diseos electrnicos digitales con un buen compromiso coste-prestaciones. Y lo que es mejor, permiten obtener una implementacin en un tiempo de diseo asombrosamente corto (con la consiguiente reduccin del parmetro clave: Time to market). Otro aspecto que se debe tener en cuenta para decidirse por este tipo de implementacin es que el coste de realizacin es muy bajo, por lo que suele ser una buena opcin para la realizacin de prototipos. En estas notas vamos a describir de forma muy somera en qu consisten estos dispositivos, particularizando para una familia del fabricante Xilinx. La informacin contenida en ellas se basa en gran medida en las siguientes fuentes: sobre arquitectura de FPGAs [BFRV92, Xil91, CSR+99a]; sobre diseo de circuitos [WE94, CSR+99b].

EVOLUCIN DE LOS DISPOSITIVOS PROGRAMABLES Se entiende por dispositivo programable aquel circuito de propsito general que posee una estructura interna que puede ser medicada por el usuario (o a peticin suya, por el fabricante) para implementar una amplia gama de aplicaciones. El primer dispositivo que cumpli estas caractersticas era una memoria PROM, que puede realizar un comportamiento de circuito utilizando las lneas de direcciones como entradas y las de datos como salidas (implementa una tabla de verdad). Hay dos tipos bsicos de PROM: 1. Programables por mscara (en la fbrica), proporcionan mejores prestaciones. Son las denominadas de conexiones hardwired. 2. Programables en el campo (field) por el usuario final. Son las EPROM y EEPROM. Proporcionan peores prestaciones, pero son menos costosas para volmenes pequeos de produccin y se pueden programar de manera inmediata.Wladimir Ortiz Fernndez WOF-

3-

Escuela Politcnica Nacional

Sistemas Digitales

El PLD, Programmable Logic Device, es una matriz de puertas AND conectada a otra matriz de compuertas OR ms biestables. Cualquier circuito lgico se puede implementar, por tanto, como suma de productos. La versin ms bsica del mismo es una PAL, con un plano de puertas AND y otro tipo de puertas OR. Las salidas de estas _ultimas se pueden pasar por un biestable en la mayora de los circuitos del mercado. Ventaja: son bastante en clientes si implementan circuitos no superiores a unos centenares de puertas. Inconvenientes: arquitectura rgida, y est limitado por un nmero fijo de biestables y entradas/salidas. La PLA, Programmable Logic Array, es ms flexible que la PAL: se pueden programar las conexiones entre los dos planos. Estos dispositivos son muy simples y producen buenos resultados con funcionalidades sencillas (slo combinacional). Hace falta algo un poco ms sofisticada y general: una matriz de elementos variados que se puedan interconectar libremente. Este es el caso de una MPGA (Mask-Programmable Gate Array), cuyo principal representante est constituido por un conjunto de transistores ms circuitera de E/S. Se unen mediante pistas de metal que hay que trazar de forma _optima, siendo _esta la mscara que hay que enviar al fabricante. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques. ESTRUCTURA GENERAL DE LAS FPGAS El proceso de diseo de un circuito digital utilizando una matriz lgica programable puede descomponerse en dos etapas bsicas: 1. Dividir el circuito en bloques bsicos, asignndolos a los bloque configurables del dispositivo. 2. Conectar los bloques de lgica mediante los conmutadores necesarios.

Figura 2: Estructura general de una FPGA (en concreto de XILINX)

Para ello el fabricante proporciona las herramientas de diseo adecuadas. Los elementos bsicos constituyentes de una FPGA como las de Xilinx se pueden ver en la Figura 2 y son los siguientes:Wladimir Ortiz Fernndez WOF-

4-

Escuela Politcnica Nacional

Sistemas Digitales

1. Bloques lgicos, cuya estructura y contenido se denomina arquitectura. Hay muchos tipos de arquitecturas, que varan principalmente en complejidad (desde una simple puerta hasta mdulos ms complejos o estructuras tipo PLD). Suelen incluir biestables para facilitar la implementacin de circuitos secuenciales. Otros mdulos de importancia son los bloques de Entrada/Salida, 2. Recursos de interconexin, cuya estructura y contenido se denomina arquitectura de rutado. 3. Memoria RAM, que se carga durante el RESET para configurar bloques y conectarlos. Entre las numerosas ventajas que proporciona el uso de FPGAs dos destacan principalmente: el bajo coste de prototipado y el corto tiempo de produccin. No todo son ventajas. Entre los inconvenientes de su utilizacin est_an su baja velocidad de operacin y baja densidad lgica (poca lgica implementable en un solo chip). Su baja velocidad se debe a los retardos introducidos por los conmutadores y las largas pistas de conexin. Por supuesto, no todas las FPGA son iguales. Dependiendo del fabricante nos podemos encontrar con diferentes soluciones. Las FPGAs que existen en la actualidad en el mercado se pueden clasificar como pertenecientes a cuatro grandes familias, dependiendo de la estructura que adoptan los bloques lgicos que tengan definidos. Las cuatro estructuras se pueden ver en la _gura 3, sin que aparezcan en la misma los bloques de entrada/salida. 1. Matriz simtrica, como son las de XILINX 2. Basada en canales, ACTEL 3. Mar de puertas, ORCA 4. PLD jerrquica, ALTERA o CPLDs de XILINX. En concreto, para explicar el funcionamiento y la estructura bsica de este tipo de dispositivos programables slo se consideraran las distintas familias de XILINX.

Figura 3: Tipos de FPGAs 2. Arquitectura de las FPGA de Xilinx TECNOLOGA DE PROGRAMACIN Antes de continuar con conocimientos ms avanzados acerca de FPGAs (de XILINX en concreto), hay que aclarar cmo se realiza el proceso de programacin (ie., las conexiones necesarias entreWladimir Ortiz Fernndez WOF-

5-

Escuela Politcnica Nacional

Sistemas Digitales

bloques y pistas). En primer lugar, si se piensa que el nmero de dispositivos de conexin que hay en una FPGA es muy grande (tpicamente superior a 100.000), es necesario que cumplan las siguientes propiedades: Ser lo ms pequeos que posible. Tener la resistencia ON lo ms baja posible, mientras la OFF ha de ser lo ms alta posible (para que funcione como conmutador). Se deben poder incorporar al proceso de fabricacin de la FPGA. El proceso de programacin no es nico, sino que se puede realizar mediante diferentes \tecnologas", como son clulas RAM estticas, transistores EPROM y EEPROM, etc. En el caso de las FPGAs de XILINX los elementos de programacin se basan en clulas de memoria RAM que controlan transistores de paso, puertas de transmisin o multiplexores. En la figura 4 se puede ver esquemticamente cmo son. Dependiendo del tipo de conexin requerida se elegir un modelo u otro.

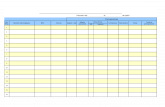

Figura 4: Tipos de conectores utilizados por XILINX Es importante destacar que si se utilizan clulas SRAM la configuracin de la FPGA ser vlida nicamente mientras est conectada la alimentacin, pues es memoria voltil. En los sistemas finales est claro que hace falta algn mecanismo de almacenamiento no voltil que cargue las clulas de RAM. Esto se puede conseguir mediante EPROMs o disco. Este elemento de programacin es relativamente grande (necesita por lo menos 5 transistores), pero se puede implementar en el proceso normal de fabricacin del circuito (es CMOS). Adems, permite reconfigurar la FPGA de una forma muy rpida. DESCRIPCIN DE LAS PRINCIPALES FAMILIAS Hay mltiples familias lgicas dentro de XILINX. Las primeras que surgieron son: XC2000 (Descatalogada en el ao 1999), XC3000 y XC4000, correspondientes respectivamente a la primera, segunda y tercera generacin de dispositivos, que se distinguen por el tipo de bloque lgica configurable (CLB) que contienen. En la actualidad existen tambin las familias de FPGA SpartanII, SpartanIII, Virtex, VirtexII y VirtexPro. La tabla 1 muestra la cantidad de CLBs que puede haber en cada FPGA de las familias base y ese mismo valor expresado en puertas equivalentes. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques.Wladimir Ortiz Fernndez WOF-

6-

Escuela Politcnica Nacional

Sistemas Digitales

Cuadro 1: Familias del fabricante XILINX El bloque lgica ha de ser capaz de proporcionar una funcin lgica en general y reprogramable. La mejor forma de realizar esto es mediante una tabla de valores \preasignados" o \tablas de lookup". Bsicamente, una tabla de look-up (LUTs en adelante) es una memoria, con un circuito de control que se encarga de cargar los datos. Cuando se aplica en una direccin las entradas de la funcin booleana la memoria devuelve un dato, lo que se puede hacer corresponder con la salida requerida. Falta a~nadir los componentes necesarios para desempear funciones no implementables con una memoria, tales como una batera de registros, multiplexores, bfer etc. Estos componentes estn en posiciones fijas del dispositivo. La ventaja de la utilizacin de este tipo de tablas es su gran exibilidad: una LUT de k entradas puede implementar cualquier funcin booleana de k variables, y hay 22k funciones posibles. El inconveniente es obvio: ocupan mucho espacio y no son muy aprovechables.

Figura 5: Arquitectura del CLB de la XC2000 Los bloques lgicos configurables de la familia XC2000 se componen de una tabla de lookup con cuatro entradas y un biestable, con lo que puede generar cualquier funcin de hasta 4 variables o dos funciones de 3 variables. El de la familia XC3000 es ms complejo: permite implementar una funcin de 5 variables o dos funciones de 4 variables (limitadas a 5 diferentes entradas, claro). Adems contiene dos biestables y cierta lgica. La familia XC4000 es ya mucho m_as sofisticada. Tiene tres tablas de look-up dispuestas en dos niveles, llegando a poder implementar funciones de hasta 9 variables. En general, los recursos de interconexin son de tres tipos: Conexiones directas, permiten la conexin de las salidas del CLB con sus vecinos ms directos (N, S, E y O).Interconexiones de propsito general, para distancias superiores a un CLB (ms all del vecino). Son pistas horizontales y verticales del tamao de un CLB, pero que se pueden empalmar para crear pistas ms largas. Lneas de largo recorrido, suelen cubrir lo ancho o largo de la pastilla. Permiten conexiones con un retardo mucho menor que uniendo las anteriores.

Wladimir Ortiz Fernndez

WOF

-

7-

Escuela Politcnica Nacional

Sistemas Digitales

El camino crtico de un circuito es el recorrido que, desde una entrada hasta una salida, presenta un retardo mximo. ARQUITECTURA DE LA FAMILIA XC2000 Aunque hoy en da no se encuentran disponibles las FPGAs de esta familia, dado que contienen la arquitectura ms sencilla, vamos a utilizarlas como base para comprender el funcionamiento de este tipo de dispositivos. En la _gura 5 se puede ver cmo es el bloque congelable bsico de las XC2000. Contiene como elementos principales una tabla de look-up de 4 entradas y un biestable D. La tabla de look-up puede reproducir cualquier funcin de cuatro variables o dos funciones de tres variables. De las dos salidas del CLB una se puede registrar, o se pueden dejar las dos combinacionales.

Figura 6: Recursos de interconexin en la familia XC2000

Adicionalmente, en el bloque hay 6 multiplexores que permitirn seleccionar las conexiones que se desea hacer dentro de cada CLB particular. Por ello, en sus terminales de seleccin necesitaran un elemento de memoria con el valor deseado (ver _gura 4). Ntese que la salida del biestable se puede llevar de vuelta a una de las entradas de la LUT, siempre y cuando se configuren adecuadamente los selectores oportunos. Esto es muy _til, pues permite implementar estructuras realimentadas como son contadores o mquinas de estados. Por otro lado, la arquitectura de rutado de la familia XC2000 utiliza tres tipos de recursos de interconexin: conexiones directas, conexiones de propsito general y lineas de largo recorrido. Todos estos recursos se pueden ver en la _gura 6. Las conexiones directas (en la _gura aparecen slo para un CLB) proporcionan enlace desde la salida de un CLB hasta sus vecinos superior, inferior y a la derecha. Si hay que conectar una red a un bloque ms lejano hay que utilizar las conexiones de propsito general, que son segmentos de pista dispuestas horizontal y verticalmente a lo largo de toda la FPGA. En particular, en esta familia hay cuatro segmentos horizontales y cinco verticales por canal. Su longitud est limitada siempre a la distancia fija entre 2 CLBs, por lo que para realizar conexiones ms largas hay que utilizar las matrices de interconexin. Es importante observar que la utilizacin de estos recursos repercutir negativamente en las prestaciones del diseo, pues los conectores de la matriz introducen forzosamente un retardo. Las lneas de largo recorrido se utilizan para conexiones que han de llegar a varios CLBs con bajo skew.Wladimir Ortiz Fernndez WOF-

8-

Escuela Politcnica Nacional

Sistemas Digitales

ESPECIFICACIONES Como ya se ha comentado, vamos a disear una versin simplificada de una FPGA de la familia XC2000 de Xilinx. Todo el diseo debe seguir las especificaciones que acompaan este enunciado (sacadas de [Xil91]), permitindose la realizacin de las implicaciones que se consideren oportunas. A continuacin se darn algunas directrices sobre que implicaciones se pueden hacer y cul es la forma de abordarlas. Ha de quedar claro desde el principio que este diseo tiene un margen de libertad bastante grande. Es decir, NO hay que hacer una FPGA idntica a una de la familia XC2000, sino que se deben adaptar las especificaciones de la misma para poder utilizar las tcnicas vistas en clase: Diseo con doble fase de reloj, elementos CMOS de cualquiera de los tipos estudiados, etc. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques.

ESTRUCTURA La FPGA que se debe realizar constara de 16 Lbs. En principio basta con este tamao, pues el diseo ha de ser completamente regular y estructurado, caracterizando perfectamente a nivel de mdulos, lo que lo har fcilmente ampliable. Recordamos que la meta que se persigue es un diseo correcto, con un trazado simple y bien estructurado. Adems de los 16 CLBs, es necesario implementar los recursos de conexin (tanto las lneas como las matrices de interconexin) y el sistema de control que gestione la programacin de toda la FPGA. Para facilitar la comprensin del problema, hay que ver en el diseo dos estructuras \superpuestas": una correspondiente a la FPGA propiamente dicha, como la ve el diseador final; otra estructura constituye el entramado necesario para realizar la programacin de la FPGA. Esta ltima parte es transparente para el usuario. Es importante destacar que la programacin de la FPGA no es crtica en cuanto a prestaciones, porque se hace una _nica vez y no es determinante. Solo ha de ser correcta. Sin embargo, si interesa optimizar el funcionamiento de la FPGA una vez programada para la implementacin Final. BLOQUES LGICOS La arquitectura del CLB de la XC2000 se presento en la _gura 5, siendo sus componentes principales: Una LUT de 4 entradas y 2 salidas Un biestable. Seis multiplexores, cada uno con sus correspondientes elementos de memoria.

La LUT que vamos a implementar es como se describi en el ejercicio 4 (apartado 3.3). Es decir, ha de ser capaz de implementar dos funciones de 4 entradas independientes1. En Xilinx, el biestable del CLB dispone de una entrada de \reloj" o enable que se puede excitar con tres lneas: La entrada de reloj clk.WOF-

Wladimir Ortiz Fernndez

9-

Escuela Politcnica Nacional

Sistemas Digitales

La entrada de propsito general C. La funcin combi nacional G (salida de la LUT).

Figura 7: Biestable del CLB

Figura 8: Matriz de interconexin

Dado que nosotros trabajamos con dos fases de reloj, no tiene mucho sentido que se puedan utilizar otras seales como reloj, por lo que una implementacin perfectamente vlida del CLB sera la de la figura 7. En cuanto al tipo de biestable, el que se encuentra realmente en el CLB de Xilinx es configurable, de forma que se puede programar como latch D sensible al nivel o biestable D sensible al anco. Para nuestros propsitos sera suficiente implementar uno de los dos tipos de biestable2, sin que sea programable. Con esto el nmero de multiplexores del CLB que nos hacen falta es menor. Cualquier otra simplificacin que se haga al CLB habr de justificarse de forma similar a la realizada en el prrafo anterior, (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques. DESCRIPCIN DETALLADA DE LA LUT Hasta ahora, se ha presentado el CLB de la XC2000 desde el punto de vista de un usuario final. Dado que ahora se va a implementar siguiendo una metodologia full-custom, es necesario conocer ms detalles. En la figura 9 se ve el conjunto de entradas y salidas que tiene realmente la LUT. Como se puede observar, en el smbolo aparecen dos entradas nuevas, las relacionadas con la programacin de la LUT: Las lneas de datos Din, sirven para introducir en la LUT los datos de programacin. La lnea de programacin Prog, su valor sera diferente en funcin del modo en que se est (programacin/funcionamiento normal).

Como ya se ha explicado previamente, la forma inmediata de implementar una LUT es utilizar una memoria RAM esttica. Por ejemplo, considera la tabla de verdad de la funcin f = ab + _c que10 -

Wladimir Ortiz Fernndez

WOF

-

Escuela Politcnica Nacional

Sistemas Digitales

aparece en la _gura 10. Si esta funcin lgica se implementa con una LUT de tres entradas, sera necesaria una RAM de 23 = 8 posiciones, y almacenaremos 1 en la posicin 000, 0 en la posicin 001, y as__ sucesivamente.

Figura 9: Smbolo de la LUT

Figura 10:Implementaci_on LUT con SRAM

Si queremos realizar una LUT de dos salidas lo podemos hacer con 2 memorias de 2k posiciones, o lo que es mejor, con una memoria de k lneas de direccin y 2 bit de palabra. Por supuesto, se est ocupando mucha _rea, pero esta es la mejor forma de realizar una funcin booleana cualquiera. Se deja al alumno decidir la mejor forma de implementar la memoria para conseguir un buen compromiso rea-tiempo de acceso. La equivalencia de terminales entre la LUT y la memoria son los siguientes. Las lneas de entrada corresponden al bus de direcciones; las lneas de datos equivalen a bus de datos de entrada; las salidas (X, Y en nuestro caso) corresponden a bus de datos de salida; y la seal de programacin sera la lnea de lectura/escritura, R/ _W de la memoria. Dependiendo del tipo de implementacin de la memoria se puede necesitar alguna entrada ms (por ejemplo, se puede utilizar alguna seal de reloj para temporizar el funcionamiento de la memoria).

IMPLEMENTACIN DE MEMORIAS CMOS Una memoria CMOS3 integra los siguientes componentes bsicos: La clula de memoria. Puede ser esttica o dinmica dependiendo de la forma de almacenamiento del dato. Las clulas estticas son ms grandes que las dinmicas, pero tienen la ventaja de no necesitar refresco. La forma ms eficiente de distribuir las clulas es colocarlas en una matriz cuadrada, como se muestra en la figura 11. El decodificador de filas, que permite seleccionar la _la de la matriz de clulas de memoria a la que se quiere acceder (tanto para lectura como para escritura). Para ello se utilizarn parte de las lneas de direccin. El decodificador de columnas, que permite seleccionar las clulas de la palabra que se va a leer o escribir entre los datos de la _la proporcionada por el decodificador de _las. Circuito de escritura de las clulas adecuadas (las de la palabra deseada). Circuito de lectura de la fila adecuada (sense ampli_er). Circuito de control de lnea de bit, que acondiciona esta lnea para que sean factibles las operaciones de lectura y escritura.

La forma de distribuir las clulas en la matriz se describe a continuacin.Wladimir Ortiz Fernndez WOF-

11 -

Escuela Politcnica Nacional

Sistemas Digitales

Hay que intentar hacer una matriz lo ms cuadrada posible. Siguiendo la terminologa de la figura 11, supongamos que tenemos una memoria con 2k palabras (por lo tanto con k lneas de direccin) y cada palabra

Figura 11: Estructura de una memoria

Figura 12: R/W de una clula de memoria

tiene b bits. En total tendremos 2kb clulas. Todas estas clulas se ordenan en una matriz de dimensiones n _ m, donde m = 2k???l y n = 2l_ b, siendo l una parte de las lneas de direccin necesaria para hacer la seleccin de las columnas. Hay que intentar que n y m sean lo ms parecido posible para tener forma cuadrada. En la figura 12 aparece representada la relacin existente entre todos los elementos constituyentes de la memoria y su disposicin en las operaciones de lectura y escritura. RECURSOS DE INTERCONEXIN Como se expuso en la seccin 2.3, la arquitectura de rutado de la familia XC2000 utiliza tres tipos de recursos de interconexin: conexiones directas, conexiones de propsito general y lneas de largo recorrido (ver _gura 6). Toda esta estructura se puede implicar para hacerla ms fcil de implementar. En esta seccin hacemos una propuesta de como se pueden realizar. Comenzando por las conexiones de propsito general, sabemos que se basan en la unin de segmentos de pista entre CLBs. Para implicar el rutado vamos a considerar que son 4 lneas tanto en sentido horizontal como en vertical. Necesitaremos dos clulas especiales para realizarlas: La matriz de interconexin (_gura 8), que permite el cruce de pistas horizontales y verticales. No tiene por qu posibilitar la conexin de todas las lneas con todas. Se implementar a utilizando 4 switch de 2x2. Mdulos de conexin de las entradas y salidas del CLB a los segmentos de pista de las conexiones de propsito general. Un ejemplo de cmo se puede hacer estas conexiones se ve en la _gura 13. Como se ve, hay que facilitar el acceso a las entradas del CLB y la salida del mismo. No tiene porque ser el acceso slo a las lneas verticales; esto depender fundamentalmente del trazado que se realice del CLB.

Siguiendo esta propuesta, las conexiones directas que vamos a implementar son las descritas en el manual de Xilinx:Wladimir Ortiz Fernndez WOF-

12 -

Escuela Politcnica Nacional

Sistemas Digitales

La salida X se puede conectar a las entradas A o B del CLB inferior o a las entradas C o D del CLB superior.

Evidentemente esto es para los CLBs internos de la FPGA. Los que estn en la periferia se podrn conectar directamente a las padas de E/S. Por supuesto, las lneas de E/S del CLB no tienen por qu tener la orientacin mostrada en la figura, cada proyecto se realizara con la orientacin que cada grupo estime mejor. En cuanto a las lneas de largo recorrido, se deja a voluntad del diseador implementar las que son programables. En caso de considerarlas, se tendr que elegir que entradas y salidas del CLB tendrn acceso a las mismas. En la _gura 13 se ha presentado como ejemplo dos lneas de largo recorrido y algunas entradas accediendo a las mismas. Hablamos de lneas programables porque hay 2 lneas de largo recorrido que en nuestro caso NO sern programables y s__ son obligatorias: las lneas que llevan las dos fases del reloj, que como se sabe, se deben rutar con especial cuidado. CIRCUITO DE CONTROL DE PROGRAMACIN. Esta parte de la FPGA debe ser una extensin del circuito de programacin de una LUT. Ha de ser un circuito _nico que configure forma secuencial toda la FPGA. Aunque l la familia XC2000 hay varias formas de programar la FPGA, nosotros nos centraremos en el modo ms sencillo: el denominado modo Serial/Slave. En este caso los datos llegan en serie por un pin de entrada de datos de forma sncrona: un reloj (CCLK) valida los datos de la entrada serie (DIN). Se deja a alumno denar el formato de los datos de entrada cuando se est en configuracin. El control de la FPGA se puede hacer desde un microprocesador, resultando el esquema de conexin ms sencillo el que aparece en la figura 14. Resulta evidente que hay que utilizar los recursos de interconexin para realizar la programacin, por lo que sera necesario configurar primero las interconexiones para realizar la programacin de los CLBs. Para programar las LUTs, se sugiere como forma sencilla de implementacin comenzar conjurando todas las lneas para que lleven a, b c y d a todos los CLBs de la FPGA. Luego se utilizaran unas \lneas de seleccin de CLB" que vayan habilitando cada CLB mientras se hace la programacin. Son necesarios unos decodificadores globales que sirvan para llevar el dato a cada _la/columna de CLBs. Esto se puede ver como el acceso en escritura a una memoria. Si se realiza la escritura por _las o columnas, harn falta unos registros de desplazamiento globales. Todos los elementos de memoria se deben enlazar siguiendo una filosofa "scan-path". Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques.

FPGA PROGRAMACIN PASO A PASO FPGAs y microprocesadores son ms similares de lo que usted puede pensar. Aqu hay un estudio sobre cmo programar una FPGA y algunas razones por las que usted desea. Pequeos procesadores son, por ahora, la clase ms grande de venta de computadoras y la base de muchos sistemas embebidos. El primer single-chip microprocesador contena aproximadamente 10.000 puertas de la lgica y 10000 bits de memoria. Hoy en da, conjuntos de puertas programables de campo (FPGA) proporcionan solo 10 millones de chips de acercarse a las puertasWladimir Ortiz Fernndez WOF-

13 -

Escuela Politcnica Nacional

Sistemas Digitales

de la lgica y 10 millones de bits de memoria. microprocesadores con una FPGA.

Figura 1 se comparan uno de estos

Figura 1: Comparacin de la primera a los actuales microprocesadores FPGAs Existen poderosas herramientas para programar estos poderosos chips. A diferencia de los microprocesadores, no slo los bits de memoria, sino tambin la lgica puertas estn bajo su control como el programador. En este artculo se mostrar el proceso de programacin utilizados para el diseo FPGA. Como un programador de sistemas embebidos, que est consciente de los procesos de desarrollo se utiliza con microprocesadores. El proceso de desarrollo de FPGAs es similar suficiente que tendrs ningn problema para la comprensin, pero suficientemente diferentes que usted tendr que pensar de forma diferente a utilizar bien. Usaremos las similitudes a comprender los conceptos bsicos, y luego discutir las diferencias y la forma de pensar en ellas. SIMILITUDES El cuadro 1 muestra las etapas implicadas en el diseo de sistemas empotrados con un microprocesador y un FPGA. Este lado de la otra comparacin le permite evaluar los dos procesos y ver cmo son similares. Cuadro 1: paso a paso el proceso de diseo de microprocesadores y FPGAs Microprocesador FPGA Diseo arquitectnico Diseo arquitectnico Eleccin (C, Java) de la lengua Eleccin de la (Verilog, VHDL) Programas de edicin lengua

Programas de edicin Compilar (. DLL,. OBJ)

programas Compilar programas Sntesis de los programas (. EDIF)

Vincular los programas de Programas de colocacin y (. EXE) ruteoWladimir Ortiz Fernndez WOF-

14 -

Escuela Politcnica Nacional

Sistemas Digitales

(. VO. SDF. FFT) Carga de los programas de Carga de programas para la ROM FPGA Depuracin programas de P Documentacin programas Entrega de programas de los Depuracin de los programas de FPGA de Documentacin de programas Entrega de programas

DISEO ARQUITECTNICO. La fase de diseo arquitectnico-es sorprendentemente similar. Aunque las personas se sostienen las filosofas de diseo, no es raro realizar un "primer corte" en la programacin en un pseudolenguaje que puede ser refinado y traducido a un idioma especfico como, por ejemplo, el montaje, C + +, JAVA o. Describo mi primera FPGA diseo arquitectnico en un pseudo-lenguaje C luego traducirlo a Verilog para una FPGA. Por lo tanto, la capacidad de expresarse en C es un buen comienzo en el aprendizaje Verilog. Cuestiones arquitectnicas podra llenar un libro, por lo que nos enfocaremos en los problemas del desarrollo. Debido a entender la edicin, compilacin, montaje, la vinculacin, y la carga de microprocesadores en la programacin, puede referirse a esta edicin, compilar, sintetizar, colocacin, rutas, y la carga de la programacin en FPGA. EDICIN No slo es la sintaxis de C-Verilog similares, pero, ya que es 100% ASCII, puede utilizar cualquier editor de archivos para preparar fpga.v. Nada nuevo aqu. COMPILAR El proceso de compilar un programa para el microprocesador combina los archivos modificados y se basa, lgicamente, una correcta secuencia de bits que se utilizan para controlar la secuencia de las puertas lgicas. Estas puertas de escribir datos en los autobuses, en las cerraduras y los registros, en los puertos, y en todos los canales. Las puertas se han fijado las relaciones diseados para realizar funciones fijas. El lenguaje ensamblador instrucciones representan estas funciones. As microprocesador compiladores producir lenguaje ensamblador programas que luego son ensambladas dentro de poco, o directamente producir patrones de los bits a la unidad y cerrar las puertas y llenar los registros y la memoria. La operacin anloga en la FPGA de programacin es la compilacin de Verilog lgica de transferencia en el registro (RTL) netlists. Como el nombre lo implica, los datos se transfieren a los registros, con sujecin a la hora de algunas condiciones. En esta etapa se aleja de FPGA de programacin de microprocesadores en la programacin que un proceso de sntesis se requiere para producir bits (intermedio o los objetos que se pueden convertir en bits) que el control de puertas y llenar los registros y recuerdos en una FPGA. Este nivel se denomina nivel de la puerta lgica, ya que describe las puertas de la lgica que el sistema estar integrado. El formato de salida es normalmente un Formato de intercambio de Diseo Electrnico (EDIF) archivo. Hay una gran diferencia entre la compilacin y sntesis, y usted tiene que estirarse para abarcar algunos ella. Considerando que el compilador produce bits para el control de los patrones fijos puerta (el microprocesador decodificadores, registros, unidad aritmtica lgica, y as sucesivamente), la puerta de sintetizador define patrones descritos por la lgica del programa. EsWladimir Ortiz Fernndez WOF-

15 -

Escuela Politcnica Nacional

Sistemas Digitales

decir, su programa se sintetiza la lgica, o en mapas, puertas lgicas, no en el procesador de instrucciones que controlan las estructuras multigate. Esto es absolutamente increble, y la buena FPGA programadores dar gracias todos los das para vivir en la rara vez en la historia (despus de 1990 +) cuando se puede disear arquitecturas con las palabras y, a continuacin, una sntesis de su lgica en (principalmente silicio) que ejecutan las puertas de su lgica. No se deje llevar, pero es absolutamente maravilloso. VINCULACIN Vinculacin de una tarde-tal vez a la programacin de 1950. Ordenadores y programas anteriores simplemente los bits en la consola interruptores, y, por ende, en los registros. (Leer sobre el desarrollo de la vinculacin en la barra lateral.) Los bits de los productos basados en el microprocesador proceso de compilacin generalmente no controlan directamente las puertas, sino que debe estar conectado a otros patrones de bits. Esto es as porque la mayora de los programas que se ejecutan bajo el control de un sistema operativo y debe estar conectado, o vinculados, para el sistema operativo. De hecho, la ubicacin en memoria de la compilado bits por lo general es desconocido y no se determina hasta el enlace y la carga. Adems, puede haber programas existentes en una librera que tambin debe estar vinculado con el programa compilado antes existe un producto til. El proceso de sntesis, como lo hemos discutido, produce patrones de bits, en un formato intermedio. Compilamos Verilog RTL netlists para, a continuacin, a sintetizar Verilog EDIF, entonces el lugar y la va para producir EDIF HEX o TTF archivos que se pueden cargar en una FPGA. Estos patrones de poco terminar el control de puertas y la lgica de llenado de memoria y registros. De la misma manera que C y otros programas se incluyen los objetos definidos en el (posiblemente de terceros), las bibliotecas, los programas pueden incluir la FPGA o importacin de partes de sistemas de propiedad intelectual de terceros, en forma de programas ejecutables-FPGA u objetos. Tambin, de la misma manera que la vinculacin y el proceso de carga de los sistemas integrados de diseo conecta diversos objetos del sistema, los subsistemas, o sistemas como superpotencia del sistema operativo, incluida la biblioteca de objetos (y las cargas o los lugares especficos en las ubicaciones de la memoria), el lugar y la ruta funcin de diseo de FPGA en lugares en los subsistemas de sntesis FPGA lugares y conexiones (enlaces microprocesador ~ FPGA rutas) entre estos subsistemas, lo que permite su funcionamiento como un sistema integrado. La vinculacin real y carga de los bits compilado es esencialmente un proceso de montaje, en una dimensin, los patrones distribuido poco ms de un conjunto de direcciones de memoria disponible lineal. FPGA lugar el proceso y la ruta se ajuste, en dos dimensiones, los patrones de bits (lgica subsistemas) a travs de una matriz bidimensional de puertas lgicas disponibles, y las rutas de autobuses entre la lgica de estos subsistemas, segn sea necesario. La similitud en los procesos es evidente. Historia de vnculos Principios de las computadoras tenan un "parche bordo" que se vea algo as como el telfono de las juntas de revisin de la dcada de 1940 donde "cables de red" se conecta en "tomas" para hacer las conexiones entre los diversos autobuses y registrar las entradas y salidas. La revisin de las tablas y'40s aos 50 se convirti en el poco tramo microprogramming de la dcada de 1970, donde, una vez ms, la atencin se centr en el control de puertas lgicas, y la revisin de los cables se aplicaron como "alambre de recapitulacin" conexiones. FPGAs En el enrutamiento deWladimir Ortiz Fernndez WOF-

16 -

Escuela Politcnica Nacional

Sistemas Digitales

cables de red son las conexiones entre las puertas. FPGAs principios que figuran puertas numeradas entre los cientos y miles. El tamao no es suficiente para aplicar los sistemas, pero fue capaz de aplicar los tipos de circuitos construido con circuitos integrados de mediana escala (decenas de puertas), que ejecut el "pegamento lgica" que se celebr microprocesadores y chips de sofisticados perifricos juntos. Por lo tanto, las primeras aplicaciones prcticas de FPGAs consisti en la sustitucin de muchos chips de lgica de cola con un FPGA. Debido a que estos circuitos ya estn completamente descritos por diagramas de circuito, la primera FPGA editores grficos utilizados captura, es decir, los circuitos se redibuja en el editor, y ste era el de entrada de informacin. N de alto nivel de idiomas se utilizan para programar la FPGA en este proceso, simplemente de edicin de grficos y basados en el tiempo de simulacin de formas de onda. CARGANDO Por ltimo, al igual que los programas estn incorporados a menudo integradas en fsica ROM, flash, o descargado en vivo, programas de FPGA (compilado, sintetizado, colocado, y encaminado) debe estar integrada en la fsica FPGAs. La programacin real puede ser un archivo. HEX o similar. Los programadores suelen descargar o grabar los bits de estos archivos en el hardware. Si no voltil, esto es una propuesta de una sola vez. Si no, es una descarga-en-el encendido proposicin. Existen muchas variaciones con FPGAs como con microprocesador basado en los sistemas incorporados, pero al final, en un microprocesador que funcione a base de producto, los bits compilado, vinculados entre s, y cargados deben "entrar en" la memoria fsica para el control de las puertas del transformador, y en un funcionamiento basado en FPGA producto, los bits recopilado, sintetizado, colocado, y dirigidas, deben "entrar en" la FPGA, para la aplicacin de las puertas del sistema. DEPURAR PROGRAMAS Todos los programadores experimentados saben que los programas complejos, incluso subprogramas, no ejecute correctamente la primera vez. La primera vez que ver la forma de resolver un problema, tienden a estar contentos, (es posible!) Y luego subestimar el tiempo necesario para aplicar la solucin. Esto se debe a que nuestros poderes de la abstraccin, basndose en la experiencia, nos permiten ver las soluciones, sin preocuparse por cada detalle meollo. Pero la dura verdad es que el sistema fsico en el que nos exige la incorporacin de nuestros programas que cada meollo detalle debe ser manejado para que funcione. Sin duda, usted ha tenido la experiencia de la fijacin de un nico bit (o bandera) que caus un programa falle de repente ejecutarse correctamente. Aleluya! Funciona. No puedo dormir ahora. De todos modos, las cosas no funcionan fuera de la puerta. Por lo general, tienen que poner ellos y ver lo que hacen y donde su expiracin. En el programa de desarrollo de sistemas embebidos, que suelen utilizar depuradores, simuladores, emuladores y. Estas herramientas nos permiten el paso a travs de la ejecucin del programa y observar los efectos sobre las banderas, registro de contenidos, de memoria, y as sucesivamente, y para tratar de coincidir con lo que esperamos en un determinado lugar y tiempo con lo que vemos, o en el simulador emulador. Simulacin frente a la emulacin: Depuracin FPGA en el diseo se basa principalmente en la simulacin. Usted puede ver por qu. La emulacin, en el contexto de programas deWladimir Ortiz Fernndez WOF-

17 -

Escuela Politcnica Nacional

Sistemas Digitales

microprocesadores incorporados, por lo general se refiere a la ejecucin de programas en especial en la emulacin de circuito (ICE) de hardware diseados para 1) ejecutar exactamente igual que la mquina objetivo y 2) proporcionar visibilidad, acceso y control de la mquina objetivo en potentes medios, con la emulacin de momento exactamente igual al objetivo de la sincronizacin. As pues, la esencia de la emulacin se basa en hardware fsico que reproduce el microprocesador, mientras que la adicin de las puertas de las puertas destinadas para la depuracin. Esta metodologa funciona porque el microprocesador consta de un conjunto de puertas, la aplicacin de la CPU, entre otros. El FPGA no tiene un "fijo" patrn de las puertas, en el sentido de la CPU, de hecho, objeto de programas de la FPGA es definir un modelo de puertas, a travs del proceso descrito en este documento, que llevar a cabo nuestro diseo. Y nuestro diseo ser diferente de cualquier otro diseo. Por esta razn, no existen emuladores de FPGA, en el sentido en el circuito de emuladores. Los ms rpidos procesadores de hoy en da no se puede emular en hardware, puesto que ya se ejecutan tan rpido como sea posible, y la CIE circuitos adicionales aade puerta niveles, por tanto, retardar la CIE y la prevencin de continuar con el procesador. Por esta razn, los diseos se centran en el procesador incorporado en la depuracin de apoyo. Este enfoque es un tanto similar al diseo de FPGA, que es til para construir en depurar las ayudas. Porque usted est acostumbrado a la creacin de ayudas en los programas de depuracin, de las declaraciones sobre IMPRESIN arriba, usted comprender la importancia de este punto, y ser capaces de traducir su comprensin en el mbito FPGA. La mayora de la programacin de microprocesadores, en particular incrustado programacin, se basa en el supuesto de que sofisticados sistemas operativos y dispositivos perifricos son "conectado" el programa, a travs de interfaces de la aplicacin. As pues, se centra en la depuracin dentro de la mquina y no pretende simular el sistema operativo o de los perifricos, sino que trabaja con ellos. Testbenches en FPGA: La mayora de los sistemas autnomos FPGA sistemas conectados al mundo real, y el funcionamiento en la interaccin con el mundo real. Por lo tanto, una gran parte de la depuracin y la prueba se refiere a simular el mundo real al que se conceden la FPGA. En referencia a la forma lgica de los circuitos se depurado histricamente, esto se llama el testbench y es considerada como un todo-en otras palabras, puede ser compilado en su conjunto. Normalmente a travs de pasos de simulacin del funcionamiento del testbench, que estimula la FPGA. El proceso de simulacin seala las transformaciones y las traducciones de las seales que se propagan a travs de la FPGA de las clavijas de entrada y proporciona las respuestas que, eventualmente, llegar a una salida de la clavija. Porque probablemente habr decenas o cientos de miles de puertas, que, evidentemente, no ven la totalidad de ellas, pero la ms significativa que en el rea de inters. Por ejemplo, un buffer FIFO puede ser de 48 bits de ancho y miles de palabras, pero la puerta de salida que ms le interesa en este momento puede ser la seal Buffer_Full, por lo que este se muestra en la pantalla de simulacin, junto con otras seales de inters. Este proceso se asemeja un poco centrado en las banderas o semforos en la programacin de microprocesadores. Puede agrupar mltiples seales. Por ejemplo, ocho cables puede dar un nombre, Data_In_Bus, y los valores numricos que aparecen en el autobs se puede mostrar, en lugar de mostrar todas las ocho lneas en constante cambio. Variables de estado se puede dar nombres y se muestran ASCII. En el mismo sentido que usted lo desea, puede centrarse en la ejecucin del programa dentro de una subrutina, puede que quiera observar slo la seal de actividad en un subsistema. Una vez que aprenden las herramientas, se convierte en algo natural para depurar un FPGA subsistema que ha diseado. En pocas palabras: la depuracin de FPGA se realiza mediante software de simulacin y utilizando su hardware actual. Cualquier uso de la depuracin de su hardware actual debe ser diseada por usted.Wladimir Ortiz Fernndez WOF-

18 -

Escuela Politcnica Nacional

Sistemas Digitales

Comienzo de la pgina y Netlist ~ principal: Aunque no es realmente una parte del proceso, es til comprender que la salida de la FPGA es un proceso de diseo netlist o de la lista de las redes o los cables que conectan los productos puerta a puerta otros insumos. Adems, hay un nivel superior a partir de la cual desciende todo. Piense en la parte superior como el principal punto en un microprocesador programa donde el programa se inicia. Aunque puede haber 50 o ms mdulos que se crean en forma independiente una FPGA diseo, cuando el proceso haya finalizado, todos se vincular en el netlist. Cualquier mdulo en la lista no tendr ningn efecto. Esto es anlogo a una subrutina que nunca es llamado. Si no hay conexin a un mdulo, el mdulo no puede hacer nada. LA DOCUMENTACIN DE LOS PROGRAMAS: No puedo pensar en ninguna diferencia significativa entre la buena prctica en la documentacin de microprocesadores basados en sistemas embebidos basados en FPGAs y los sistemas integrados de programacin. El contenido obviamente difieren ligeramente, pero la prctica y los procedimientos son los mismos. LA ENTREGA DEL PRODUCTO: FPGAs son sorprendentemente similares a los microprocesadores en la entrega efectiva de trabajo de hardware y software. El microprocesador de hardware, consejos, fuentes de alimentacin, las conexiones, debe estar correctamente diseado, y el software debe ser quemado o descargarse como se ha descrito anteriormente. El FPGA hardware, consejos, fuentes de alimentacin, conexiones, etc, debe estar correctamente diseado, y el software debe ser quemado o descargarse como se ha descrito anteriormente. Si el hardware es correcta, el software puede evolucionar. Esto permite correcciones de errores y de la caracterstica adicional. Esto es cierto en el caso de los microprocesadores y FPGAs. El Verilog o VHDL lenguaje de descripcin de hardware (HDL)-cada uno es un diseo de alto nivel del idioma ofrece un rpido tiempo de salida al mercado utilizando FPGAs. El sistema permite el diseo HDL, depurar y verificar todos en el mismo medio ambiente. Al igual que con el diseo de microprocesadores, diseo de FPGA puede ser impulsado por la lnea de comandos o IDE basado. DIFERENCIAS La mayor parte de lo que hemos discutido slo se ha centrado en las similitudes entre la programacin de microprocesadores incorporados y FPGA programacin. Ahora ver algunas diferencias significativas. Unsynthesizable: Probablemente la mayor sorpresa para los programadores experimentados incrustado es que los programas que son funcionalmente bien, que se ejecutan, y puede ser simulada, y producir resultados correctos, no podr ser synthesizable. Qu significa esto? Esto significa que usted puede escribir "buenos" programas funcionales que son imposibles de convertir en un netlist que puede ser asignada a una FPGA. Por qu es esto? Verilog principalmente porque es un "superconjunto" de synthesizable sintaxis. Histricamente, Verilog fue diseado como un lenguaje de simulacin para la simulacin de sistemas de lgica. Fue slo despus de que la tecnologa de sntesis fue capaz de convertir en realidad la salida de RTL de la simulacin en netlists compilador basado en la puerta a nivel de las estructuras de hecho se encuentra en FPGAs. Por lo tanto, es comprensible que todo el lenguaje de simulacin, herramientas diseadas antes de la sntesis, no es totalmente synthesizable. Qu significa esto para usted? Esto significa que el problema es ms complejo de lo que inicialmente pareca. Cmo crear programas synthesizable est fuera del alcance de este artculo, pero es un tema para futuros artculos.Wladimir Ortiz Fernndez WOF-

19 -

Escuela Politcnica Nacional

Sistemas Digitales

Por qu vas a querer usar un idioma que contienen nonsynthesizable construye? Hay varias razones. Veremos a dos. En primer lugar, es posible que desee para representar un sistema que ms tarde se dividi en los subsistemas de software y hardware. Es ms fcil disear un sistema completo utilizando el idioma y luego la restriccin de la parte de hardware para el diseo synthesizable construcciones. Una razn ms general es la siguiente. FPGA diseo debe incluir siempre una testbench, que es el entorno que proporciona los insumos, incluida la de reloj (s) y datos, y acepta los resultados de la FPGA. Es el software que describe el mundo como el "visto por" FPGA alfileres. Este mundo est compilado para ser simulado, pero no sintetizada. Piense en esto. El cdigo en la FPGA debe ser asignada a puertas lgica real en el FPGA, por lo tanto, por definicin, debe ser synthesizable que, puesto que la sntesis es el proceso de convertir el idioma en RTL puerta nivel de idiomas y, por tanto, en una matriz de puertas programables de campo. Sin embargo, el cdigo "fuera de" la FPGA no se va a poner dentro de una FPGA. Qu significa esto para usted? Esto significa que el problema es ms complejo de lo que inicialmente pareca. Cmo crear programas synthesizable est fuera del alcance de este artculo, pero es un tema para futuros artculos. Por qu vas a querer usar un idioma que contienen nonsynthesizable construye? Hay varias razones. Veremos a dos. En primer lugar, es posible que desee para representar un sistema que ms tarde se dividi en los subsistemas de software y hardware. Es ms fcil disear un sistema completo utilizando el idioma y luego la restriccin de la parte de hardware para el diseo synthesizable construcciones. FPGAs son sorprendentemente similares a los microprocesadores en la entrega efectiva de trabajo de hardware y software. El microprocesador de hardware, consejos, fuentes de alimentacin, las conexiones, debe estar correctamente diseado, y el software debe ser quemado o descargarse como se ha descrito anteriormente. Una razn ms general es la siguiente. FPGA diseo debe incluir siempre una testbench, que es el entorno que proporciona los insumos, incluida la de reloj (s) y datos, y acepta los resultados de la FPGA. Es el software que describe el mundo como el "visto por" FPGA alfileres. Este mundo est compilado para ser simulado, pero no sintetizada. Piense en esto. El cdigo en la FPGA debe ser asignada a puertas lgica real en el FPGA, por lo tanto, por definicin, debe ser synthesizable que, puesto que la sntesis es el proceso de convertir el idioma en RTL puerta nivel de idiomas y, por tanto, en una matriz de puertas programables de campo. Sin embargo, el cdigo "fuera de" la FPGA no se va a poner dentro de una FPGA. FPGAs son sorprendentemente similares a los microprocesadores en la entrega efectiva de trabajo de hardware y software. El microprocesador de hardware, consejos, fuentes de alimentacin, las conexiones, debe estar correctamente diseado, y el software debe ser quemado o descargarse como se ha descrito anteriormente. Una razn ms general es la siguiente. FPGA diseo debe incluir siempre una testbench, que es el entorno que proporciona los insumos, incluida la de reloj (s) y datos, y acepta los resultados de la FPGA. Es el software que describe el mundo como el "visto por" FPGA alfileres. Este mundo est En primer lugar, es posible que desee para representar un sistema que ms tarde se dividi en los subsistemas de software y hardware. En primer lugar, es posible que desee para representar un sistema que ms tarde se dividi en los subsistemas de software y hardware. Es ms fcil disear un sistema completo utilizando el idioma y luego la restriccin de la parte de hardware para el diseo synthesizable construccione

Wladimir Ortiz Fernndez

WOF

-

20 -

Escuela Politcnica Nacional

Sistemas Digitales

La mayor parte de lo que hemos discutido slo se ha centrado en las similitudes entre la programacin de microprocesadores incorporados y FPGA programacin. Ahora ver algunas diferencias significativas. El FPGA hardware, consejos, fuentes de alimentacin, conexiones, etc, debe estar correctamente diseado, y el software debe ser quemado o descargarse como se ha descrito anteriormente. Si el hardware es correcta, el software puede evolucionar. Esto permite correcciones de errores y de la caracterstica adicional. Esto es cierto en el caso de los microprocesadores y FPGAs. El Verilog o VHDL lenguaje de descripcin de hardware (HDL)-cada uno es un diseo de alto nivel del idioma ofrece un rpido tiempo de salida al mercado utilizando FPGAs. El sistema permite el diseo HDL, depurar y verificar todos en el mismo medio ambiente. Al igual que con el diseo de microprocesadores, diseo de FPGA puede ser impulsado por la lnea de comandos o IDE basado Va a ser utilizado por el diseador para simular el medio ambiente de la FPGA, mientras que la depuracin. Por esta razn, es til para permitir la programacin de alto nivel que simplifican la construccin la construccin de la testbench. Si la construccin testbench se han limitado a synthesizable se construye la fuerza para utilizar el diseador de nivel inferior abstracciones que es necesario. La Figura 2 muestra la synthesizable y nonsynthesizable partes de un diseo. .

Figura 2: Synthesizable y nonsynthesizable porciones de diseo Este es un punto muy importante, por lo que repetirla. El lenguaje Verilog, diseado inicialmente para la simulacin lgica, ofrece potentes construcciones de alto nivel que son tiles para simular el "mundo real" a los que la FPGA se conectar. La construccin no se asigna directamente a las estructuras lgica FPGA o se convierta en una puerta de nivel netlist. Puesto que slo un subconjunto de la lengua es Verilog synthesizable, que testbench diseo es ms fcil, pero la programacin FPGA, de por s, es ms difcil. Las versiones ms recientes de Verilog (en el mercado "real pronto") cambiar la "mezcla" de synthesizable a nonsynthesizable idioma abstracciones, pero este problema probablemente siempre estar con nosotros hasta cierto punto. C Y VERILOG Durante los ltimos aos, ha habido un esfuerzo por ampliar Verilog aadiendo lenguaje C construye. El esfuerzo ahora est culminando con las normas IEEE procesos, pero la situacin est sin resolver en este momento, con la (esperemos remota) posibilidad de que el idioma se dividi en dos versiones. Los problemas son legales, comerciales, y conceptual. Tambin es justo decir que la mayora de los programadores Verilog son poco entusiastas sobre el proceso, pero las empresas involucradas piensan que podra vender ms si el software se vuelve ms fcil para el ejrcito deWladimir Ortiz Fernndez WOF-

21 -

Escuela Politcnica Nacional

Sistemas Digitales

programadores de C a participar en el diseo de FPGA, por lo tanto, hay verdadera presin para proceder con proceso de las normas. Debido a las incertidumbres se resuelvan durante el prximo ao o as, no se centrar en esta situacin aqu. La situacin es anloga a la asamblea el idioma de programacin C vs historia. Cuando los recursos son escasos, vale la pena el diseo de manera eficiente, por lo tanto, el lenguaje ensamblador es el mejor. Cuando se liberan los recursos, la eficiencia del proceso de diseo domina, programacin y lenguaje C se prefiere. FPGA en el mundo, los recursos an no son libres, por lo tanto, Verilog es el idioma de su eleccin. Esto probablemente cambiar con el tiempo. Tenga en cuenta que una interface de Verilog ya existe, como se muestra en la Figura 3. Tambin hay variantes de FPGAs que contienen un microprocesador de silicio en el ncleo junto con los circuitos FPGA. En tales casos, los microprocesadores pueden programarse usando C mientras que las puertas se FPGA programado usando Verilog o VHDL. El uso de C en el cdigo funcional testbench hace sentido, porque no es necesario synthesizable.

Figura 3: Testbenchs y depuracin de cdigo en C Para los equipos de programacin de sistemas embebidos que quieran ampliar sus capacidades en el diseo de FPGA, recomiendo que los que tienen menos conocimiento de hardware debera centrarse en testbench diseo, mientras que los ms capaces de centrarse en el diseo de hardware aprender a escribir cdigo synthesizable.

OPTIMIZACIN Ahora que tenemos un panorama ms completo de diseo de FPGA, vamos a comparar la diferencia en los resultados antes y despus de la colocacin y el enrutamiento. Cuando el sistema est compilado en Verilog, la salida es una RTL netlist. Cuando la entrada a un sintetizador, el Verilog se convierte en una puerta de nivel netlist, susceptible de ser asignada a FPGA hardware (en el supuesto xito de la sntesis.) La mayora de los sintetizadores pueden producir una descripcin en lenguaje Verilog de esta puerta a nivel de cdigo. La belleza es que esta puerta nivel Verilog puede ser compilado y simulado. Por lo tanto, podemos de depuracin en la propia puerta. La simulacin de la RTL Verilog se llama simulacin funcional, mientras que la simulacin del sintetizador Verilog se llama la puerta de salida a nivel de simulacin, como se muestra en la Figura 4. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas oWladimir Ortiz Fernndez WOF-

22 -

Escuela Politcnica Nacional

Sistemas Digitales

pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques.

Figura 4: El proceso de programacin FPGA Cul es la diferencia entre la puerta y funcional a nivel de simulacin? Una diferencia es que, como compiladores de C pueden optimizar cdigo C, sintetizadores pueden optimizar netlists FPGA. De hecho, si especifica el objetivo, los sintetizadores pueden optimizar para cumplir su objetivo. Los objetivos son tpicamente la zona vs demora. rea de optimizacin intento de utilizar el menor nmero de puertas (rea de silicio) en una FPGA, a expensas de la velocidad de ejecucin. Demora intentos de optimizacin para maximizar la velocidad de ejecucin, aunque la zona ms FPGA es obligatorio. El resultado neto es que el cdigo funcional que escribi en Verilog RTL en el nivel pueden tener diferentes aplicaciones, y las seales de que usted utiliza para depurar el cdigo funcional se han optimizado de la existencia. Es decir, que pueden desaparecer en la ltima puerta de la aplicacin a nivel. As, a pesar de que has probado a fondo y simular el cdigo RTL, querr hacer lo mismo en la puerta nivel. Sintetizadores tpicamente permiten limitaciones que se especifican en el marco del proceso de optimizacin. Una de esas limitaciones es b para evitar que el sintetizador de hacer lo que quiera con elementos especficos del diseo. Otra limitacin es preserve_hierarchy como una alternativa a aplanar el diseo. Porque las fronteras jerrquicas pueden prevenir o limitar la optimizacin, los sintetizadores, que aplanar el diseo se suelen ofrecer ms resultados ptimos. 0 SDF Y COPIA DE LA ANOTACIN Bien, ahora estamos listos para la ltima gran diferencia entre el microprocesador y los procesos de programacin FPGA. As como hay casos en donde la velocidad de diseo de microprocesadores de ejecucin es crtica, lo mismo ocurre con el diseo de FPGA. Cuando microprocesador cdigo debe ser el tiempo, la velocidad de reloj y el nmero de ciclos por instruccin se puede utilizar para calcular la velocidad de ejecucin, que ser fuertemente dependientes de procesador. Cuando se produce un sintetizador a nivel Verilog puerta para una FPGA, es fuertemente dependiente de FPGA, es decir, los retrasos asociados con los proveedores especficos FPGA estructuras son conocidas y pueden ser usados para calcular velocidades de operacin. As pues, la simulacin de la puerta a nivel de cdigo para un FPGA es realista en este sentido.Wladimir Ortiz Fernndez WOF-

23 -

Escuela Politcnica Nacional

Sistemas Digitales

Pero recuerde, an nos queda lugar a esta puerta y la va a nivel netlist. Esta operacin se demora para agregar las rutas ms largas, con lo que la ralentizacin de la velocidad de ejecucin final. Si su diseo debe cumplir algunas especificaciones del mundo real, tales como USB 12MHz (reloj de 48MHz) o 480MHz USB2.0 luego debe ejecutar en esta velocidad, o bien no han resuelto el problema. Cmo se puede saber si la ruta de cdigo se ejecutar con la suficiente rapidez? Para resolver este problema, el lugar y la ruta de los programas (suministrados por el FPGA vendedores) tambin producen Verilog produccin y producir archivos de SDF, que son archivos en el formato estndar de demora, que la captura de los retrasos asociados con la ruta y colocar netlist. Simuladores SDF puede utilizar esta informacin para anotar de nuevo la puerta a nivel de cdigo, lo que permite la simulacin de diseo final FPGA en su ms exacto. Debido a que la FPGA elementos estn bien caracterizados, con la configuracin tpica y mantenga veces, el simulador puede detectar el incumplimiento de estas especificaciones. Grfica sobre las formas de onda, los fracasos suelen aparecer en rojo, mientras que el tiempo es bueno "en verde" cuando la frecuencia de reloj deseado se utiliza. Cuando la FPGA se ejecuta en el green con la frecuencia de reloj que desee utilizar, y se comporta en el testbench como se desea, usted tiene un diseo FPGA que est listo para ser descargados a los equipos de pruebas del mundo real. Quizs deberamos recordar que las tres versiones del cdigo de simulacin FPGA, RTL, funcionales, y la puerta de nivel por lo general utilizan el mismo cdigo testbench, es decir, no hay tres versiones de la testbench. EN REVISIN Hemos visto que, conceptualmente, la programacin de microprocesadores y programacin FPGA seguir caminos casi idnticos. Son ambos basados en el diseo arquitectnico y se describen en trminos de C como de alto nivel, que se recopilan o sintetizados, posiblemente en conjuncin con terceras partes la biblioteca de objetos. El resultado de este proceso est vinculado y cargado en una direccin de memoria o puesto dimensin y ruta en dos dimensiones puerta matrices, de tal forma que estos patrones fijos poco se puede descargar correctamente diseado para el hardware y, finalmente, deben hacerse a la funcin del modo que se dise la arquitectura. Cuando las puertas se preciosos entidades y herramientas 100% de propiedad, que hizo final sentido limitado a organizar estas puertas universalmente utilizado en objetos, tales como los registros de la CPU, ALUs, decodificadores de instrucciones, y la direccin de descodificadores. A continuacin una serie de instrucciones que una relinked y estos elementos, de modo que, por ejemplo, dos salidas de la CPU registro podra estar conectado (a travs de autobuses) a una entrada de UTA, la UTA salida conectado a un registro de destino y, a continuacin, la ALU entrada conectado (a travs de autobuses) a una direccin de memoria, y la UTA salida conectado a un registro diferente, y as sucesivamente y as sucesivamente. Tiene perfecto sentido. Cuando la escala y, por lo tanto, la economa cambia, todo cambia. Cuando las puertas ya no son preciosos, pero son bsicos, los elementos fijos el enfoque ya no tiene tanto sentido. El monstruoso desarrollo de idiomas, herramientas, dispositivos de E / S, las normas, y as sucesivamente seguir el desarrollo y la aplicacin de CPU vivo durante dcadas, si no siglos, pero la economa son ahora de tendencias y ms en la direccin FPGA. Esto ha sido dado otro impulso econmico en relacin con ASICs. El costo de las reparaciones de hardware, es decir, los ASIC-est aumentando drsticamente con la disminucin de ancho de lnea y el aumento de la densidad de la puerta, haciendo la tecnologa FPGA incluso ms relevante para los diseadores de sistemas embebidos. Hoy ms de un milln de puertas disponibles, maana 10 millones, acompaados en un nico chip millones de bits de memoria. Usted puede hacer lo que quieras, describiendo en un lenguaje de programacin, tales como Verilog, y pasando por el proceso descrito anteriormente. FPGA ELEGANCIA Una diferencia en el diseo de microprocesadores y FPGA es subjetiva. Hay una asombrosaWladimir Ortiz Fernndez WOF-

24 -

Escuela Politcnica Nacional

Sistemas Digitales

elegancia y "limpieza" del diseo de FPGA vs microprocesador programa de diseo. En el diseo despus del diseo, he realizado cunto tiempo se gasta en la programacin de sistemas embebidos "prepara" para hacer algo. Esto implica la creacin de registros o datos en memoria y la creacin de enlaces en otros registros, para obtener alguna fuente, hacer algo, y ponerlo en algn lugar. Los programadores no ver esta realidad, al igual que los peces probablemente no ve el agua, porque esa es la naturaleza del proceso. Es menos visible, con lenguaje de alto nivel y ms visible con el lenguaje ensamblador, pero siempre existe. En este FPGA "prepara" no se dan realmente. Todo es el lugar que le corresponde y pasa de una sola vez, en un ciclo de reloj. Esto no quiere decir que no se puede disear registros, autobuses, y en FPGAs ALUs, pero usted encontrar que usted realmente no pasar mucho tiempo "preparndose para hacer algo." No voy a impulsar este punto, porque tiene el diseo de FPGAs antes de que te golpea en la cabeza. Pero recuerde: usted lee aqu primero. Otra diferencia significativa con FPGA diseo radica en el carcter paralelo de los procesos de FPGA. En lugar de un nico programa basado en contrarrestar "locus de control", tpicamente una FPGA puertas todos los relojes a la vez. De este modo usted puede tener muchos procesos ocurren en paralelo, en lugar de secuencialmente. Esto tambin lleva algn tiempo acostumbrarse a porque es tan diferente de la forma programadores piensan. Por qu le gustara programar una FPGA, en primer lugar? Bueno, si usted es el diseo de programas de contabilidad, no. Sin embargo, muchos sistemas empotrados estn estrechamente unido al mundo real, y hay muchos problemas que simplemente ocurra demasiado rpido, para ser manipulados en el software. En este caso, puede dejar que sus competidores tienen estos problemas (que suelen ser caros) y se puede seguir con el ms lento, ms fcil (de bajo perfil) problemas. O usted puede programar soluciones FPGA. No es obligatorio. Es una oportunidad. Ed. Klingman trabajado como fsico en la NASA de investigacin durante siete aos, y luego fund Ciberntico Micro Systems, Inc, que ahora celebra su 25 aniversario. Es autor de los libros de texto Prentice-Hall microprocesador Diseo de Sistemas, Vol. I y II. Y numerosos documentos tcnicos, y ha sido galardonado con 20 patentes de EE.UU..

LACA PROTOTIPO FPGA PARA APLICACIONES DE PROCESADO DE SEAL Las FPGAs se han demostrado eficaces para el desarrollo de prototipos que pongan en prctica nuevos diseos o algoritmos. Sin embargo las placas de prototipo actuales tienen varios problemas que dificultan la medicin de parmetros importantes para la prueba y la puesta a punto de tales diseos. Por esta razn se ha llevado a cabo el diseo y la implementacin de una nueva placa prototipo que conlleva una serie de diferencias con respecto a las ya existentes con el fin conseguir tres objetivos: poder implementar algoritmos realizados tradicionalmente con DSP, el empleo de interfaces de testeo serie (JTAG) y la realizacin de mediciones automticas de parmetros del diseo digital implementado en la FPGA. Los sistemas comerciales empleados actualmente para el desarrollo de prototipos basados en FPGA se pueden encuadrar en dos tipos principales: sistemas didcticos y sistemas de gran tamao. En la figura 1 se observa la arquitectura general de estos sistemas [1]. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a pistas o pistas entre si. En realidad, lo que se programa en una FPGA son los conmutadores que sirven para realizar las conexiones entre los diferentes bloques, ms la configuracin de los bloques. Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCAWladimir Ortiz Fernndez WOF-

25 -

Escuela Politcnica Nacional

Sistemas Digitales

Fig. 1. Arquitectura de placas prototipo de desarrollo basadas en FPGA Los primeros sistemas se emplean principalmente para el desarrollo de pequeos circuitos digitales con el fin de evaluar su funcionamiento de una forma sencilla, principalmente aplicados a la enseanza. Estos sistemas se caracterizan por no disponer de memoria SRAM o tenerla de pequeo tamao y de realizar la programacin a travs del sistema Host [2], as como de disponer de una FPGA de baja densidad. Adems, los sistemas pequeos no disponen de interfaces completos de testeo (JTAG), o carecen de dispositivos perifricos de adquisicin de seal. La programacin de estos sistemas se realiza a travs de un computador Host, por lo que su uso autnomo en la mayora de los casos es limitado. Por el contrario, los sistemas empleados en investigacin disponen de gran cantidad de recursos de memoria y en la mayora de los casos de dos o ms FPGAs de gran densidad [3]. Por otro lado y desde un punto de vista prctico, una vez realizada la implementacin de un circuito en una FPGA se hace necesario la medicin de ciertos parmetros importantes que nos ofrecen valores de mrito de nuestro diseo. Entre estos parmetros se encuentran la latencia del circuito (ns), el throughput (MB/s), el consumo (W) y el ruido generado(A). En cualquier caso, la medida de ciertos parmetros de mrito del diseo se ve dificultada por la imposibilidad de variar la frecuencia de la seal de reloj, o por la inexistencia de puntos de medida de consumo de potencia o de seales de alta velocidad [4]. Los experimentos prcticos llevados a cabo han conducido a la conclusin de que las placas actuales no disponen de tomas de conexin para terminales de prueba adecuados, introducindose gran cantidad de ruido de modo comn en las mediciones. Esto es debido a que el ruido de conmutacin de alta frecuencia generado en el sistema se introduce en el circuito de medida a travs de las conexiones y puntos de prueba, al presentar estas conexiones un circuito resonante cuya influencia ser mayor cuando la frecuencia de los picos sea cada vez ms prxima a la alta frecuencia de resonancia. Para evitar este problema, en el prototipo se ha dispuesto de dos planos de masa junto con conexiones de baja inductancia parsita para poder realizar, entre otras, mediciones del ruido generado. Estos problemas nos han llevado a plantear una serie de objetivos que nos lleven a realizar una placa de prototipo que se ajuste a nuestras necesidades. Estos objetivos son: poder implementar algoritmos realizados tradicionalmente con DSP, el empleo de interfaces de testeo serie (JTAG) y la realizacin de mediciones automticas de parmetros del diseo digital implementado en la FPGA [5]. Tradicionalmente las FPGAs han sido orientadas al campo sncrono. Los circuitos asncronos estn aumentando en inters por las potenciales ventajas de las que gozan frente a los sncronos. EsteWladimir Ortiz Fernndez WOF-

26 -

Escuela Politcnica Nacional

Sistemas Digitales