EE03602C

-

Upload

denzelflag -

Category

Documents

-

view

9 -

download

0

description

Transcript of EE03602C

-

Captulo 2Tecnologa de circuitos integrados

2.1 Introduccin

Si bien el origen de la tecnologa de circuitos de estado slido podra remontarse al ao 1875, cuandose observ que el selenio mostraba efectos rectificadores y fotoconductores, el hito clave reconocidocomo origen de esta tecnologa es la construccin por parte de J. Bardeen y W. Brattain, de Bell Tele-phone Labs, del primer dispositivo con ganancia de estado slido, el transistor bipolar [1]. Este dispo-sitivo, basado en materiales semiconductores, signific el punto de partida de la actual tecnologaelectrnica. Fue W. Schokley [2] quien en 1951 aplic el modelo del comportamiento elctrico de launin de dos materiales semiconductores extrnsecos con diferente dopaje, la unin pn, al transistor deunin (bipolar junction transistor, BJT).

Tras 50 aos de evolucin de la tecnologa, el elemento base de la actual tecnologa electrnicaes el circuito integrado, cristal nico de material semiconductor (usualmente silicio) en el que se hanimplementado un nmero muy elevado de dispositivos transistores, generalmente de tipo unipolarconocidos como transistores MOS. Los transistores MOS tienen un fundamento fsico diferente a losBJT; son dispositivos de efecto de campo (FET) basados en el cambio de comportamiento de la capade la superficie del semiconductor en una estructura Metal-xido-Semiconductor. Aparte de la preli-minar patente de Lilienfeld [3], los primeros trabajos sobre el comportamiento de esta simple estructu-ra son debidos, de nuevo, a W. Schockley [4], si bien el primer dispositivo transistor MOS fue fabri-cado en 1960 por Kahng y Atalla [5],[6]. En el prximo apartado se procede a presentar la estructura yel comportamiento elctrico de los dispositivos MOS.

La tecnologa de circuitos integrados tiene su origen en 1959, tras los trabajos de Jack Kilby [7]de Texas Instruments y Robert Noyce [8] de Fairchild Semiconductors. En agosto de 1959 FairchildSemiconductors hace pblica la tecnologa de fabricacin de transistores en un proceso planar y en

-

38

Diseo de circuitos y sistemas integrados

marzo de 1960 Texas Instruments anuncia el primer circuito integrado comercial, un multivibradorbasado en dispositivos semiconductores BJT de silicio.

Como se ha visto en el captulo anterior la tecnologa electrnica se caracteriza por su gran va-riedad de aplicaciones y su vertiginosa evolucin. Esta evolucin se traduce en la prctica en la mejo-ra de las prestaciones de los circuitos integrados microelectrnicos, gracias, sobre todo, a la reduccinde las dimensiones fsicas de los dispositivos -los transistores y de las interconexiones que los co-nectan entre s para formar los circuitos electrnicos. En tecnologas CMOS el parmetro que se tomacomo referencia es la longitud mnima del canal que es posible fabricar con una determinada genera-cin tecnolgica ().

En este captulo se presentan modelos bsicos que permiten analizar cmo repercute en lasprestaciones de los circuitos microelectrnicos CMOS la modificacin de los parmetros fsicos yelctricos que la evolucin tecnolgica impone a los dispositivos y las interconexiones. Tambin secomentarn nuevos modelos, as como los nuevos fenmenos que aparecen o se hacen ms palpablesen tecnologas submicrnicas. Tambin se presentan en este captulo los fundamentos de fabricacinde los circuitos integrados actuales. Finalmente, se analizan son las previsiones para la evolucintecnolgica en el futuro y sus repercusiones en el funcionamiento y las prestaciones previstas de loscircuitos microelectrnicos.

2.2 Fundamentos de los dispos itivos MOS

2.2.1 Estructura bsica: Condensador MOS

La Fig. 2.1 muestra la estructura bsica MOS. Se trata de una estructura tipo condensador tpica endonde uno de los electrodos es un material semiconductor, en el caso de la figura un semiconductortipo p con una concentracin de impurezas Na y una constante dielctrica Si. El otro electrodo es me-tlico (usualmente aluminio, Al).

El material dielctrico (xido de silicio SiO2, aislante) tiene un espesor tox y una contante dielc-trica ox. Si consideramos la estructura sin pola-rizar y a una temperatura estable T (suficiente-mente alta como para asegurar la ionizacin detodos los tomos de las impurezas) y no consi-deramos ningn tipo de carga atrapada en eldielctrico o las superficies, tendremos que ladensidad de portadores mayoritarios p y mino-ritarios n es la misma en todo el volumen delsemiconductor y vienen dadas por:

p N n nNai

a

= =

2 (2.1)

siendo ni la densidad intrnseca de portadores.El valor de la capacidad que podemos esperarentre los terminales G (gate, puerta) y B (bulk,body, cuerpo o substrato), Cg puede ser calcula-

metal

xido (SiO2)

semiconductor

GVG

BVB=0

tipo p (Na)Si

toxox

x

xdE(x)

Fig. 2.1 Estructura bsica Metal-xido-Semiconductor

-

39

Tecnologa de circuitos integrados

da considerando la expresin de la capacidad de dos placas paralelas semiinfinitas:

C C A C W Lg ox ox= = con C toxox

ox

=

(2.2)

en donde Cox es la capacidad por unidad de rea, A es el rea, W la anchura y L la longitud del conden-sador MOS.

Procedamos ahora a polarizar la estructura. Consideramos que el substrato B se encuentra a unatensin VB = 0 y el electrodo de puerta G se polariza a una tensin moderada positiva VG. En el casode un condensador metal-metal, todo el potencial VG se aplica en el xido y no en las zonas metlicas,lo que provoca la aparicin de un campo elctrico uniforme en la zona del xido de valor

oxGox tVE = . En este caso, metal-metal, la superficie superior del electrodo inferior se encuentra a unpotencial de 0 voltios. En el caso de la estructura MOS que tratamos, no todo el potencial cae a travsde la zona del xido; parte del potencial penetra en el interior del semiconductor, principalmente en laregin superficial superior. Ello provoca la existencia de un campo elctrico interno al cristal quemodificar la distribucin de portadores. Si denominamos S al potencial existente en la superficiesuperior del semiconductor, S=(x=0), (ver Fig. 2.1), en donde es la funcin potencial en el interiordel semiconductor, tendremos:

V VG ox S= + (2.3)en donde Vox es el potencial que cae en la zona del xido. El campo elctrico ES en la superficie (x=0)vendr dado por:

E E x ddxS x

= = = =

( )0 0 (2.4)

y tendr un sentido, como se muestra en la Fig. 2.1, que provocar una repulsin y desaparicin dehuecos (portadores mayoritarios de carga equivalente positiva), ello har que la densidad de mayorita-rios pS en dicha superficie (x=0) sea tal que aS Np

-

40

Diseo de circuitos y sistemas integrados

cimiento de portadores mayoritarios (enhancement). Todos los resultados de este apartado son exten-sibles al hecho de considerar un semiconductor tipo n. En ese caso el potencial VG debera ser negati-vo para provocar el efecto de vaciamiento y positivo para el de enriquecimiento. Por ltimo, si QS esla densidad de carga en la superficie podemos escribir, si contemplamos la estructura como un con-densador de capacidad Cox, una relacin entre Vox y QS:

V QCox

S

ox

= (2.6)

2.2.2 Concepto de inversin de por tadores en una pelcula de la superficie del semiconductor,tensin umbral

Si aumentamos progresivamente el valor de VG, ir aumentando el valor de S, llegando a niveles enlos que no slo desaparecen los portadores mayoritarios, sino que se alcanzar una concentracinsignificativa de minoritarios (electrones). Esta situacin, en la que una fina capa de la superficie delsemiconductor p se comporta como un semiconductor n (electrones como portadores mayoritarios yprctica inexistencia de huecos, minoritarios), se denomina inversin, y a la mencionada capa, capa de

inversin.Si bien el proceso es paulatino y

continuo, se acepta que este mecanis-mo de inversin aparece cuando elpotencial en la superficie del semicon-ductor alcanza el doble del potencialde Fermi, F [9] definido como:

F ai

kTq

Nn

= ln( ) (2.7)

El valor pues del potencial de su-perficie es FS 2 , para el que,

aplicando el conjunto de ecuaciones (7.5), podemos determinar el grosor de la regin de vaciamientoy el valor de la densidad de carga en la regin, QB:

xqNdSi F

a

=

2 2 ( ) y Q q NB Si a F= 2 2 ( ) (2.8)

Aceptada, en estas circunstancias, la aparicin de una capa de inversin, debemos considerar quocurre cuando aumentamos an ms el valor de VG. Para valor superiores que el que provoca la capade inversin, el aumento de potencial se encamina de manera exclusiva a fortalecer la capa de inver-sin y no aumenta prcticamente el espesor de la regin de vaciamiento [8]. As, el valor del espesorde la regin de vaciamiento xd indicado en la ecuacin (2.8) es prcticamente el valor mximo depenetracin del efecto de campo en el semiconductor.

Con estas consideraciones podemos establecer el valor de la tensin VG que provoca la aparicinde la capa de inversin, tensin Vto que denominamos tensin umbral (threshold voltage). Relacio-nando las ecuaciones (2.3), (2.6) y (2.8) podemos escribir:

Vq N

CtoSi a F

oxF= +

2 22

( ) (2.9)

SiO2

capa de inversin

regin de vaciamiento

substrato sin densidad de carga

Fig. 2.2 Capas de vaciamiento e inversin en una estructuraMOS polarizada

-

41

Tecnologa de circuitos integrados

En un anlisis de primer orden de circuitos MOS se considera que Vto es la tensin por debajo dela cual no existe capa de inversin y por encima de la cual el exceso (VG-Vto) produce un aumento netode la carga de inversin QI, de manera que:

Q Q QS B I= + (2.10)

con Q C V VI ox G to= ( ) (2.11)En la prctica, el valor de Vto puede quedar afectado por la existencia de cargas atrapadas en el

xido o las interfaces, provocando un tercer sumando en (2.9). En la fabricacin de circuitos integra-dos tambin se acostumbra a implantar cargas en la superficie del semiconductor, ello modifica elvalor de Vto y se utiliza como tcnica para ajustar la tensin umbral de los dispositivos.

Por ltimo vamos a discutir el efecto que tendra una polarizacin del substrato (que hasta ahorahemos considerado conectado a 0 voltios) a un cierto valor VB negativo. Para un MOS polarizado demanera que aparezca capa de inversin, la aparicin de una tensin de polarizacin del substrato VBmodifica la distribucin de cargas y consecuentemente el valor de la tensin umbral. Un anlisis sen-cillo consiste en considerar la carga de inversin como un material n y analizar el efecto de la tensinVB como si se tratara de una unin pn polarizada inversamente [10]. El valor de la nueva tensin um-bral Vt viene dado por:

V V Vt to F B F= + + ( )2 2 (2.12)en donde el factor se denomina coeficiente de polarizacin de substrato (body bias coefficient) yviene dado por

=

2q NC

Si a

ox

.

A la variacin de la tensin umbral debida a la polarizacin del substrato se denomina efecto de pola-rizacin del substrato (body effect) y aparece en circuitos integrados en donde los dispositivos se colo-can apilados en estructuras serie. Dado que este fenmeno no aparece en muchos de los circuitos ana-lizados y que no es significativo en algunos otros, por razones prcticas en este libro, en trminosgenerales, no diferenciaremos entre Vt y Vto, por lo que a partir de ahora pasaremos a denominar a latensin umbral con el smbolo Vt genrico. La tensin umbral Vt es positiva en los transistores NMOSy negativa en los PMOS. El valor depende evidentemente de las caractersticas de cada tecnologa ycomo veremos ms adelante, es una variable que se escala junto a la reduccin de tamao en la evolu-cin tecnolgica. Como valores tpicos podemos considerar 0,7 V para una tecnologa de 0,8 m y0,25 V para una de 0,25 m.

2.2.3 Estructura de un transistor MOS

Un transistor MOS es un dispositivo que permite la amplificacin de seales y la conmutacin deramas de circuito a una gran velocidad. Por ello son la base de los circuitos analgicos y digitalesmodernos. La tecnologa MOS es adems fcilmente integrable, es decir, que pueden implementarsemillones de transistores MOS en un nico cristal de silicio, dando lugar a los circuitos integrados cuyaconstitucin y fabricacin veremos en el apartado 2.3 de ste captulo.

En la Fig. 2.3 (a) se muestra la estructura vertical de un transistor MOS tipo n o NMOS, una es-tructura vertical MOS sobre un substrato p con dos regiones (D y S) implantadas o difundidas n+ a losdos lados de la regin superficial (que ahora denominaremos canal). Los terminales del transistor sonG, puerta o gate, que controla el comportamiento del canal, tal y como hemos visto en los apartadosanteriores, los dos terminales D, drenador o drain y S, surtidor o source y, por ltimo, la polarizacindel substrato B (body, bulk). Generalmente en los circuitos microelectrnicos, y as lo consideraremos

-

42

Diseo de circuitos y sistemas integrados

siempre si no se indica lo contrario, el terminal B est conectado a GND para todos los transistoresNMOS. En la Fig. 2.3 (b) se muestra la composicin correspondiente a un transistor MOS tipo p oPMOS. En este caso el terminal B est usualmente conectado a la tensin positiva VDD. En ambostipos de transistor el electrodo de puerta, por razones de fabricacin, no es metlico, sino que estformado a partir de una deposicin de material polisilicio amorfo. En el comportamiento elctrico noexiste diferencia entre el transistor de puerta metlica y el de puerta de polisilicio.

En la Fig. 2.3 (c) y (d) se muestran las estructuras MOS horizontales, es decir, tal como se vensobre la superficie del circuito integrado. Esta visin tiene importancia por su significado en diseoVLSI, como veremos ms adelante. Por ltimo en (e) y (f) se muestran los smbolos de los respectivosdispositivos que usaremos en los circuitos de este libro (obsrvese que no se muestra el terminal B porconsiderar que est conectado a GND o VDD segn el caso, como se ha dicho anteriormente).

2.2.4 Caracterstica I/V de un transistor MOS

En este apartado vamos a analizar el comportamiento y a desarrollar un modelo analtico aproximadode las caractersticas I/V de los transistores MOS. El modelo presentado, y que se acostumbra a refe-renciar como modelo de Shichmann-Hodges [11], es debido a paulatinos trabajos de Moll [12], Sah[13] y Hofstein y Heiman [14] y es un modelo DC de gran seal.

S DG

L

S DG

Lsubstrato p substrato n

n+ n+ p+ p+

GND VDD

L L

W W

G G

D D SS

D D

G G

SS

a) b)

c) d)

e) f)

Fig. 2.3 Secciones verticales de transistores NMOS y PMOS a) y b) respectivamente.Vistas horizontales c) y d) y smbolos circuitales e) y f) respectivamente

-

43

Tecnologa de circuitos integrados

En primer lugar y bajo un anlisis DC [13], la caracterstica de puerta de estos dispositivos esmuy sencilla. La puerta est aislada del resto de circuito por un aislante (el xido, razn por la cual aveces se ven denominados como transistores de puerta aislada), por lo que se caracteriza por unaresistencia de entrada infinita (con lo que la corriente de entrada por puerta, IG, es siempre nula,

0=GI ). Veremos ms adelante que el modelo ms completo (AC) para el terminal de entrada es el deuna capacidad.

Nos concentraremos aqu en el anlisis de un transistor NMOS, siendo todos los resultados ex-tensibles a PMOS con los correspondientes cambios de signo. En el anlisis consideraremos al termi-nal S, surtidor, conectado a GND (al igual, como hemos indicado anteriormente, que el substrato B).Aplicaremos una tensin al terminal D, drenador, que al estar referida a GND y estar el terminal Sconectado a GND, denominaremos VDS, y pretendemos determinar la caracterstica de ID en funcin deVDS y por supuesto de la tensin de puerta, G (que por las mismas razones que anteriormente denomi-naremos VGS) que, segn hemos deducido anteriormente, podr provocar la aparicin de una regin deinversin y permitir una conduccin entre D y S a travs del canal cuando VGS>Vt. El hecho de quecuando existe conduccin de canal siempre existe una regin de vaciamiento que lo rodea y por ello loasla del substrato hace que la corriente por el terminal D sea la misma que por el terminal S, por elloa la corriente de drenador la denominamos I I IDS D S= =

As pues, partimos de que en todo momento 0=GI , y de que para VGS

-

44

Diseo de circuitos y sistemas integrados

todo y la corriente tiene el mismovalor IDS. Observamos en la figura quela regin de inversin no es uniforme.Esto es debido a que, si bien el poten-cial en el terminal G es constante paratodo y, no lo es la tensin en el canal,que, de hecho, forma un divisor resis-tivo no lineal entre D y S, por lo quepara un y genrico debemos considerarque el canal se encuentra a una tensinV(y), cuyo valor est entre 0 y VDS.Observemos que la situacin mscrtica es en el extremo D, que esdonde la capa de inversin es mnimaal ser la tensin de canal mxima.

Para asegurar la existencia de ca-nal en ese extremo, consideraremosque VDS es moderada, concretamenteVDS

-

45

Tecnologa de circuitos integrados

I C WL

V V V dV C WL

V V V VDS n ox GS to

Vn ox

GS t DS DS

DS

= =

( ) ( ) 12

2 (2.18)

lo que nos indica que el comportamiento de IDS sigue una ley hiperblica en VDS, con una constante de

proporcionalidad que denominamos K, factor de transconductancia, K C WL

n ox=

.

Recordemos que este anlisis es solo vlido para VDSVGS-Vt el transistor se encuentra en esta regin de corriente casi constante, denominada regin desaturacin. La condicin VDS=VGS-Vt se cumple ahora en un punto del canal anterior a D, lo que pue-de ser considerado como una contraccin de la longitud de canal, produciendo un ligero aumento decorriente (prcticamente lineal con VDS).

As pues, el modelo para esta regin de saturacin viene dado por:

I K V V VDS GS t DS= +212( ) (2.21)

en donde es el factor de modulacin de canal que modela el ligero incremento lineal de corrientecon la tensin VDS. Un valor tpico de es 0,01 V-1, en muchos casos consideraremos =0, acercn-donos a un comportamiento ideal del transistor. En los circuitos integrados modernos, como veremosen un prximo apartado, intervienen transistores tanto PMOS como NMOS, dando lugar a la tecnolo-ga CMOS (Complementary MOS).

2.2.5 Parmetros y caractersticas de los dispositivos y las interconexiones en tecnologa CMOS

En este apartado se recopilan los parmetros que caracterizan las tecnologas y circuitos CMOS. LaFig. 2.5 muestra un corte vertical y una vista superior de un transistor MOS. En ella se definen losdistintos parmetros geomtricos con la notacin que se utilizar en el resto del libro. El lector deberecordar que, en una tecnologa planar, los nicos parmetros que el diseador puede definir o modi-ficar son las dimensiones horizontales de los dispositivos (ancho y largo del canal, forma de las difu-siones y de las interconexiones, etc.). El resto de parmetros vienen dados por el proceso de fabrica-cin. Adems, el proceso de fabricacin tambin determina los valores mnimos para las dimensiones

-

46

Diseo de circuitos y sistemas integrados

que el diseador puede utilizar en los dispositivos y las interconexiones, detallados en las denomina-das reglas de diseo.

Junto con los parmetros geomtricos es necesario considerar los parmetros de tipo fsico, co-mo el nivel de impurezas o nivel de dopado del semiconductor utilizado como substrato (Na). Losparmetros elctricos ms importantes son la tensin de alimentacin (VDD) y las tensiones umbralnominales de los transistores NMOS y PMOS (Vtn y Vtp, respectivamente).

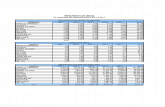

Todos los parmetros anteriores se denominan parmetros primarios porque vienen directa-mente determinados por la estructura de los dispositivos y las interconexiones de los circuitos micro-electrnicos. La Tabla 2.1 resume estos parmetros primarios. Los parmetros elctricos que se deri-van de ellos se denominan parmetros secundarios y entre ellos podemos citar el campo elctrico a lolargo del canal (El) y el que existe verticalmente a travs de los xidos (Ev) o la capacidad de puertaCg.

Adems de los parmetros que afectan a elementos individuales del circuito integrado, hay quetener en cuenta otros parmetros de tipo global, como el nmero de entradas y salidas finales del cir-cuito NE/S, el nmero total de transistores NTRT y el tamao del circuito, que puede medirse conside-rando que es un cuadrado de lado D y por tanto de rea A = D2. De estos parmetros primarios glo-bales se deducen otros parmetros secundarios globales, como el nivel de integracin (nmero detransistores por unidad de superficie) representado por NI.

En cuanto a las interconexiones, esimportante hacer una distincin entre lasque se clasifican como interconexioneslocales -utilizadas, como su propio nombreindica, para conectar elementos cercanosentre s- que vern reducidas sus dimensio-nes de forma proporcional al escalado delos elementos a conectar, e interconexionesglobales -utilizadas para interconectar losbloques de mayor nivel que forman el cir-cuito integrado y distribuir seales por todala superficie del mismo-. Estas ltimas venaumentada su longitud al aumentar la com-plejidad y el rea de los circuitos integra-dos, a pesar de que se escalen los dispositi-vos elementales. Los parmetros

Drenador n +

Interconexiones

Puerta

Surtidor n

+

L

W

Vista superior

Puerta

Surtidor n+

Substrato p,dopado NA

Xj

tox

L

tFox

Interconexiones

Drenador n +

Corte transversal

H

Fig. 2.5 Vistas transversal y superior de un transistor NMOS indicando los principales parmetros geomtricos

Longitud del canal LAnchura del canal WProfundidad de las uniones XjGrosor xido de puerta toxGrosor xido de campo tFoxGrosor interconexiones HNivel de dopado del substrato NATensin de alimentacin VDDTensiones umbral Vtn, Vtprea del circuito integrado A = D2Nmero de transistores NTRTNmero de entradas/salidas NE/S

Tabla 2.1 Parmetros primarios de la una tecnologaCMOS

-

47

Tecnologa de circuitos integrados

secundarios ms relevantes de las interconexiones son su resistencia y su capacidad, lo que permite,en una primera aproximacin, calcular el retardo RC que introducen en la transmisin de las seales.

2.2.6 Modelo analtico del transistor MOS

Las expresiones que hemos visto en el apartado 7.2.4 son el modelo ms elemental que describe elfuncionamiento de un transistor MOS [15]. En (2.22) se muestran las ecuaciones correspondientes aun NMOS. Las ecuaciones para un PMOS son equivalentes, teniendo en cuenta que las tensionespuerta-surtidor, drenador-surtidor y umbral tienen signos contrarios a sus equivalentes en el NMOS.En la Fig. 2.6 se muestran las curvas caractersticas de un transistor MOS. Obsrvense las tres regio-nes de corte, hmica y saturacin. En esta ltima regin se muestran las curvas reales y las correspon-dientes a despreciar el efecto de modulacin del canal (=0). Debido a la presencia del factor

)1( DSV+ en el modelo, al extrapolar las caractersticas de la regin de saturacin se cruzan en elpunto /1=DSV . El modelo analtico de Sah, que utilizaremos en este texto y que ha sido desarro-llado en el apartado 2.2.4 es:

I

V V

K V V V V V V V V V

K V V V V V V

D

GS tn

n DS GS tnDS

GS tn DS GS tn

nGS tn DS GS tn DS

=