Flipflops

-

Upload

walter-carrillo -

Category

Documents

-

view

221 -

download

2

description

Transcript of Flipflops

-

FLIP-FLOPSMultivibradores Biestables

-

Sistema digital generalizadoLas salidas dependen de las entradas para cualquier instante de tiempo.Elementos de Memoria (Se mantiene)

-

Circuito SecuencialExisten dos tipos:Sincrnico: su comportamiento puede definirse a partir del conocimiento de sus seales en instantes discretos de tiempo.Asincrnico: depende del orden en que cambian las seales de entrada

-

Multivibrador BiestableFlip-Flops FFCircuito Lgico con Dos Salidas Q y QQ Salida Normal y Q Salida InvertidaDos Estados Posibles Q=0 y Q=1Q=1 y Q=0El Flip-Flop guarda el estado para variaciones a la entrada (Memoria).

-

Flip-Flop SET CLEAR NANDEntradas SET y CLEAR (PONER - LIMPIAR)Dos estados de Salida Igualmente Probables.

-

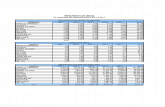

Transicin de Entradas. CLEAR=1SETCLEARQQ

-

Transicin del SET para CLEAR=1SETCLEARLa pulsacin BAJA en SET FF termina en el estado Q=1Estado FIJO Q=1

-

Transicin en CLEARSETCLEARSETCLEARQQAnulacin del FFQ=0 Estado Anulado

-

Resumen FF NANDFFQQSC

SETCLEARSALIDA FF11No hay Cambio01Q=110Q=000Ambiguo

-

Variacin de SET y CLEAR

-

FF Con SET-CLEAR NOR

SETCLEARSALIDA FF00No hay Cambio10Q=101Q=011Ambiguo

-

Transicin de Seales en FF NORQ

-

Seales de un CronometroSistemas digitales Asincrnica Sincrnica

Transicin en sentido positivoTransicin en sentido Negativo

-

FLIP-FLOPS IIFF SC CronometroFF J-K CronometroFF D Cronometro

-

FF S-C Transicin PositivaTransicin Positiva

SC Qn+100Qn(No hay Cambio)10101011Ambiguo

-

FF S-C Transicin NegativaCual es la Seal en Q ?TransicinNegativa

SC Qn+100Qn (No hay Cambio)10101011Ambiguo

-

FF S-C Con NAND Un FF BASICO DE COMPUERTAS NANDUN CIRCUITO CONDUCTOR DE PULSACIONESUN CIRCUITO DETECTOR DE ARISTA.

-

EL BIESTABLE J-K CON CRONOMETROLas entradas de Control J K == S C Transicin en Sentido Positivo.Diferente J=1 y K=1 No generan seal ambigua.Para 1 1 FF Pasa al estado Opuesto.Siempre que efectu Transicin Negativa.MODO ARTICULADO DE OPERACIN.FF J=1 K=1 Qn+1 = Qn

-

Biestable J-K con Cronometro (subida) Suponemos Q=1 InicialTransicin POSITIVATSP

JKQn+100Qn(No hay Cambio10101011Qn' (Se articula)

-

Biestable J-K con Cronometro (bajada) Suponemos Q=1 InicialTransicin Negativa

JKQn+100Qn(No hay Cambio10101011Qn' (Se articula)

-

FF J-K Con transicin Activada J K Q y Q Se retroalimenta

-

BIESTABLE D CON CRONOMETROD es SincrnicaTSPQ == D para TSP

DQn+10011

-

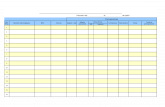

Ejercicio Disear un Circuito de almacenamiento de registros de 8 bits con TSP y TSN Con FF D.

-

UN FF D a partir de un FF S-C

-

Transferencia paralela FF D Circuito Combinatorio

-

Cerrojo DNo posee Circuito detectorCLK 0 D no tiene efectoCLK 1 D 0 SET =0 o CLEAR PARA Q=D.Permite que Q Cambie de estado Si D Cambia en tanto que CLK =1

-

EjercicioDeterminar la forma de onda de un Cerrojo D para las formas de onda de entrada.

-

ENTRADAS ASINCRONICASS,C,J,K y D Entradas de Control.Entradas Sincrnicas.El efecto es sincronizado con la seal del CLK.Se implementan una o mas entradas Asincrnicas.Operan independiente de las Sincrnicas.Se utilizan para FF1 o FF 0 NO importa condiciones.

-

ENTRADAS ASINCRONICAS

DCSETDCCLEARFF11OperacinSincrnica01Q=1 SET10Q=0 CLEAR00No se utilizaAMBI.

-

Convenciones de Fabricantes de Chips

Entrada SET AsincrnicaEntrada CLEAR AsincrnicaDC SETDC CLEARPRESETCLEARSETRESETSd (fijacin directa)Cd (eliminacin Directa)

-

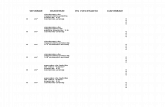

Las entradas Asincrnicas

-

Consideraciones de Distribucin Fabricantes CaracteristicasValores Mnimos de ts y th.Tiempos en nanosegundos.Tiempos de constitucin y de contencin.Demoras de propagacin.Frecuencia mxima de cronometraje

*