LAB4ELC315

-

Upload

victorsagastume -

Category

Documents

-

view

218 -

download

0

Transcript of LAB4ELC315

-

7/25/2019 LAB4ELC315

1/18

UNIVERSIDAD DE EL SALVADORFACULTAD DE INGENIERA Y ARQUITECTURA

ESCUELA DE INGENIERA ELCTRICAELECTRNICA III

LABORATORIO 4: SWITCH ANALGICO, SAMPLE AND HOLD,MULTIPLEXER ANALGICO.

CATEDRTICO: ING. JORGE RAMOS LPEZ.

INSTRUCTORES:

BR. GEORGINA ALEJANDRA RAMOS

BR. ARMANDO JOSE VALLE

ESTUDIANTES

BOLAOS ESQUIVEL, JOCELYN REGINA BE12004

SAGASTUME PEATE, VICTOR SALOMON SP11024

Martes 03 de Noviembre de 2015.

RESUMEN: En el laboratorio: Switch Analgico, Sample and Hold, MultiplexerAnalgico,se pretende analizar las caractersticas y las aplicaciones para cada uno de loscircuitos que en la prctica se realizaron. En el presente laboratorio la primer parte consisteen la implementacin del circuito El timer LM555 el cual proporcionara una salida enVCLK, obteniendo una seal de reloj de 20kHz (+5%) tal como se indica en los resultadosobtenidos. La segunda parte consiste en implementar el circuito Inversor CMOS estecircuito requerir la salida VCLK y su completo Vcomp, la tercer parte de la prctica delaboratorio se trabaj con el circuito Sample and Hold para ello se utiliz un transistorNMOS como switch y se demostr el funcionamiento de este inyectndole la forma de ondade salida del inversor CMOS que a la vez en su entrada tena la seal de reloj producida porel multivibrador, finalmente se implement el circuito Multiplexer Analgico este circuitoayuda a muestrear una seal de entrada. Los resultados obtenidos sern analizados, simulados

en TINA y sern mostrados por imgenes obtenidas en el procedimiento.

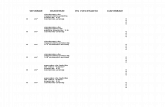

EQUIPO: Lista de materiales y equipo utilizados para la elaboracin y prueba de loscircuitos realizados en la prctica de laboratorio:

-

7/25/2019 LAB4ELC315

2/18

Equipo:

Osciloscopio Agilent DSO1012A ,100 MHz:Generador de seales agilent 33210a 100 MHZ.

Protoboard.

Multitester digital.Materiales:

Timer: LM555.Amp-Op: LM356.MOSFET: I4007.Resistencias de: 1k(2), 1.5k(1), 2.9k(1), 100(1).Capacitores de: 0.01uF (1), 0.1uF (1), 1000pF (1).Potencimetro de 10k

INTRODUCCIN:Cuando un equipo electrnico nos muestra una informacin, puede hacerlo de formaanalgica o de forma digital; una seal analgica es continua, y puede tomar infinitos valores.De diferente manera el concepto de una seal digital nos indica que es discontinua de otramanera se puede decir que va a saltos, pasa de un valor al siguiente sin poder tomar valoresintermedios. Los circuitos que se implementaran en la prctica; un generador de reloj,switches analgicos, sample and hold y finalmente un multiplexor analgico 2.1.En el presente laboratorio se implementaron circuitos para ilustrar los conceptosmencionados, se analiz cada uno de los circuitos en el cual se presentan el procedimiento yresultado obtenidos. No habiendo ms que agregar, se ha preparado el siguiente reporte.

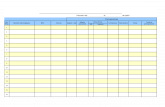

DESARROLLO DE LA PRTICA.

PARTE I:El timer LM555.Descripcin del circuito: En la figura 1 se muestra el LM555 configurado como unmultivibrador estable (generador de reloj). Adems se calcularon los valores requeridos deRA y RB para conseguir una seal de reloj de 20kHz (+5%) con un ciclo de trabajo deaproximadamente el 60%. Se utiliz un condensador C =0.01uF.

-

7/25/2019 LAB4ELC315

3/18

Se realizaron los clculos siguientes:

=

+ Ec. 1

=1

Para un ciclo de trabajo del 60% y sustituyendo los valores en ecuacin 1, obtenemos losiguiente:

0.6 =

120

Sustituyendo en la ecuacin 2, tenemos:

30 =1

20

= 20Sabiendo que:

= ln(2)

Calculamos el valor requerido para RB:

=

ln(2)=

20

0.01 ln(2)= 2.88

Por lo tanto el valor que RA debe tener se calcula de la siguiente manera:

=

2

-

7/25/2019 LAB4ELC315

4/18

0.6 = 3

2(3)

= 1.44

Resultados ObtenidosAl realizar los clculos necesarios para los requerimientos pedidos, los resultados obtenidosfueron los siguientes:

Figura 2. Resultados para VCKL

Simulacin: Teniendo los valores de las resistencias del circuito, construimos el diseo enTINA.

El resultado del circuito multivibrador estable anterior es el siguiente:

-

7/25/2019 LAB4ELC315

5/18

Discusin:Como podemos ver en el resultado, se han marcado con los cursores el inicio y el fin de unperiodo. Esto con la intencin de calcular la frecuencia a la que trabaja el circuito.

Tomando en cuenta que =

; T= periodo

= 10.22- 10.17= 50Por lo tanto:

=1

50

= 20

Para obtener este resultado se tienen que tener en cuenta algunos detalles en cuanto a lasimulacin de este circuito.

Como observamos en el resultado, el tiempo de inicio es de ti=10ms y el tiempo final es detf=10.50ms. Esto se hizo debido a que cuando el circuito comienza su funcionamiento, esteno inicia con las condiciones requeridas. Toma algn tiempo para que el funcionamientodel timer sea el adecuado.

-

7/25/2019 LAB4ELC315

6/18

Como se muestra en la figura 5, en las condiciones inciales de la respuesta del sistema, elresultado de la frecuencia vara segn el tiempo de funcionamiento.

Tambin se tiene que tomar en cuenta que para simular multivibradores astables, en TINAtiene que marcarse la casilla Zero InitialValue.

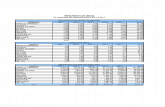

PARTE II: Inversor CMOS.Descripcin del circuito: Del timer LM555 la salida digital VCLKvariar entre tierra y +15V. El multiplexer 2.1 requerir la salida VCLKy su completo Vcomp. La figura 7 muestrael inversor CMOS.

-

7/25/2019 LAB4ELC315

7/18

Resultados Obtenidos: Para generar la seal complemento se utiliz un inversor digitalconstruido en base a dos transistores del arreglo del MOSFET I4007. Los resultadosobtenidos fueron los siguientes:

Figura 8 Resultados Obtenidos para VCOMP

Simulacin:En adicin a la primera etapa, que es el Timer con LM555, se agrega unaetapa inversora.

-

7/25/2019 LAB4ELC315

8/18

Se utiliz un modelo en TINA para los MOSFET del MC14007, que son los que conformanla etapa del inversor CMOS. Presentamos en resultado a continuacin:

Discusin: Se tom la salida del circuito anterior, el timer con el LM555, por lo tanto las

mismas caractersticas del circuito se conservan y se muestran en la salida VCLK. En lasalida Vcomp, vemos el mismo resultado que VCLK, sin embargo el inversor cumple lafuncin que se espera del, la cual es invertir el resultado. Si sobreponemos las sealesresultantes podemos ver claramente como estas dos seales son las opuestas a la otra.

-

7/25/2019 LAB4ELC315

9/18

Al observar las seales, a pesar de que se invierte completamente VCLK, vemos un pequeadiferencia en la parte superior de VCLK. Esto debido a que la etapa inversora se alimentacon +15V, lo cual compensa la seal que viene deteriorada desde VCLK

PARTE III: Sample and Hold.Descripcin del circuito: En la figura 12 se muestra el circuito Sample and Hold, se utilizun de los MOFETS canal N del I4007 como switch analgico para M3 (como se indica enla figura), las resistencias RG3 y RS3 son para proteccin del switch analgico que semanej en nuestro circuito.

Resultados Obtenidos: Se debe mencionar que VGENes una seal seno de 1kHz, de 5Vpico a pico con un offset de +2.5V, adems el voltaje vara de 0 a +5V. Los resultadosobtenidos fueron los siguientes:

-

7/25/2019 LAB4ELC315

10/18

Simulacin:Ahora agregamos una etapa ms a nuestra salida invertida por la etapaanterior.

Ahora veremos el resultado de la nueva etapa como VHOLD, manteniendo siempre VCLK

Y Vcomp. Adems se ver la seal VGEN, que es una seal senoidal con 5Vpp, 1KHz y2.5VDC-offset. VGEN y VHOLDtendrn que oscilar entre 0V y 5V.

-

7/25/2019 LAB4ELC315

11/18

Discusin:En el circuito vemos un transistor MC14007 conectado como switch analgico. Este switchva a ser controlado por la seal de reloj invertida, Vcomp=Vgate, lo cual modificara el voltajede compuerta del transistor, dependiendo de la frecuencia del LM555. El voltaje decompuerta a su vez activa y desactiva el switch que hemos conectado. Este efecto se puedeapreciar brevemente en la figura 15 cuando vemos que la seal VHOLDtiene una seal senoidalde 1KHz, pero tiene pequeos sobresaltos que corresponden a la seal Vcomp, que tiene unafrecuencia de 20KHz. Esos sobresaltos son por efecto del transistor conectado como switch.

El amplificador operacional LM356, est conectado como seguidor de tensin realimentadocon su entrada inversora. Alimentamos la seal senoidal desde la entrada no-inversora. Estaconfiguracin acta como un sujetador de voltaje, el cual mantendr estable el nivel detensin que requerimos a la salida de nuestro circuito, a pesar de los cambios que se realizaranen l.

-

7/25/2019 LAB4ELC315

12/18

Confirmamos as el funcionamiento del sujetador de tensin. Siendo Vcap, la entrada noinversora del amp-op, y VHOLDla salida del circuito.

PARTE IV: Multiplexer analgico.Descripcin del circuito:En la figura 17 se muestra el circuito Mutiplexer analgico, el

resultado que se espera obtener a la salida del multiplexer es una seal del tipo senoidal perocompuesta por una serie de impulsos, los cuales tendrn una altura igual que la seal deentrada.

Resultados obtenidos: Tal como se muestra en las figuras siguientes los resultadosobtenidos son como los esperados para el funcionamiento de nuestro circuito. Los resultadosobtenidos fueron los siguientes:

-

7/25/2019 LAB4ELC315

13/18

Simulacin: Finalmente agregamos una etapa extra a nuestro circuito, quedando el circuitode la siguiente manera:

-

7/25/2019 LAB4ELC315

14/18

La etapa agregada al circuito, es un switch analgico extra. Este estar alimentado porVCLK, el cual es el opuesto a Vcomp. El resultado lo vemos a continuacin

-

7/25/2019 LAB4ELC315

15/18

Discusin:Ahora vemos un switch adicional, de nuevo, implementado a partir de de un MOSFET. Laconfiguracin de l, es igual al switch implementado anteriormente. La principal diferenciaes la alimentacin del switch. El voltaje de compuerta se alimenta con VCLK, y la fuente tieneuna alimentacin DC por medio de un potencimetro.

Esta nueva seal la inyectamos junto con la seal de switch anterior en la entrada no inversoradel amplificador operacional. La seal de ambos switches en la entrada no inversora, juntocon la seal de salida en VHOLDlas aislamos para un mejor anlisis.

Vemos ahora que Vmux es la seal de entrada al sujetador de voltaje. Como en el circuitoanterior podemos ver el efecto que tiene el switch sobre la seal. La diferencia de las seales

es debido a que los switches con alimentacin de reloj opuesta, se encienden y se apagan conuna frecuencia de 20KHz; Sin embargo cada switch al encenderse busca seguir la tensinque alimenta cada switch, al ser opuestas, una seal senoidal se forma en los extremos de lasseales.

Cuando vemos VHOLD, a diferencia de Vmux, solo se muestra la mitad de la seal. Esto sedebe al efecto del amplificador operacional conectado como sujetador de voltaje.

-

7/25/2019 LAB4ELC315

16/18

CONCLUSIONES.

En base al conocimiento adquirido con la investigacin terica y su correspondienteaplicacin prctica, se llegaron a las siguientes conclusiones:

El multivibrador astable tiende a necesitar un tiempo para normalizar sus funciones.En nuestro caso elDutyCycleo Ciclo de Trabajose ve afectado en las condiciones inicialesde funcionamiento del circuito, por lo tanto tambin nuestra frecuencia y periodo se vieronafectados. Para el anlisis es prudente dar un tiempo de estabilizacin al sistema.

Los circuitos Sample and Hold y Multiplexer analgico, son circuitos que capturan el valorde tensin de una seal que vara continuamente en el tiempo, y congela ese nivel de tensinpor un periodo de tiempo determinado. Sabiendo esto podemos concluir que este circuito sepuede implementar para eliminar valores no deseados dentro de las seales que queremostransmitir en el sistema, y as evitar corrupcin en la seal de salida.

Para implementar los tiempos en los que el circuito simple and hold y el multiplexor estarnsujetando la tensin, se utiliz una seal de reloj implementando un LM555.Esta es una manera muy prctica de manipular estos circuitos, debido a que el diseo de lafrecuencia a la que trabaja el reloj es fcilmente ajustable. Tambin el DutyCycle se puedeajustar fcilmente de acuerdo a la necesidad que requieran los circuitos analgicos yamencionados. Esto hace del timer la mejor manera de manipular la frecuencia de muestreo(sample) de los circuitos desarrollados.

BIBLIOGRAFA.

Sedra, Adel y Smith, Kenneth. Circuitos Microelectrnicos, Quinta edicin.McGraw-Hill Interamericana, 2006.

http://recursostic.educacion.es/secundaria/edad/4esotecnologia/quincena5/4q2_contenidos_1a.htm.

http://www.ti.com/lit/ds/symlink/lm555.pdf

http://www.electronics-tutorials.ws/transistor/tran_7.html

-

7/25/2019 LAB4ELC315

17/18

Product

Folder

Sample &Buy

Technical

Documents

Tools &

Software

Support &Community

LM555SNAS548D FEBRUARY 2000 REVISED JANUARY 2015

L M 5 5 5 T im e r

1 Features 3 DescriptionThe LM555 is a highly stable device for generating

1 Direct Replacement for SE555/NE555accurate time delays or oscillation. Additional

Timing from Microseconds through Hoursterminals are provided for triggering or resetting if

Operates in Both Astable and Monostable Modes desired. In the time delay mode of operation, the timeis precisely controlled by one external resistor and Adjustable Duty Cyclecapacitor. For a stable operation as an oscillator, the

Output Can Source or Sink 200 mAfree running frequency and duty cycle are accurately

Output and Supply TTL Compatible controlled with two external resistors and onecapacitor. The circuit may be triggered and reset on Temperature Stability Better than 0.005% per Cfalling waveforms, and the output circuit can source Normally On and Normally Off Outputor sink up to 200 mA or drive TTL circuits.

Available in 8-pin VSSOP Package

Device Information(1)

2 ApplicationsPA RT NUMB ER PA CK AGE B ODY SIZE (NOM)

Precision Timing SOIC (8) 4.90 mm 3.91 mm

Pulse Generation LM555 PDIP (8) 9.81 mm 6.35 mm

VSSOP (8) 3.00 mm 3.00 mm Sequential Timing

Time Delay Generation (1) For all available packages, see the orderable addendum atthe end of the datasheet. Pulse Width Modulation

Pulse Position Modulation

Linear Ramp Generator

Schematic Diagram

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,intellectual property matters and other important disclaimers. PRODUCTION DATA.

ANEXOS

http://www.ti.com/product/lm555?qgpn=lm555http://www.ti.com/product/lm555?qgpn=lm555http://www.ti.com/product/LM555?dcmp=dsproject&hqs=supportcommunityhttp://www.ti.com/product/LM555?dcmp=dsproject&hqs=swdesKithttp://www.ti.com/product/LM555?dcmp=dsproject&hqs=tddoctype2http://www.ti.com/product/LM555?dcmp=dsproject&hqs=sandbuysamplebuyhttp://www.ti.com/product/LM555?dcmp=dsproject&hqs=pf -

7/25/2019 LAB4ELC315

18/18

TLF5943

CD4007MC

D4007CDualComplementaryPairPlusInverter

February 1988

CD4007MCD4007C Dual

Complementary Pair Plus InverterGeneral DescriptionThe CD4007MCD4007C consists of three complementarypairs of N- and P-channel enhancement mode MOS transis-tors suitable for seriesshunt applications All inputs are pro-

tected from static discharge by diode clamps to VDD andVSS

For proper operation the voltages at all pins must be con-

strained to be between VSS b 03V and VDD a 03V at alltimes

FeaturesY Wide supply voltage range 30V to 15VY High noise immunity 045 VCC (typ)

Connection Diagram

Dual-In-Line Package

TLF59431

Top View

NoteAll P-channel substrates are connected to VDDand all N-channel substrates are connected to VSS

Order Number CD4007

C1995 National Semiconductor Corporation RRD-B30M105Printed in U S A