PRACTICA_3_2014_1

-

Upload

silverio-casillas -

Category

Documents

-

view

31 -

download

0

Transcript of PRACTICA_3_2014_1

-

Prctica 3

Introduccin a la tarjeta Spartan 3E Starter y

al ambiente ISE WebPack

Versin 1.0

Clave: 11680

Diseo Digital

LABORATORIO

Profesor

M.C. Diego Armando Trujillo Toledo

Objetivos:

1. Introducir al alumno a un ambiente de diseo para lenguaje descriptor de hardware (VHDL).

2. Identificar la estructura bsica de una descripcin en VHDL (entidad / arquitectura). 3. Elaborar algunos ejemplos de descripciones en VHDL y comprobar, a travs de la

simulacin, su funcionamiento.

4. Introducir al alumno a un sistema de desarrollo basado en un FPGA. 5. Distinguir la organizacin de un sistema de desarrollo basado en FPGA y los elementos

que lo componen.

6. Elaborar algunos ejemplos de descripciones en VHDL, sintetizarlos e implementarlos en la tarjeta de desarrollo

Investigacin Previa:

Debe incluir la bibliografa utilizada. Si no tiene bibliografa, sta no ser revisada y por

consecuencia la prctica tampoco, incluye al menos 2 libros de nivel de ingeniera.

Definicin de VHDL.

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Definicin de entidad y arquitectura, en el contexto de un circuito digital descrito con VHDL. Palabras reservadas utilizadas para definir la entidad y la arquitectura en VHDL.

Diferencia entre seal y puerto de entrada/salida, en el contexto de VHDL.

Diferencia entre los modos IN, OUT, BUFFER e INOUT en VHDL.

Definicin de sntesis, mapeo y enrutamiento, en el contexto del diseo con VHDL.

Definicin de FPGA y CPLD.

Definicin de macrocelda y look-up table (LUT).

Lectura del documento "Organizacin de la tarjeta Spartan 3E".

Lectura de la Gua de Usuario de la tarjeta Spartan 3E.

Revisin del diagrama elctrico de la tarjeta Spartan 3E, seccin "LEDs", "Buttons" y "Switches". Explicacin de la forma de operar de cada "button" y de cada "switch"

(cundo entregan un nivel lgico '1'? cundo entregan un nivel lgico '0'?

Realice una lectura general de la prctica ANTES de realizarla.

Material y Equipo: 1 Computadora con ambiente de desarrollo Xilinx ISE 10.1.

1 Tarjeta de desarrollo para FPGA Spartan 3E Starter (almacn). Verifique que la tarjeta incluye

el cable USB y el cable de alimentacin.

Introduccin:

Los trminos sistema de desarrollo, kit de desarrollo y tarjeta de desarrollo se refieren al mismo hardware que se utilizar para implementar el circuito digital. De la misma

forma, los trminos ambiente de desarrollo, plataforma de desarrollo, software de desarrollo se refieren al programa de cmputo que se utiliza para describir, sintetizar y programar la tarjeta Spartan3E.

VHDL (Very high-speed integrated circuit Hardware Description Language) es un

lenguaje de descripcin de circuitera (hardware) que se desarroll a mediados de la dcada de

1980. A travs de l es posible describir casi cualquier tipo de circuito digital, desde un circuito

combinatorio simple, hasta un microprocesador completo. La ventaja de utilizar VHDL al

construir un sistema digital es que el diseador puede poner ms nfasis en la funcionalidad del

circuito y evitar algunos de los problemas que se presentan cuando el circuito digital se

construye manualmente interconectando circuitos integrados en un protoboard como pueden ser:

equivocacin en las conexiones, falla en la tablilla o falsos contactos debido a los alambres de

conexin. Adems, cuando el circuito digital aumenta en su complejidad y el nmero de circuitos

integrados utilizados para construirlo tambin aumenta, se incrementa la probabilidad de cometer

algn tipo de equivocacin.

Durante la descripcin de un circuito digital o sistema digital con VHDL se hace uso de

una serie de herramientas tanto de software como de hardware que ayudan al proceso de diseo.

Entre las herramientas de software utilizadas se encuentran ambientes o plataformas que

incluyen editores de cdigo VHDL, sintetizadores (que traducen y verifican el cdigo VHDL) y

simuladores. Entre las herramientas de hardware se encuentran los dispositivos programables de

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

alta capacidad (alta densidad), las tarjetas de desarrollo y los sistemas programables completos

en tarjeta.

En lo que se refiere a las herramientas de software, los editores de cdigo VHDL que

incluyen los ambientes o plataformas de diseo actualmente cuentan con varias caractersticas

como resaltado automtico de palabras clave VHDL, sangra automtica de lneas, plantillas

integradas para fragmentos de cdigo VHDL frecuentemente utilizados, entre otras. El

sintetizador (o herramienta de sntesis) que se encuentra incluido en el ambiente o plataforma de

diseo se encarga de analizar la sintaxis, traducir y verificar el cdigo VHDL (o descripcin

VHDL) para que posteriormente el cdigo sea simulado y la descripcin sea programada en un

dispositivo programable de alta densidad. El simulador de la plataforma de diseo permite

definir y aplicar entradas a la descripcin y observar el comportamiento de las salidas, sin tener

que construir el circuito fsico. La simulacin permite observar el comportamiento de las salidas

del sistema tanto funcionalmente (es decir, su comportamiento lgico), como temporalmente

(esto es, que se cumplan los retrasos de tiempo esperados, o que los tiempos de establecimiento,

retencin y otros sean cumplidos).

NOTA:

Cuando se trabaja con VHDL, es comn que se confundan los trminos programa y descripcin. El trmino programa generalmente se utiliza para referirse a un conjunto de instrucciones que realizan una tarea especfica y que son ejecutadas por un microprocesador. El

trmino descripcin debe ser utilizado para referirse a un cdigo VHDL exclusivamente. Un

cdigo VHDL no es propiamente un programa, ya que no es ejecutado por un microprocesador,

sino traducido a una lista de conexiones que ms tarde ser programada en un dispositivo lgico

programable. En lo sucesivo, se utiliza el trmino descripcin, para referirse al cdigo VHDL.

Existen diferentes alternativas para implementar descripciones de circuitos digitales

realizadas con VHDL (o con cualquier otro lenguaje de descripcin). Anteriormente se utilizaban

circuitos integrados programables con encapsulados DIP que se programaban y despus se

interconectaban en un protoboard con elementos tales como resistencias, leds, interruptores, etc.

Actualmente se dispone de tarjetas de desarrollo que contienen varios de estos elementos y otros

ms, para ayudar al usuario en la etapa de implementacin y prueba de su circuito digital.

La ventaja de utilizar una tarjeta de desarrollo es que el usuario tiene ms tiempo para

dedicarlo a la construccin de cdigo VHDL. El tiempo que anteriormente el usuario empleaba

en probar cada compuerta lgica o circuito integrado, interconectarlo en un protoboard, aadirle

resistencias, leds e interruptores, ahora lo puede invertir para describir circuitos digitales de

mediana-alta complejidad. Adems, la probabilidad de que un circuito integrado no funcione

correctamente disminuye, ya que la tarjeta ha sido probada en forma individual al momento de

ser fabricada. Tambin disminuye la probabilidad de realizar una conexin incorrecta, pues

todas y cada una de las conexiones de la tarjeta han sido realizadas desde su fabricacin y

verificadas. Con esto, se espera entonces que se puedan elaborar circuitos con mayor

funcionalidad en menor tiempo.

La mayora de las tarjetas de desarrollo contiene elementos de entrada y de salida, tales

como LEDs e interruptores. Existen algunos modelos que contienen inclusive una pantalla de

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

cristal lquido (LCD), interfaces de comunicacin RS-232, Ethernet, USB, PS/2, osciladores de

reloj e incluso su propia fuente de alimentacin.

La forma en la que un circuito digital debe ser implementado no debe ser a travs de la

prueba y error. Esto significa que ANTES de implementar el circuito en la tarjeta, el usuario

debe haberlo simulado tantas veces sea necesario para asegurar que el funcionamiento del

circuito descrito es como se esperaba. No se considera una buena prctica de diseo la

implementacin del circuito sin haber comprobado su comportamiento a travs de la simulacin.

Por lo tanto, se espera que cada vez que se utilice la tarjeta de desarrollo, el alumno invierta el

tiempo necesario en desarrollar la simulacin.

Todos los fabricantes de tarjetas de desarrollo ofrecen un manual o gua del usuario en el

que se muestra cada una de las conexiones de la tarjeta y la forma de utilizar cada uno de los

elementos que sta incluye. Se espera que en caso de duda, el alumno siempre consulte este

manual de usuario para asegurar el buen uso de la misma.

Esta prctica de laboratorio introduce al uso de la plataforma o ambiente de diseo Xilinx ISE

WebPack y al uso de la herramienta de hardware para implementar circuitos digitales de

mediana alta complejidad y muestra la forma en que se debe interpretar la informacin del manual de usuario de la tarjeta.

Desarrollo:

Como ejemplo, se describir el circuito de la figura 1.

Figura 1

1. Encienda la computadora y localice el cono del ambiente de desarrollo ISE Xilinx 10.1 en el escritorio o bsquelo dentro de la barra de inicio, en el grupo de programas Xilinx

ISE Design Suite 10.1 --> ISE --> Project Navigator.

2. Una vez que Xilinx ISE arranque, el siguiente paso es crear un proyecto. Seleccione dentro de la barra de herramientas File --> New Project, para que aparezca la ventana de

la figura 2.

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Figura 2

3. Dentro del cuadro de texto Project name establezca un nombre para su proyecto. Observe que el proyecto se crear y guardar en la carpeta definida por la ruta que se indica en el

cuadro de texto Project location. Haga click en Next.

4. Asegrese de que en la ventana New Project Wizard Device Properties (figura 3) se encuentren seleccionadas las siguientes opciones. De ser necesario, modifquelas y haga

click en Next.

Family: Spartan3E

Device: XC3S500E

Package: FG320

Speed: -4

Simulator: ISE Simulator (VHDL / Verilog)

Preferred Language: VHDL

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Figura 3

NOTA: Siempre que vaya a trabajar con la tarjeta Spartan3E, ser necesario asegurar que esta

ventana contiene las opciones sealadas en la figura. En caso contrario, es posible que el sistema

digital construido no funcione correctamente.

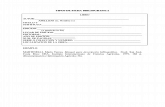

5. En la siguiente ventana New Project Wizard Create New Source (figura 4), haga click en el botn New Source y en la ventana que aparece New Source Wizard Select Source Type elija del lado derecho VHDL Module y dentro del campo File name que aparece del

lado izquierdo, escriba un nombre para el archivo .VHD que contendr su descripcin. El

nombre que indique aqu ser el nombre de la entidad (puede utilizar el mismo nombre

que us para el proyecto o un nombre diferente). En seguida haga click en Next.

Figura 4

6. Dentro de la ventana New Source Wizard Define Module se deben indicar los nombres de las entradas y salidas que contiene la descripcin, as como su direccin (si es entrada

o salida).

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Consulte la figura 5 y escriba en el campo Port Name el nombre de cada entrada o salida

del circuito que se va a describir; en el campo Direction elija la direccin (entrada o

salida) y en el cuadro de texto Architecture name, indique un nombre para la arquitectura.

En seguida haga click en Next y en la ltima ventana de confirmacin New Source

Wizard Summary haga click en Finish.

(Si recibe un mensaje de que el folder donde va a guardar su proyecto no existe, indique

al sistema que debe de crearlo).

Figura 5

7. En las siguientes ventanas que aparecen, simplemente haga click en Finish para terminar con la creacin del proyecto. La plantilla de la derecha que ISE WebPack ha creado el

proyecto es en donde se debe introducir la descripcin en VHDL. Ubique en esa plantilla

la seccin de arquitectura y complete lo que haga falta de la siguiente descripcin (figura

6), que describe al circuito.

entity circuito_combinacional is

port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

Y : out STD_LOGIC);

end circuito_combinacional;

architecture circuito_combinacional _arch of circuito_combinacional is

signal signaltemp1,signaltemp2,signaltemp3: STD_LOGIC;

begin

signaltemp1

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

signaltemp3

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

12. Ya que este es un circuito puramente combinacional, no se requiere una seal de reloj, por lo que en la seccin Clock information de la siguiente ventana que aparece (figura 8),

Initial Timing and Clock Wizard Initialize Timing, , verifique que la opcin Combinatorial (or internal clock) se encuentre seleccionada.

Asegrese tambin que el campo Initial Length of Test Bench contiene 2000 y haga click

en Finish.

Figura 8

13. El nuevo espacio de trabajo que se abre es donde se especificar la forma en que se espera se comporte el circuito. Al hacer click en cada una de las secciones de color

turquesa (cyan), se puede cambiar el nivel lgico que se desea aplicar en cada entrada (A,

B, y C). Observe la figura 9 y configue los valores aplicados en cada entrada como se

muestra (haga click en cada una de las secciones azules para modificar los valores lgicos

presentes en cada entrada).

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Figura 9

14. Grabe el archivo con los estmulos de entrada. Utilice el cuarto botn de izquierda a derecha en la barra de botones.

15. En la ventana Sources elija, dentro de la lista Sources for la opcin Behavioral Simulation y observe que el archivo con sus estmulos de entrada ha sido

automticamente agregado al proyecto. Seleccione el archivo con extensin .TBW y en la

ventana Processes expanda la pestaa Xilinx ISE Simulator para elegir Simulate

Behavioral Model. Haga doble click en esta opcin para simular el comportamiento de su

circuito.

16. Debe aparecer una ventana nueva con los resultados de la simulacin. Observe que el simulador muestra un tiempo menor a 1000 ns. Para cambiar la escala de tiempo, reinicie

la simulacin con el botn , introduzca 2000 ns en el campo

y haga click en el botn de correr simulacin . Debe observar la simulacin

completa (figura 10). Asegrese de verificar que el comportamiento del circuito es el que

se esperaba, revisando en el diagrama del circuito TODOS los diferentes valores que se

aplicaron a la entrada y lo que se obtuvo en la salida.

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

Figura 10

En caso de que se hubiera generado un error, deber repetir los pasos anteriores asegurndose

que haya especificado correctamente los valores de estmulo en cada entrada, e inclusive que

haya introducido correctamente la descripcin.

17. Ahora se proceder a realizar la sntesis de la descripcin para implementarla en la tarjeta. Asegrese que el archivo .VHD se encuentra seleccionado y dentro de la ventana

Sources en el campo de seleccin Sources for elija Implementation. Dentro de la ventana

Processes, haga doble click en Synthesize. Si el proceso se desarroll correctamente, debe

aparecer una palomita de color verde, como muestra la figura 11.

Si se genera algn error durante la sntesis, revise los mensajes que arroja Xilinx ISE y

procure corregir el error antes de continuar. En caso de duda, pregunte al instructor.

Figura 11

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

18. A continuacin procedemos con la etapa de implementacin. Dentro de la ventana Processes, haga doble click en Implement Design. De nuevo, si la implementacin se

desarroll correctamente, debe aparecer una palomita de color verde.

19. Ahora se ligarn las entradas y salidas de la descripcin con los elementos de entrada / salida que contiene la tarjeta. Dentro de la pestaa User Constraints, haga doble click en

Floorplan Area / IO / Logic Post-Synthesis. Si aparece la ventana de la figura 12, haga click en OK para aceptar el mensaje de confirmacin. Este mensaje indica que se va a

crear un archivo con las conexiones de las terminales del FPGA a las entradas / salidas

del circuito.

Figura 12

20. Xilinx ISE abre una aplicacin nueva (llamada PACE) para que el usuario asigne los pines de entrada y salida y los interconecte a los elementos de la tarjeta. Localice la ventana

Design Object List I/O Pins y observar que se enlistan las entradas y salidas de la descripcin. En el campo Loc, se debe introducir el nmero de pin del FPGA que se va a

conectar a dicha entrada salida. Conecte la entrada A al pin H18 (interruptor SW2), la

entrada B al pin L14 (interruptor SW1), la entrada C al pin L13 (interruptor SW0) y la

salida Y al pin F11 (led LD3), como muestra la figura 13.

Cada vez que realiza una asignacin de un pin, debe observar en la ventana Package pins

for xc3s500e-4-fg320, con la pestaa Package View activa, que se ilumina el pin

correspondiente con un crculo de color azul, indicando que ya se ha asignado.

Figura 13

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

21. Con el tercer botn de izquierda a derecha guarde los cambios y cierre la aplicacin PACE para regresar a Xilinx ISE.

22. Dentro de la ventaja Processes, haga doble click en Generate Programming File para generar el archivo que se programar en el FPGA. Al final, debe aparecer tambin la

palomita de color verde, como muestra la figura 14. Es probable que Xilinx ISE actualice

los pasos anteriores (Synthesize y Implement Design) y los vuelva a ejecutar en forma

automtica.

Figura 14

23. Conecte la tarjeta con el cable USB a la computadora y conecte el cable de alimentacin. En caso de que el sistema operativo necesite instalar algn driver, asegrese de que la

instalacin se haga en forma automtica (todos los drivers que la tarjeta requiere estn

incluidos en el sistema operativo). Es probable que aparezcan dos o tres solicitudes de

instalacin de drivers; atindalas todas seleccionado la opcin de instalar el driver en

forma automtica. En caso de duda, pregunte al instructor.

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

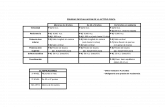

24. Antes de programar el dispositivo, verifique que la tarjeta contiene los jumpers en las posiciones correctas (tabla 1):

Jumper Posicin

JP6 Cerrado

JP7 Cerrado

JP9 Cerrado entre VCCCB0 y 3.3V

J11 Cerrado entre CS0_B y SEL.

Cerrado entre ROM_CS y CS0_B

J30 Cerrado (todos)

Tabla 1

Si alguno de los jumpers no est en la posicin indicada, colquelo correctamente.

25. Como ltimo paso, se encuentra la programacin del dispositivo que se encuentra en la tarjeta. Dentro de la ventana Processes, expanda la pestaa Configure Target Device y

haga doble click en Manage Configuration Project (iMPACT). Xilinx ISE abre una nueva

aplicacin (llamada iMPACT) para programar la tarjeta. En la ventana que aparece revise

que las opciones se encuentren como aparecen en la figura 15. ANTES DE

CONTINUAR, asegrese que la tarjeta se encuentra conectada a su fuente de

alimentacin y que el cable USB se ha conectado a la computadora y a la tarjeta. Haga

click en Finish.

Figura 15

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

26. Observar que aparecen momentneamente dos ventanas de progreso que indican que Xilinx ISE se est conectando con la tarjeta. Si aparece algn mensaje de error, deber

repetir el paso anterior y asegurarse que la tarjeta se encuentra alimentada y conectada.

27. En la siguiente ventana que aparece (Assign New Configuration File) elija el archivo con extensin .BIT que aparezca en su folder de trabajo y haga click en Open. En las

siguientes dos ventanas que aparecen, simplemente haga click en Bypass. (Estas

opciones indican que solamente se va a programar el FPGA, no las memorias que

contiene la tarjeta).

28. En la ventana que aparece, verifique que las opciones indicadas en la figura 16 se encuentran seleccionadas (solamente para Device 1. Los otros dos dispositivos no se

utilizarn por el momento). Haga click en OK.

Figura 16

29. Seleccione el dispositivo marcado como xc3s500e y con el botn derecho, seleccione Program, como muestra la figura 17. Si el dispositivo se program correctamente, debe

aparecer un mensaje azul con la leyenda Program Suceeded.

Figura 17

-

Diseo Digital

FCQI Tijuana M.C. Diego Trujillo / M.C. Jorge Loya

30. Cierre la aplicacin iMPACT y revise el funcionamiento del circuito, manipulando el estado de los interruptores SW2, SW1 y SW0, observando los cambios en LD3.

NOTA: Ya que el FPGA contiene celdas de memoria voltil, la informacin que haya

programado en l nicamente estar disponible mientras la tarjeta se encuentre

energizada. Cuando la tarjeta se desconecta de la alimentacin, el FPGA pierde la

informacin guardada anteriormente y se restaura una aplicacin demostrativa que

contiene una de las memorias de la tarjeta. PARA ENTREGAR

1. Realice la descripcin en VHDL del circuito combinacional del cual le correspondi obtener su tabla de verdad en la prctica anterior, realice la simulacin correspondiente

de todas sus entradas, asigne los pines correspondientes a las entradas y salidas, programe

la tarjeta y compruebe su tabla de verdad con la operacin fsica del circuito.

(Sugerencia: recuerde asignar los pines de entrada a los interruptores slide-switch y las

salidas a alguno de los LEDs). nicamente muestre al instructor el circuito funcionando.

2. Con ayuda de la tarjeta y del manual de usuario, anote los pines del FPGA que se encuentran conectados a cada uno de los siguientes elementos:

a. Interruptores SW3 a SW0. b. LED7 a LED0. c. Interruptores izquierda / derecha / arriba / abajo. d. Interruptor rotatorio. e. Pantalla de cristal lquido.

Conclusiones

Agregar en el reporte los siguientes elementos:

Tomando como referencia el circuito que describi, cul es la diferencia entre una seal y un puerto de entrada / salida?

Cules seran las primeras ventajas que logra identificar mediante el uso de VHDL y un FPGA para disear circuitos digitales combinacionales?

Cules seran las primeras desventajas que logra identificar mediante el uso de VHDL y un FPGA para disear circuitos digitales combinacionales?

Con base en lo que conoce hasta ahora de un FPGA, cules piensa que podran ser las restricciones / limitaciones al momento de utilizar VHDL y un FPGA para implementar

un circuito digital?

De acuerdo con su experiencia de laboratorio, cules podran ser las dificultades para un usuario de estas herramientas (Xilinx ISE y Spartan3E)?