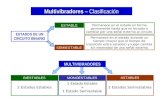

04 - MULTIVIBRADORES

-

Upload

sebastian0527 -

Category

Documents

-

view

103 -

download

1

Transcript of 04 - MULTIVIBRADORES

MULTIVIBRADORES MONOESTABLES

En determinadas aplicaciones, se necesita de un circuito capaz de generar un pulso durante un lapso dado de tiempo y luego retorne a su nivel lgico original.

El monoestable es un circuito que realiza esta funcin al recibir una excitacin exterior. Por lo tanto, tiene un estado estable (de aqu su nombre) y un estado casi estable:

Funcionamiento: Primero la salida est en un estado estable. Despus de aparecer un disparo en su entrada (flanco de subida o de bajada), su salida cambia en un estado inestable temporalmente (tw), para posteriormente regresar al estado estable.

Se disponen de 2 tipos de monoestables: MONOESTABLE NO REDISPARABLE Es aquel que luego de recibir un disparo de entrada, y estando en medio de su salida recibe otro disparo de entrada, lo ignora hasta que acabe su periodo de estado inestable. Luego s estar listo para recibir un nuevo disparo. (DIBUJO PAG 216)

Vemos que: Los que activan al monoestable son: a, b, c y e. lo disparan por un tiempo tp, luego del cual retorna a su estado estable.

Los flancos d y f no tienen ningn efecto sobre la salida, por que este ya se encuentra disparado. El monoestable debe retornar a su estado estable antes de ser reactivado nuevamente.

La duracin del pulso de salida tp siempre va a ser el monoestable comn tp = 0,7 Rt . Ct.

mismo

independientemente de la duracin de los pulsos de entrada. En un

MONOESTABLE REDISPARABLE Se diferencia del anterior en: Puede volver a dispararse mientras se encuentra en su estado inestable, con lo cual dar origen a un nuevo intervalo tp.

Supongamos: Tp= 4ms. a T Q tp tp b c

Con lo anterior podemos ver que: El monoestable se dispara con los pulsos a y b, mientras que con el pulso c tambin lo dispara iniciando un nuevo ciclo de la misma duracin que el primer ciclo.

Al igual que el caso anterior, el tiempo de duracin de tp no depende del ancho del pulso de entrada.

Podemos dispararlo cuantas veces queramos. T Q tp

555 COMO MONOESTABLE Tambin podemos configurar el 555 para que funciones de modo MV monoestable: R Vcc

7 6

8 4 Reset

3

Salida

2 1 C Gnd 5 0,01F

Disparador

Normalmente la salida se encuentra en un estado bajo. Cuando aparece un voltaje en la entrada menor a 1/3 de Vcc (normalmente un corto pulso invertido), la salida pasa a uno. El condensador C empieza a cargarse a travs de R. Cuando alcanza un poco mas de 2/3 de Vcc la salida pasa nuevamente a cero, C ve tierra por la entrada de descarga (pin 7) y se descarga en forma rpida volviendo a las condiciones iniciales.

Tenemos que: T = 1,1 RC Con: T = Segundos. R = Ohms. C = Faradios.

As por ejemplo, los valores R = 3 k duracin aproximada de 3,3 ms.

y C = 1 F produciran un pulso con una

Consideraciones: Si la entrada se mantiene baja, la salida no cae. El Reset normalmente en uno. Si se coloca a tierra, la salida se fija en cero aunque est disparado.

BIESTABLES Los circuitos vistos hasta el momento su salida solo depende de su entrada presente en el momento.

A diferencia de los circuitos combinacionales, estos ciruitos lgicos tienen la capacidad de almacenar estados del mismo mediante arreglo de compuertas lgicas.

La mayoria de sistemas digitales estn constituidos por circuitos combinatorios y elementos de memoria.

El elemento de memoria ms importante es el multivibrador Biestable (MVB), (flipflop, FF, por su nombre en ingls), que est formado por un ensamble de compuertas lgicas. Aunque una compuerta lgica, por s misma, no tiene la capacidad de

almacenamiento, pueden conectarse varias configuraciones de compuerta que se utilizan para producir estos multivibradores. Un FF puede mantener un estado indefinidamente y cambiar al momento de recibir un nuevo estado en su (s) entrada (s).

La Figura muestra el tipo de smbolo general empleado para un flip-flop. El smbolo indica el FF tiene dos salidas, marcadas como Q y Q, que son inversas entre s. En

realidad, se puede utilizar cualquier letra, pero la Q es la de uso ms extendido. La salida Q recibe el nombre de salida normal del FF, mientras que Q es la salida negada o invertida del FF.

Cada vez que se haga referencia al estado de un FF, ste ser el estado de su salida normal Q; se sobreentiende que la salida invertida Q, se encuentra en el estado opuesto. Por ejemplo, si se afirma que el FF se encuentra es estado ALTO (1), significa que Q=1; si se seala que el FF se encuentra en el estado BAJO (0), entonces Q=0. Claro esta que el estado Q siempre es el inverso de Q. Un FF puede tener una o ms entradas. stas se emplean para provocar que el FF haga transiciones hacia atrs y hacia adelante entre sus posibles estados de salida. Como se ver ms adelante, la entrada del FF slo tiene que recibir un pulso momentneo para cambiar el estado de su salida y sta permanecer en el nuevo estado an despus de la desaparicin del pulso de entrada. Esta es la caracterstica de memoria del FF. El flip-flop tambin se conoce con otros nombres, entre ellos registro bsico y multivibrador biestable. El trmino registro bsico se utiliza para ciertos tipos de flipflops que se describen ms adelante. El trmino multivibrador biestable es un nombre ms tcnico para un flip-flop, pero es muy largo para ser utilizado con frecuencia. FF CON COMPUERTAS NAND El FF ms elemental es el llamado registro bsico de compueras NAND o registro bsico.

Bajo condiciones normales, las salidas siempre sern inversas entre s. Las entradas normalmente estn en estado alto. Se puede demostrar que hay dos estados de salida igualmente probables con Establecer=Restablecer=1, donde el estado que realmente existe depender de lo que haya ocurrido anteriormente.

FUNCIONAMIENTO EST=REST=1. Esta condicin es el estado normal y no tiene efecto alguno sobre el estado de salida. Las salidas Q y Q permanecern en el estado en que se encontraban antes de presentarse esta condicin de entrada.

EST = 0, REST = 1. Este estado siempre ocasionar que la salida pase al estado Q=1, donde permanecer an despus de que EST retorne a ALTO. A esto se le denomina inicio del registro bsico.

EST = 1, REST = 0. Esto siempre producir el estado Q=0, donde la salida permanecer an despus de que REST retorne a ALTO. A esto se le llama borrado o reinicio del registro bsico.

EST=REST=0. Esta condicin intenta iniciar y borrar el registro bsico en forma simultnea y puede producir resultados ambiguos. No debe utilizarse.

Obteniendo al final: EST 0 0 1 1 REST 0 1 0 1 SALIDA Invlido Q=1 Q=0 Sin Cambio

Teniendo tambin una representacin alternativa: La cual se empleara de ahora en adelante cuando hablemos de FF con NAND

Donde: S = Entrada ESTABLECER C = Entrada RESTABLECE Y las burbujas significan que sus entradas se activan en bajo.

FF CON COMPUERTAS NOR

Dos compuertas NOR acopladas transversalmente se pueden utilizar como un registro bsico con compuerta NOR. El arreglo que se muestra en la Figura es semejante al registro bsico, excepto que las salidas Q y Q tienen posiciones invertidas. El anlisis de la operacin del registro bsico NOR puede efectuar exactamente de la misma forma que el registro bsico NAND y se resumen como sigue:

EST= REST =0. Esta es la condicin normal del registro bsico NOR y no tiene efecto alguno sobre el estado de salida Q y Q permanecern en cualquier estado en que se encontraran antes de esta condicin de entrada.

EST =1, REST = 0. Esto siempre har Q=1, donde permanecer an despus de que EST retorne a 0.

EST = 0, REST = 1. Esto siempre har Q=0, donde se quedar aun despus de que REST regrese a 0.

EST = 1, REST = 1. Esta condicin intenta iniciar y borrar el registro bsico al mismo tiempo y produce Q=Q=0. Si las entradas se regresan a 0 simultneamente, el estado de salida resultante es impredecible. No se debe usar esta condicin de entrada.

El registro bsico de la compuerta NOR opera exactamente igual que el registro bsico NAND excepto que las entradas EST y REST son activas en ALTO en vez de activas en BAJO y el estado normal en reposo es EST = REST = 0. Q se fijar en ALTO por medio de un pulso ALTO en la entrada EST y se har BAJO por medio de un pulso ALTO en la entrada REST.

Obteniendo al final: EST 0 0 1 1 REST 0 1 0 1 SALIDA Sin Cambio Q=0 Q=1 Invlido

El smbolo de bloque simplificado del registro bsico NOR. Las entradas S y C son activas en ALTO. Las entradas estn sin burbujas, lo que significa que sus entradas se activan en alto.

SEALES DE RELOJ Los sistemas digitales pueden operar en forma sincrnica o asincrnica. En los sistemas asincrnicos las salidas de los circuitos lgicos pueden cambiar de estado en cualquier momento en que una o ms de las entradas cambien. En los sistemas sincrnicos los tiempos exactos en que alguna salida puede cambiar de estados se determinan por medio de una seal, que comnmente se denomina, de reloj. Esta seal de reloj es una serie de pulsaciones rectangulares o cuadradas. La seal del reloj se distribuye a todas las partes del sistema y muchas (o incluso todas) las salidas del sistema pueden cambiar de estado slo cuando el reloj hace una transicin.

Las transiciones (tambin denominadas flancos):

Transicin con pendiente positiva TPP (Cuando el reloj cambia de 0 a 1). Conocido tambin como Flanco de Subida.

Transicin con pendiente negativa TPN (Cuando el reloj cambia de 1 a 0). Conocido tambin como Flanco de Bajada.

FF SINCRONIZADOS POR RELOJ Existen varios tipos de FF sincronizados por reloj. Las principales caractersticas, que son comnmente a todos ellos, son: 1. Los FF sincronizados por reloj, tienen una entrada de reloj que comnmente est marcada como CLK, CK o CP. En muchos FF sincronizados por reloj, la entrada CLK es disparada por flanco, lo que significa que es activada por una transicin de la seal; esto se especifica por la presencia de un pequeo tringulo sobre la entrada CLK.

2. Los FF sincronizados por reloj tambin poseen una o ms entradas de control que pueden tener varios nombres, lo que depende de su operacin. Las entradas de control no tendrn efecto sobre Q hasta que ocurra la transicin activa del reloj. En otras palabras, su efecto esta sincronizado con las seales aplicadas en la entrada CLK. Por esta razn, estas entradas reciben el nombre de entradas sincrnicas de control. 3. En resumen, puede afirmarse que las entradas de control hacen que las salidas del FF estn listas para cambiar, mientras que la transicin activa en la entrada CLK es la que dispara el cambio. TIPOS DE ACTIVACION

FF SC SINCRONIZADO POR RELOJ

S 0 CLK 0 1 1

C 0 1 0 1

CLK

Q Qo 0 1 Ambiguo

Las entradas S y C controlan el estado del FF, pero este no responde a estas entradas sino hasta que la incidencia del flanco de subida del reloj. Cabe sealar que Qo seala el nivel anterior de Q. Nomenclatura muy empleada por los fabricantes de CI. Ejemplos: Flanco de Subida

Flanco de Bajada

FF JK SINCRONIZADOS POR RELOJ El flip-flop JK es tambin llamado "flip-flop universal" debido a que con l, se pueden implementar otros tipos de flip-flop, como el FF tipo "D" o el FF tipo "T".

Trabaja de la misma forma que los SC o S-R excepto por que la condicin J=K=1 no genera una salida ambigua. Para este estado la salida siempre pasara a su estado opuesto. J 0 0 1 1 K 0 1 0 1 Qo CLK Q Qo 0 1

Este flip-flop es mucho ms verstil que el S-C puesto que no tiene estados ambiguos. La condicin J=K=1, la cual genera la operacin de complemento, se usa ampliamente en todos los tipos de contadores binarios. En esencia, el flip-flop J-K puede hacer cualquier cosa que el flip-flop S-C puede hacer, adems de operar en el modo de complemento. Veamos un ejemplo de este tipo de FF:

Circuitera interna del FF J-K

Su circuitera es la misma de un S-C disparado por flanco. Su diferencia est en una realimentacin desde las salidas Q y Q hacia el conductor de pulsos. FF TIPO D SINCORNIZADO POR RELOJ A diferencia de los flip-flops S-C y J-K, el tipo D slo tiene una entrada sncrona de control, D (letra que proviene de dato) y su entrada de reloj. La operacin del flip-flop D es muy sencilla: Q va hacia el mismo estado en que se encuentra la entrada D cuando ocurre un flanco en CLK. En otras palabras, el nivel presente en D ser almacenado en el flip-flop en el momento en que se presente un flanco.

D 0 1

CLK

Q 0 1

Funcionamiento: La salida Q va hacia el mismo estado de D cuando detecta un flanco en la entrada de reloj. El estado de D es almacenado en el FF cuando se detecta el flanco. Un FF tipo D con flanco de bajada funciona de la misma manera.

Ej.:

Implementacin de un FF Tipo D Vamos a ver que la implementacin de este tipo de FF es muy sencilla.

DCLK

O tambin a partir de un FF J-K:

DCLK

J

K

REGISTRO BASICO D Este es un FF tipo D el cual no es activado por reloj detector de flancos.

Veamos si smbolo y su tabla: END 0 1END

D X 0 1

Q Qo 0 1

1

END

FF TIPO T Es aquel en el que la nica entrada es la del disparador (reloj), y ste se obtiene en base a un FF J-K, llevando las entradas J y K permanentemente al nivel 1. Cuando se pulsa la entrada T, el FF cambia de estado.

T

T Q

ENTRADAS ASINCRONAS En flip-flops sincronizados por reloj se han estudiado las entradas J, K, D y T, las cuales se han sealado como entradas de control. A estas entradas se les denomina tambin entradas sincrnicas porque su efecto sobre la salida del FF se sincroniza con la entrada CLK. Como se ha observado, las entradas sincrnicas de control deben utilizarse junto con una seal de reloj para activar al FF.

Muchos FF con reloj tambin tienen una o ms entradas asincrnicas que operan independientemente de las entradas sincrnicas y de la entrada del reloj. Estas entradas asincrnicas se pueden emplear para fijar el FF en el estado 1 o en el 0 en cualquier instante, sin importar las condiciones presentes en las otras entradas. Las

entradas asincrnicas son entradas dominantes que pueden servir para ignorar todas las entradas a fin de colocar el FF en un estado o en el otro.

Si bien es cierto, estas entradas permiten tener al FF en estado 1 0 por un tiempo indefinido (estas entradas responden a niveles permanentes de corriente contnua) normalmente se usan para iniciar o limpiar el estado de un FF por lo que usualmente se les conoce como PRE (preset) y CLR (clear) respectivamente.

Funcionamiento: PRE=CLR=1: Las entradas asincrnicas son inactivas y el FF est libre para responder a las entradas J, K y CLK; en otras palabras, la operacin sincronizada por reloj puede llevarse a cabo.

PRE=0, CLR=1: PRE est activado y Q va inmediatamente a 1 sin importar que condiciones estn presentes en las entradas J, K y CLK. La entrada CLK no puede afectar al FF mientras PRE=0.

PRE=1,

CLR=0:

CLR

es

activado

y

Q

va

inmediatamente

a

0

independientemente de las condiciones presentes en las entradas J, K o CLK. La entrada CLK no tiene efecto mientras CLR=0.

PRE=CLR=0: Esta condicin no debe utilizarse, ya que puede producir una salida ambigua.

FF MAESTRO ESCLAVO Corresponde a dos FF JK dispuestos en serie. Un circuito sirve como un maestro y el otro como un esclavo. Reciben esta denominacin por que el estado del FF esclavo una vez que el reloj de ste as lo permite - corresponde al estado de las salidas del FF maestro. Este circuito consta adems de lo ya mencionado con un inversor. Tales se disparan con pulsos negativos de modo que el borde negativo del pulso afecte al maestro y el borde positivo afecte al esclavo y las terminales de salida.

APLICACIONES

Sincronizacin Consideremos la siguiente situacin:

La aparicin de pulsos parciales (asincrnicos) se corrige con la inclusin de un FF:

Deteccin de secuencias de Entrada En muchas situaciones una salida se activar slo cuando las entradas son activadas en cierta secuencia.

Supongamos que se desea generar una salida alta slo si la entrada A se activa antes que la entrada B:

Almacenamiento y transferencia de datos Corresponde al paso de informacin de un FF a otro y puede ocurrir en forma sncrona o asncrona.

Transferencia de Datos (serie y paralelo) Paralelo

Serie

Divisin y conteo de frecuencia Corresponde al arreglo de n FF que permiten dividir la frecuencia del reloj inicial en 2n veces.

Si La frecuencia de pulsos del reloj inicial es f, entonces la frecuencia de los pulsos de salida del flip-flop i ser f/2i.

El mismo arreglo de la figura anterior puede usarse como un contador binario, en el que cada Xi corresponde al nmero binario correspondiente a 2i (base polinomio 10).