39564c.en.es

-

Upload

lorens-collo -

Category

Documents

-

view

80 -

download

3

Transcript of 39564c.en.es

2006 Microchip Technology Inc. DS39564C

PIC18FXX2

Hoja de datos

High-Performance, flash mejorado

Microcontroladores de 10 bits A / D

DS39564C-page ii 2006 Microchip Technology Inc.

Noe los siguientes detalles de la función de protección de código en los dispositivos de Microchip:

• Los productos de Microchip cumplir con las especificaciones contenidas en su particular hoja de datos de Microchip.

• Microchip cree que su familia de productos es una de las familias más seguro de su clase en el mercado hoy en día, cuando

se utilizan de la manera prevista y en condiciones normales.

• There son métodos deshonestos y posiblemente ilegales utilizados para violar la función de protección de código. Todos estos

métodos, a nuestro conocimiento, requieren el uso de productos de Microchip de una manera fuera de las especificaciones de

funcionamiento contenidas en hojas de datos de Microchip. Muy probablemente, la persona que lo está involucrado en el robo

de la propiedad intelectual.

• Microchip está dispuesto a trabajar con el cliente que está preocupado por la integridad de su código.

• Neither Microchip ni ningún otro fabricante de semiconductores puede garantizar la seguridad de su código. Código de

confirmación no significa que estamos garantizando el producto como "irrompible".

Bacalaoprotección de correo está en constante evolución. Nosotros en Microchip están comprometidos a mejorar continuamente las

funciones de protección de código de nuestros productos. Los intentos de romper característica de Microchip código de protección

puede ser una violación de la Digital Millennium Copyright Act. Si tales actos permitir el acceso no autorizado a su software o en el

trabajo con derechos, usted puede tener el derecho a pedir la reparación conforme a esa ley.

Información contenida en esta publicación con respecto a las

aplicaciones de dispositivos y similares se proporciona

únicamente para su comodidad y pueden ser reemplazadas

por las actualizaciones. Es su responsabilidad asegurarse de

que su solicitud cumple con sus especificaciones.

MICROCHIP NO HACE NINGUNA REPRESENTACIÓN O

GARANTÍA DE NINGÚN TIPO, YA SEA EXPRESA O

IMPLICADA, escrita u oral, LEGAL O DE OTRO TIPO,

RELACIONADA CON LA INFORMACIÓN, INCLUYENDO

PERO NO LIMITADO A SU CONDICIÓN, CALIDAD,

RENDIMIENTO, COMERCIALIZACIÓN O IDONEIDAD

PARA UN PROPÓSITO.Microchip se exime de toda

responsabilidad que surja de esta información y su uso. El

uso de dispositivos Microchip en la vida de apoyo y / o

aplicaciones de seguridad es bajo riesgo del comprador, y el

comprador se compromete a defender, indemnizar y

mantener indemne a Microchip de cualquier daño,

reclamaciones, demandas o gastos resultantes de dicho uso.

No hay licencias se transmiten, de manera implícita o de otro

modo, bajo ningún derecho de propiedad intelectual

Microchip.

Marcas comerciales

The nombre y el logotipo de Microchip, el logotipo de

Microchip, Accuron, dsPIC, KEELOQ, microIdentificación,

MPLAB, PIC, PICmicro, PICSTART, MATE PRO,

PowerSmart, rfPIC y SmartShunt son marcas registradas de

Microchip Technology Incorporated en EE.UU. y otros

países.

AmpLab, FilterLab, Memory migrables, MXDEV, MXLAB,

SEEVAL, SmartSensor y la compañía de control Embedded

Solutions son marcas registradas de Microchip Technology

Incorporated en los EE.UU.

Analog-para-el-DigitalEdad, Solicitud Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, ECAN,

ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,

En circuit Programación Serial, ICSP, ICEPIC, termistor

activo lineal, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit,

PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal,

PowerInfo, PowerMate, Powertool, ICE REAL, rfLAB,

rfPICDEM, Select Modo de serie Smart, SmartTel,

Resistencia Total, UNI / O, WiperLock y ZENA son marcas

registradas de Microchip Technology Incorporated en

EE.UU. y otros países.

SQTP es una marca de servicio de Microchip Technology

Incorporated en los EE.UU.

All marcas comerciales mencionadas en este documento

son propiedad de sus respectivas compañías.

© 2006, Microchip Technology Incorporated, Impreso en los

U.S.A., Todos los derechos

reservados. Printed en

papel reciclado.

Microchip recibido ISO/TS-16949: 2002 la certificación de su sede mundial de diseño, y las instalaciones de fabricación de obleas en Chandler y Tempe, Arizona, Gresham, Oregon y Mountain View, California. Procesos de la empresa de sistemas de calidad y

2006 Microchip Technology Inc. DS39564C

procedimientos para su PIC ® de 8-bit MCUs, KEELOQ ® dispositivos de código de salto, EEPROM serie, microperipherals, memoria no volátil y productos análogos. Además, el sistema de Microchip de calidad para el diseño y fabricación de sistemas de desarrollo de la norma ISO 9001:2000.

2006 Microchip Technology Inc. DS39564C páginas 1

PIC18FXX2

28/40-pin Alto Rendimiento mejorado de microcontroladores flash con 10-bit A / D

High Rendimiento RISC CPU:

• C compilador optimizado arquitectura / conjunto de instrucciones

- El código fuente compatible con el PIC16 y

PIC17 conjuntos de instrucciones

• Memoria de programa lineal frente a 32 Kbytes • Memoria de datos Direccionamiento lineal de 1,5 Kbytes

Dispositivo

El Chi-p Programa

Memoria

En-Chip

RAM

(bytes)

Datuna

EEPROM

(bytes) FLASH

(Bytes) Palabra # Single

Instruccións PIC18F242 16K 8192 768 256 PIC18F252 32K 16384 1536 256 PIC18F442 16K 8192 768 256

PIC18F452 32K 16384 1536 256

• Hasta 10 MIPS operación:

- DC - 40. Osc MHz / reloj de entrada

- 4 MHz - 10. Osc MHz / entrada de reloj con PLL activo

• instrucciones de 16 bits de ancho, 8-bit de datos amplia trayectoria

• Los niveles de prioridad de las interrupciones

• 8 x 8 Multiplicador Hardware Single Cycle

PorCaracterísticas ipheral:

• Alta corriente de drenador / surtidor 25 mA/25 mA

• Tres pins interrupción externa

• Timer0 módulo: 8-bit/16-bit temporizador / contador con

8Bits prescaler programable

• módulo Timer1: 16-bit del temporizador / contador

• Timer2 módulo: 8-bit del temporizador /

contador con registro de tiempo de 8-bits

(base de tiempo para PWM)

• timer3 módulo: 16-bit del temporizador / contador

• Oscilador Secundario opción de reloj - Timer1/Timer3

• Dos Capture / Compare / PWM (CCP)

módulos. CCP pines que pueden

configurarse como:

- Captura de entrada: captura es

de 16-bit, max. resolución 6,25

ns (TCY/16)

- Comparar es de 16-bit, max. resolución de 100 ns (TCY)

- Salida PWM: PWM resolución es 1 - a 10-bit,

max. PWM freq. @: 8-bits de resolución = 156

kHz

10-biResolución t = 39 kHz

• Master Serial Port (MSSP) Módulo Síncrono, dos

modos de funcionamiento:

- 3-hilos SPI ™ (compatible con todos los 4 modos SPI) - Master ™ y I2C modo esclavo

DS39564C-page2 2006 Microchip Technology Inc.

PorCaracterísticas ipheral (continuación):

• Direccionable módulo USART:

- Compatible con RS-485 y RS-232-

• Puerto Paralelo Esclavo (PSP) módulo

UnAlog Características:

• Compatible 10-bit de analógico a digital del

módulo (A / D) con:

- Tasa de Muestreo rápido

- Conversión disponible durante el sueño

- Linealidad ≤ 1 LSB

• Detección Programable de Baja Tensión (PLVD)

- Soporta interrupción en-Bajo Detección de voltaje

• Programable Brown-out Reset (BOR)

SpeCaracterísticas sociales: Microcontroladores

• 100.000 escritura / borrado ciclo Enhanced FLASH

de programam típico memoria

• 1.000.000 de borrado / escritura de datos EEPROM ciclo

memorándumry

• FLASH / EEPROM de datos de retención:> 40 años

• Auto-reprogramable bajo control de software

• Power-on Reset (POR), Power-up Timer (PWRT)

und Oscilador Start-up Timer (OST)

• Watchdog Timer (WDT) con su propio on-chip

oscilador RC para un funcionamiento fiable

• Protección contra código programable

• Ahorro de energía modo SLEEP

• Opciones seleccionables del oscilador incluyendo:

- Fase 4X bucle de bloqueo (de oscilador primario)

- Oscilador Secundario (32 kHz) reloj de entrada

• Alimentación 5V Single In-Circuit Serial

Programming ™ (ICSP ™) a través de dos

pines

• In-Circuit Debug (ICD) a través de dos pines

CMOS Technology:

• Bajo consumo, alta velocidad FLASH / EEPROM

tecnología

• Diseño totalmente estático

• Amplio rango de voltaje (2.0V a 5.5V)

• Industrial y extendido rangos de temperatura

• Bajo consumo de energía:

- <1,6 mA típico @ 5V, 4 MHz

- 25 μ Una típica 3V @ 32 kHz

- <0,2 μ Una corriente de espera típico

2006 Microchip Technology Inc. DS39564C páginas 3

PIC18FXX2

28

27

26

25

24

23

22

21

20

19

18

NC

R

C6/T

X/C

K

RC

5/S

DO

R

C4/S

DI/S

DA

R

D3/P

SP

3

RD

2/P

SP

2

RD

1/P

SP

1

RD

0/P

SP

0

RC

3/S

CK

/SC

L

RC

2/C

CP

1

RC

1/T

1O

SI/C

CP

2 *

22

2

1

20

19

18

17

16

1

5

14

13

1

2

RA

3/A

N3/V

RE

F

+

RA

2/A

N2/V

RE

F

- RA

1/A

N1

RA

0/ A

N0

MC

LR

/

VP

P

RB

7/P

GD

RB

6/P

GC

R

B5/P

GM

RB

4

NC

N

C

44

43

42

41

40

39

38

37

36

35

34

RC

6/T

X/C

K

RC

5/S

DO

RC

4/S

DI/S

DA

RD

3/P

SP

3

RD

2/P

SP

2

RD

1/P

SP

1

RD

0/P

SP

0

RC

3/S

CK

/SC

L

RC

2/C

CP

1

RC

1/T

1O

SI/

CC

P2

*

NC

6

5

4

3

2

1

44

4

3

42

4

1

40

RA

3/

AN

3/V

RE

F

+

RA

2/A

N2/V

RE

F-

RA

1/A

N1

R

A0/ A

N0

M

CLR

/

VP

P N

C

RB

7/P

GD

R

B6/P

GC

R

B5/P

GM

R

B4

NC

Diagramas de pines

PLCC

RA4/ T0CKI

RA5/AN4/SS/LVDIN RE0/RD/AN5

RE1/ W R/AN6 RE2/CS/AN7

VDD

VSS

OSC1/CLKI OSC2/CLKO/RA6

RC0/T1OSO/T1CKI NC

7 8 9 10PIC18F442 11 12PIC18F452 13 14 15 16 17

39 38 37 36 35 34 33 32 31 30 29

RB3/ CCP2 * RB2/ INT2 RB1/ INT1 RB0/ INT0 VDD

VSS

RD7/PSP7 RD6/PSP6 RD5/PSP5 RD4/PSP4 RC7/RX/DT

TQFP

RC7/RX/DT RD4/PSP4 RD5/PSP5 RD6/PSP6 RD7/PSP7

VSS

VDD

RB0/INT0 RB1/INT1 RB2/INT2

RB3/CCP2 *

1 33

2 32

3 31 4 30

5PIC18F442 29

6 28

7PIC18F452 27 8 26 9 25

1024 11 23

NC RC0/T1OSO/T1CKI OSC2/CLKO/RA6 VSS OSC1/CLKI VDD

RE2/AN7/CS

RE1/AN6/WR

RE0/AN5/RD

RA5/AN4/SS/LVDIN

RA4/T0CKI

* Es el pin RB3 alternativo para la multiplexación pin CCP2.

DS39564C-page4 2006 Microchip Technology Inc.

PIC18FXX2

PIC

18F

442

P

IC1

8F

45

2

PIC

18F

24

2

PIC

18F

25

2

Diagramas de pines (Cont. d ')

DIP

MCLR / VPP 1

RA0/ AN0 2

RA1/ AN1 3 RA2/ AN2/VREF-

4

RA3/AN3/VREF + 5

RA4/ T0CKI 6

RA5/AN4/SS/LVDIN 7

RE0 /RD/ AN5 8

RE1/WR/AN6 9

RE2/CS/AN7 10

Enfermedad venéreaD11

VSS 12

OSC1/CLKI 13 OSC2/CLKO/RA6 14

RC0/T1OSO/T1CKI 15

RC1/T1OSI/CCP2 * 16

RC2/CCP1 17

RC3/SCK/SCL 18

RD0/PSP019

RD1/PSP1 20

40 RB7/PGD

39RB6/PGC

38 RB5/PGM

37 RB4

36 RB3/CCP2 *

35 RB2/INT2

34 RB1/INT1

33 RB0/INT0

32VDD

31 VSS

30 RD7/PSP7

29 RD6/PSP6

28 RD5/PSP5

27RD4/ PSP4

26 RC7/RX/DT

25 RC6/TX/CK

24 RC5/SDO

23 RC4/SDI/SDA

22 RD3/PSP3

21 RD2/PSP2

Nota: Pin compatible con 40-pin dispositivos PIC16C7X.

DIP, SOIC

MCLR / VPP 1

RA0 / AN0 2

RA1 / AN1 3

RA2/ AN2/VREF- 4

RA3/ AN3/VREF + 5

RA4/ T0CKI 6

RA5/ AN4/SS/LVDIN 7

VSS 8

OSC1/CLKI 9

OSC2/CLKO/RA6 10

RC0/T1OSO/T1CKI 11

RC1/T1OSI/CCP2 * 12

RC2/CCP1 13

28RB7/PGD

27RB6/PGC

26RB5/PGM

25 RB4

24RB3/CCP2 *

23 RB2/INT2

22 RB1/INT1

21 RB0/INT0

20 VDD

1VSS 9

18 RC7/RX/DT

17 RC6/TX/CK

16 RC5/SDO

RC3/SCK/SCL 14 15 RC4/ SDI / SDA

* Es el pin RB3 alternativo para la multiplexación pin CCP2.

2006 Microchip Technology Inc. DS39564C páginas 5

PIC18FXX2

Table de Contenidos

1.0 Vista general del equipo 7

2.0 Configuraciones del oscilador 17

3.0 Reset 25

4.0 Organización de la memoria 35

5.0 FLASH memoria de programa 55

6.0 Datos EEPROM Memoria 65

7.0 8 X 8 Hardware Multiplicador 71

8.0 Interrupciones 73

9.0 I / O Ports 87

10.0 Módulo Timer0 103

11.Módulo 0 Timer1 107

12.0 Timer2 Módulo 111

13.0 timer3 Módulo 113

14.0 Captura / Comparación / PWM (CCP) Módulos 117

15,0 Maestro Synchronous Serial Port (MSSP) Módulo 125

16,0 direccionable universal asíncrono síncrono transmisor receptor (USART) ........................................ ...................... 165

17.0 Compatible 10-bit de analógico a digital (A / D) 181

18.0 Baja Tensión Detectar 189

19.0 Características especiales de la CPU 195

20.0 Resumen Instrucción Set 211

21.0 Desarrollo 253

22.0 Características eléctricas 259

23.0 DC y AC Características Gráficos y cuadros 289

24.0 Packaging 305

Apéndicesx A: Historial de revisiones 313

Apéndicesx B: Diferencias de dispositivos 313

Apéndicesx C: Consideraciones de conversión 314

Apéndicesx D: La migración desde el inicio a los dispositivos mejorados 314

Apéndicesx E: La migración de gama media a dispositivos mejorados 315

ApéndicesF x: La migración de gama alta a dispositivos mejorados 315

Index 317

On-Line Support 327

Reader Respuesta 328

PIC18FXX2 Identificación de Productos 329

DS39564C-page6 2006 Microchip Technology Inc.

PIC18FXX2

TO ESTIMADOS CLIENTES

Yot es nuestra intención de proporcionar a nuestros valiosos clientes con la mejor documentación posible para asegurar el uso

exitoso de sus productos Microchip. Para ello, vamos a seguir mejorando nuestras publicaciones para satisfacer mejor sus

necesidades. Nuestras publicaciones serán refinados y mejorados como nuevos volúmenes y actualizaciones se introducen.

Yoi usted tiene alguna pregunta o comentario acerca de esta publicación, por favor comuníquese con el Departamento de

Comunicaciones de Marketing por correo electrónico a [email protected] or fax el Reader Formulario de Respuesta

yon la parte de atrás de esta hoja de datos a (480) 792-4150. Damos las bienvenida a sus comentarios.

La mayoría actual Hoja de Datos

To obtener la versión más actualizada de esta hoja de datos, por favor regístrese en nuestro sitio Web en todo el mundo en:

http://www.microchip.com

You puede determinar la versión de la ficha de datos mediante el examen de su número de la literatura se encuentra en la parte inferior esquina exterior de cada página. El último carácter del número literatura es el número de versión (por ejemplo, DS30000A es la versión A del documento DS30000).

Erratun

Lan fe de erratas, describiendo pequeñas diferencias de funcionamiento de la hoja de datos y soluciones recomendadas, pueden existir para los dispositivos actuales. Como dispositivo / documentación temas sean conocidos por nosotros, vamos a publicar una fe de erratas. La fe de erratas se especificará la revisión de silicio y la revisión del documento al que se aplica.

To Determinar si existe una fe de erratas para un dispositivo en particular, póngase en contacto con uno de los siguientes:

• Sitio Web de Microchip Worldwide; http://www.microchip.com

• local Su oficina de ventas de Microchip (ver última página)

When contacto con una oficina de ventas, por favor, especifique qué dispositivo, la revisión de la hoja de silicio y datos (incluir el número de la literatura) que está utilizando.

Cliente Sistema de Notificación

Register en nuestro sitio web en www.microchip.com to recibir la información más actualizada sobre todos nuestros productos.

2006 Microchip Technology Inc. DS39564C páginas 7

PIC18FXX2

NOTAS:

DS39564C-page8 2006 Microchip Technology Inc.

PIC18FXX2

10.0 Vista general del equipo

Este documento contiene información específica del

dispositivo para los siguientes dispositivos:

• PIC18F242 • PIC18F442

• PIC18F252 • PIC18F452

Thesdispositivos electrónicos vienen en paquetes de

28-pin y 40/44-pin. Los dispositivos de 28-pin no tiene

un Puerto Paralelo Esclavo (PSP) ejecutado y el

número de analógico a digital (A / D) canales de

entrada del convertidor se reduce a 5. Una visión

general de las características que se muestran en la

Tabla 1-1.

The después de dos figuras son diagramas de

bloques de dispositivos ordenados por número de

pines: 28-pin para la Figura 1-1 y la Figura 1-2 para

40/44-pin. El 28-pin y pinouts 40/44-pin se enumeran

en la Tabla 1-2 y Tabla 1-3, respectivamente.

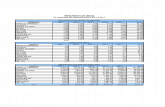

TABLE 1-1: Características del aparato

Características

PIC18F242 PIC18F252 PIC18F442 PIC18F452

Operating Frecuencia DC - 40 MHz DC - 40 MHz DC - 40 MHz DC - 40 MHz

PrograMemoria m (Bytes) 16K 32K 16K 32K

PrograMemoria m (Instrucciones) 8192 16384 8192 16384

Datuna memoria (bytes) 768 1536 768 1536

Datuna memoria EEPROM (bytes)

256 256 256 256

InterrupciónFuentes camisetas 17 17 18 18

I / O Ports Conexiones A, B, C

Conexiones A, B, C

Puertos A, B, C, D, E

Puertos A, B, C, D, E Tiempors 4 4 4 4

Capture / Compare / PWM Módulos

2 2 2 2

Comunicaciones serie

MSSP,

USART

direccionabl

es

MSSP,

USART

direccionabl

es

MSSP,

USART

direccionabl

es

MSSP,

USART

direccionabl

es Comunicaciones paralelas - - PSP PSP

10-bit analógico a digital del módulo

5 canales de entrada

5 canales de entrada

8 canales de entrada

8 canales de entrada

RESETS (y retrasos)

POR, BOR, REINICIO

Instrucción, Stack

completo,

Stack Underflow

(PWRT, OST)

POR, BOR, REINICIO

Instrucción, pila

completa,

Stack Underflow

(PWRT, OST)

POR, BOR, REINICIO

Instrucción, Stack

completo,

Stack Underflow

(PWRT, OST)

POR, BOR, REINICIO

Instruction, Stack

completo,

Stack Underflow

(PWRT, OST) Programmable baja tensión

Deproteger Vosotross

Vosotross

Vosotross

Vosotross

ProgrammablE Brown-out Restablecer

Sí Vosotross

Sí Vosotross Instrucción Set 75 Instrucciones 75 Instrucciones 75 Instrucciones 75 Instrucciones

Paquetes

28-pin DIP

28-pin SOIC

28-Pin DIP

28-pin SOIC

40-Pin DIP

44-pin PLCC

44-pin TQFP

40-pin DIP

44Pines PLCC

44Pines TQFP

2006 Microchip Technology Inc. DS39564C páginas 9

PIC18FXX2

TaPuntero ble

inc / dec lógica

4 BSR

12 4

FSR0

FSR1

FSR2

Bank0, F

12

inc / dec

lógica

Instrucción

Decodificar y Control

Correosw

er-up Tiemp

or Oscyollat

or Iniciar-up Timer Correoswer-on Reajustar Washington

tchdog Timer

Brown-out

Reajustar

Helow Voltaje Programación

In-Circuit Depurador

TIming Generación

WREG 8

FIGURA 1-1: DIAGRAMA DE BLOQUES PIC18F2X2

Bus de Datos <8>

21

8 8 8

21

Datun

pestillo

DatunRAM

Address Latch

CorreosRTLa

RA0/AN0

RA1/AN1

RA2/AN2/VREF

-

RA3/AN3/VREF

+ RA4/T0CKI

Dirección Latch

21 PCLATU PCLATH (2)

12 RA5/AN4/SS/LVDIN

RA6

ProgramMemoria (Up a 2 Mbytes)

PCU PCH P CL Dirección <12>

De retención de datos

Programa Contador

31 Nivel de Pila

16

TLatch poder

Descodificar

OSC2/CLKO

8 ROM Latch

Instrucción Registro

PRODH

8

Prödl

CorreosRTuberculosis

RB1/INT1 RB2/ INT2

RB3/CCP2(1)

RB4

RB5/ PGM RB6/PCG RB7/PGD

OSC1/CLKI

T1OSCI T1OSCO

MCLR

VDD,

VSS

4X PLL

Precision Voltaje

Referencia

3

BIT OP

8

8 x 8 Multiply

8

8

8

ALU <8>

8

PORTC

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2(1)

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

Timer0 Timer1 Timer2 Timer3 A / D Converter

CCP1

CCP2

Maestro

síncrono

Serial Port

Direccionable

USART

Data EEPROM

Nota 1: Opmultiplexación cional de CCP2 de entrada / salida con RB3 está habilitado por la selección de bit de configuración.

2:Thlos bits electrónicos de alto orden de la dirección directa para la RAM son del registro BSR (a excepción de la MOVFF instrucción).

3:Hombrey del propósito general I / O pins son multiplexados con una o más funciones de los módulos periféricos. Las combinaciones de multiplexación dependen del dispositivo.

DS39564C-page10 2006 Microchip Technology Inc.

PIC18FXX2

12 4 FSR0 Bank0, F

FSR1 FSR2

inc /

dec lógica

4 BSR

Power-up Timer

Oscyollator

Iniciar-up Timer Power-on Reajustar

Washingtontchdog Tiemp

or Brown-out

Reajustar

Helow Voltaje Programación

In-Circuit Debugger

WREG 8

TPuntero poder

inc / dec lógica

TIming Generación

FIGURA 1-2: DIAGRAMA DE BLOQUES PIC18F4X2

Bus de Datos <8>

21

8 8 8

21

Datun pestillo

DatunRAM (hasta 4K

alcance de la dirección)

Address Latch

PORTLa

RA0/ AN0

RA1/ AN1

RA2/ AN2/VREF-

RA3/AN3/VREF +

RA4/T0CKI

RA5/AN4/SS/LVDI

N

Ad Plantillass Latch

21 PCLATU Ordenador personalMALLA

(2) 12

RA6

ProgramMemoria (Up a 2 Mbytes)

PCU

PCH PCL

Dirección <12>

PORTB

De retención de datos

16

TaLatch ble

PrOGRAMA Contador

31 Nivel de

Pila

RB0/INT0

RB1/INT1 RB2/ INT2

12 RB3/CCP2(1)

RB4

RB5/PGM

RB7/PGD

OSC2/CLKO OSC1/CLKI

T1OSCI T1OSCO

MCLR

VDD,

VSS

8

Instrucció

n Decodificar y Control

4X PLL

Precision Voltaje

Referencia

ROM Latch

Instrucción

Registro

3

BIT OP

8

8

PRODH Prödl

8 x 8 Multiply

8

8

8

ALU <8>

8

POTc

PORTD

PORTE

RC0/T1OSO/T1CKYo RC1/T1OSI/CCP2(1

)

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RD0/ PSP0 RD1/ PSP1

RD2/ PSP2

RD3/ PSP3 RD4/ PSP4

RD5/ PSP5

RD6/ PSP6

RD7/ PSP7

RE0/AN5/RD

RE1/AN6/WR

RE2/AN7/CS

Timer0 Timer1 Timer2 Timer3 A /D Converter

CCP1

CCP2

Mamáster síncrono

Serial puerto

Anunciodres

sable USART

Parallel Puerto Esclavo

Datos de EEPROM

Nota 1: Multiplexación opcional de CCP2 de entrada / salida con RB3 está habilitado por la selección de bit de configuración.

2006 Microchip Technology Inc. DS39564C páginas 11

PIC18FXX2

2:Los bits de orden superior de la dirección directa de la RAM son del registro BSR (excepto para el MOVFF entrucción).

3:Muchos de los fines generales de E / S pins son multiplexados con una o más funciones de los módulos periféricos. Las

combinaciones de multiplexación dependen del dispositivo.

DS39564C-page12 2006 Microchip Technology Inc.

PIC18FXX2

TABLE 1-2: PIC18F2X2 pinout I / O DESCRIPCIONES

Pin Nombre

Pen el número

Pin

Type

Buffer

Type

Descripción

DIP SOIC

MCLR / VPP

MCLR

VPP

1 1

I

I

ST

ST

Master Clear (entrada) o de programación de alto

voltaje ICSP permitir pin.

Master Clear (Reset) de entrada. Este pin es un activo bajo

RESET para el dispositivo.

Programación ICSP alta tensión permitir pin. NC - - - - ThesE PIN debe dejarse sin conectar.

OSC1/CLKI

OSC1

CLKI

9 9 I

I

ST

CMOS

Oscillator cristal o entrada de reloj externo.

Oscillator cristal o entrada externa de reloj fuente.

ST búfer cuando se configura en modo RC, CMOS

contrario. Reloj externo fuente de entrada. Siempre

asociado con

pin Función OSC1. (Véase relacionados

OSC1/CLKI, alfileres OSC2/CLKO.) OSC2/CLKO/RA6

OSC2

CLKO

RA6

10 10 O

O

Yo/ O

-

-

TTL

Oscillator cristal o de reloj de salida.

Oscillator salida de cristal. Se conecta al

cristal o resonador en modo de oscilador de

cristal.

Yon RC modo, pin OSC2 salidas CLKO que tiene 1/4

ªfrecuencia e de OSC1, y denota la tasa de ciclo de

instrucción.

General Objetivo I / O pin.

RA0/AN0

RA0

AN0

RA1/AN1

RA1

AN1

RA2/AN2/VREF

- RA2

AN2

VREF-

RA3/AN3/VREF

+

RA3

AN3

VREF+

RA4/T0CKI

RA4

T0CKI

RA5/AN4/SS/LVDIN

RA5

AN4

SS

LVDIN

RA6

2

3

4

5

6

7

2

3

4

5

6

7

Yo/

Oh

I

Yo/

Oh

I

Yo/

Oh

I

Yo

Yo/

Oh

I

Yo

Yo/

Oh

I

Yo/

Oh

I

Yo

Yo

TTL

analógi

co

TTL

analógi

co

TTL

analógi

co

analógi

co

TTL

analógi

co

analógi

co

ST /

ST OD

TTL

analógi

co ST

analógi

co

PORTA es un bi-direccional de E / S del puerto.

Digital I / O.

Entrada

analógica 0.

Digital I / O.

Entrada

analógica 1.

Digital I / O.

Entrada

analógica 2.

A / D de referencia de tensión (baja) de entrada.

Digital I / O.

Entrada

analógica 3.

La/ Referencia D Tensión (educación superior) de entrada.

Digital I / O. Abra drenar cuando se configura

como salida. Timer0 entrada de reloj externo.

Digital I / O.

Entrada

analógica 4.

SPI entrada Slave Select.

Helow Voltaje entrada de detección.

Ver el pasador OSC2/CLKO/RA6.

Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

2006 Microchip Technology Inc. DS39564C páginas 13

PIC18FXX2

TABLE 1-2: PIC18F2X2 pinout I / O DESCRIPCIONES (CONTINUACIÓN)

Pin Nombre

Pin Número

Pin

Type

Buffer

Type

Descripción

DIP SOIC

RB0/INT0

RB0

INT0

RB1/INT1

RB1

INT1

RB2/INT2

RB2

INT2

RB3/CCP2

RB3

CCP2

RB4

RB5/PGM

RB5

PGM

RB6/PGC

RB6

PGC

RB7/PGD

RB7

PGD

21

22

23

24

25

26

27

28

21

22

23

24

25

26

27

28

Yo/

O

h

I

Yo/

O

h

I

Yo/

O

h

I

Yo/

O I

/ O

Yo/ O

Yo/

O I

/ O

Yo/

O I

/ O

Yo/

O I

/ O

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

TTL

ST

TTL

ST

TTL

ST

PORTB es un bi-direccional de E / S del puerto. PORTB

software puede ser programado para internos débiles pull-

ups en todas las entradas.

Digital I / O.

0 Interrupción externa.

Interrupción externa

1. Digital I / O.

Interrupción externa 2.

Digital I / O.

Entrada Capture2, Compare2 salida, PWM2

salida. Digital I / O.

Enterrupt-al-cambiar pin.

Digital I / O. Interrupción-al-cambiar pin.

Helow Tensión de programación ICSP permitir pin.

Digital I / O. Interrupción-al-cambiar pin.

En-Circuit Debugger y pin ICSP programación del reloj.

Digital I / O. Interrupción-al-cambiar pin.

En-Circuit Debugger y pin ICSP programación de datos. Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

DS39564C-page14 2006 Microchip Technology Inc.

PIC18FXX2

TABLE 1-2: PIC18F2X2 pinout I / O DESCRIPCIONES (CONTINUACIÓN)

Pin Nombre

Pen el número

Pin

Type

Buffer

Type

Descripción

DIP SOIC

RC0/T1OSO/T1CKI

RC0

T1OSO

T1CKI

RC1/T1OSI/CCP2

RC1

T1OSI

CCP2

RC2/CCP1

RC2

CCP1

RC3/SCK/SCL

RC3

SCK

SCL

RC4/SDI/SDA

RC4

SDI

SDA

RC5/SDO

RC5

SDO

RC6/TX/CK

RC6

TX

CK

RC7/RX/DT

RC7

RX

DT

11

12

13

14

15

16

17

18

11

12

13

14

15

16

17

18

Yo/

O

O

Yo

Yo

E /

S

de

I /

O

Yo/

O I

/ O

Yo/

O I

/ O

I /

O

Yo

E /

S

de

I /

O

Yo/

O

O

Yo/

O

O I

/ O

Yo

E /

S

de

I /

O

ST

-

ST

ST ST

CMOS

ST

ST

ST

ST

ST

ST

ST

ST

ST

-

ST

-

ST

ST

ST

ST

PORTC es un bi-direccional de E / S del puerto.

Digital I / O.

Timer1 salida del oscilador.

Timer1/Timer3 entrada de reloj

externo.

Digital I / O.

Timer1 oscilador de entrada.

Entrada Capture2, Compare2 salida, PWM2 salida.

Digital I / O.

Capture1 input/Compare1 output/PWM1 salida.

Digital I / O.

Synchronous reloj de entrada / salida serial para el

modo SPI. Entrada de reloj síncrona / salida serial

para el modo I2C

Digital I / O. SPI de entrada de datos. Los datos I2C I / O.

Digital I / O.

SPI salida de datos.

Digital I / O.

Asíncrono USART Transmit.

USART síncrona del reloj (ver relacionada RX / DT).

Digital I / O.

Asíncrono USART recibir.

USART de datos síncronos (ver relacionado TX / CK).

VSS 8, 19 8, 19 P - GReferencia ronda para la lógica y los pines de E / S.

VDD 20 20 P - Positive suministro para los pines lógicos y de I / O.

Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

2006 Microchip Technology Inc. DS39564C páginas 15

PIC18FXX2

TABLE 1-3: PIC18F4X2 pinout I / O DESCRIPCIONES

Pin Nombre

Pin Número

Pin

Type

Buffer

Type

Descripción

DIP PLCC TQFP

MCLR / VPP

MCLR

VPP

1 2 18

I

I

ST

ST

Master Clear (entrada) o ICSP alto voltaje

PROGRAMACIÓNg enable pin.

Master Clear (Reset) de entrada. Este pin es un

RESET activa baja en el dispositivo.

Programación ICSP alta tensión permitir pin.

NC - - - Estos pines se debe dejar sin conectar.

OSC1/CLKI

OSC1

CLKI

13 14 30 I

I

ST

CMOS

Oscilacióntor de cristal o entrada de reloj externo.

Oscillator cristal o entrada externa de reloj

fuente. ST búfer cuando se configura en modo

RC, CMOS contrario.

Reloj externo fuente de entrada. Siempre

asociado con pin OSC1 función. (Véase

relacionados OSC1/CLKI, alfileres OSC2/CLKO.)

OSC2/CLKO/RA6

OSC2

CLKO

RA6

14 15 31 O

O

I / O

-

-

TTL

Oscilacióntor de cristal o de reloj de salida.

Oscillator salida de cristal. Se conecta al

cristal o resonador en modo de oscilador de

cristal.

Yon RC modo, OSC2 pasador salidas

CLKO, que tiene 1/4 de la frecuencia de

OSC1 y denota la tasa de ciclo de

instrucción.

GenePropósito ral I / O pin.

RA0/AN0

RA0

AN0

RA1/AN1

RA1

AN1

RA2/AN2/VREF

- RA2

AN2

VREF-

RA3/AN3/VREF

+

RA3 AN3

VREF+

RA4/T0CKI

RA4 T0CKI

RA5/AN4/SS/LVDIN

RA5

AN4

SS

LVDIN

RA6

2

3

4

5

6

7

3

4

5

6

7

8

19

20

21

22

23

24

I /

O I

I /

O I

I /

O I

Yo

I /

O I

Yo

I /

O I

I /

O I

I

I

TTL

analógi

co

TTL

analógi

co

TTL

Analóg

ico

Analóg

ico

TTL

Analóg

ico

Analóg

ico

ST /

ST OD

TTL

ST

analógi

ca

analógi

ca

PORTA es un bi-direccional puerto I / O.

Digital I / O.

Entrada

analógica 0.

Digital I / O.

Entrada

analógica 1.

Digital I / O.

Entrada

analógica 2.

A / D de referencia de tensión (baja) de entrada.

Digital I / O.

Entrada

analógica 3.

A / D de referencia de tensión (alta) de entrada.

Digital I / O. Abra drenar cuando se configura

como salida. Timer0 entrada de reloj externo.

Digital I / O.

Entrada

analógica 4.

SPI entrada Slave Select.

Detección de bajo voltaje

de entrada.

(Véase el pasador OSC2/CLKO/RA6.)

Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

DS39564C-page16 2006 Microchip Technology Inc.

PIC18FXX2

TABLE 1-3: PIC18F4X2 pinout I / O DESCRIPCIONES (CONTINUACIÓN)

Pin Nombre

Pin Número

Pin

Type

Buffer

Type

Descripción

DIP PLCC TQFP

RB0/INT0

RB0

INT0

RB1/INT1

RB1

INT1

RB2/INT2

RB2

INT2

RB3/CCP2

RB3

CCP2

RB4

RB5/PGM

RB5

PGM

RB6/PGC

RB6

PGC

RB7/PGD

RB7

PGD

33

34

35

36

37

38

39

40

36

37

38

39

41

42

43

44

8

9

10

11

14

15

16

17

I /

O

I

I /

O

I

I /

O

I

E /

S

E /

S

I / O

E /

S

E /

S

E /

S

E /

S

E /

S

E /

S

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

TTL

ST

TTL

ST

TTL

ST

PORTB es un bi-direccional de E / S del puerto.

PORTB software puede ser programado para

internos débiles pull-ups en todas las entradas.

Digital I / O.

0 Interrupción externa.

Interrupción externa

1. Digital I / O.

Interrupción externa 2.

Digital I / O.

Entrada Capture2, Compare2 salida, PWM2

salida. Digital I / O. Interrupción-al-cambiar pin.

Digital I / O. Interrupción-al-cambiar pin.

Helow Tensión de programación ICSP permitir pin.

Digital I / O. Interrupción-al-cambiar pin.

En-Circuit Debugger y pin ICSP programación

del reloj.

Digital I / O. Interrupción-al-cambiar pin.

En-Circuit Debugger y pin ICSP programación

de datos. Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

2006 Microchip Technology Inc. DS39564C páginas 17

PIC18FXX2

TABLE 1-3: PIC18F4X2 pinout I / O DESCRIPCIONES (CONTINUACIÓN)

Pin Nombre

Pin Número

Pin

Type

Buffer

Type

Descripción

DIP PLCC TQFP

RC0/T1OSO/T1CKI

RC0

T1OSO

T1CKI

RC1/T1OSI/CCP2

RC1

T1OSI

CCP2

RC2/CCP1

RC2

CCP1

RC3/SCK/SCL

RC3

SCK

SCL

RC4/SDI/SDA

RC4

SDI

SDA

RC5/SDO

RC5

SDO

RC6/TX/CK

RC6

TX

CK

RC7/RX/DT

RC7

RX

DT

15

16

17

18

23

24

25

26

16

18

19

20

25

26

27

29

32

35

36

37

42

43

44

1

I /

O

O

Yo

I /

O I

/ O

E /

S

E /

S

E /

S

E /

S

I / O

I /

O I

/ O

I /

O

O

I /

O

O I

/ O

I /

O I

/ O

ST

-

ST

ST ST

CMOS

ST

ST

ST

ST

ST

ST

ST

ST

ST

-

ST

-

ST

ST

ST

ST

PORTC es un bi-direccional de E / S del puerto.

Digital I / O.

Timer1 salida del oscilador.

Timer1/Timer3 entrada de reloj

externo.

Digital I / O.

Timer1 oscilador de entrada.

Entrada Capture2, Compare2 salida, PWM2 salida.

Digital I / O.

Capture1 input/Compare1 output/PWM1 salida.

Digital I / O.

Synchentrada ronous reloj serial / salida para

Modo SPI.

Synchentrada ronous reloj serial / salida para

Modo I2C.

Digital I / O.

SPI de

entrada de

datos. Los

datos I2C I /

O.

Digital I / O.

SPI salida de datos.

Digital I / O.

UAsíncrono de transmisión SART.

USART síncrona del reloj (ver relacionada RX / DT).

Digital I / O.

UAsíncrono SART recibir.

USART de datos síncronos (ver relacionado TX / CK).

Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

DS39564C-page18 2006 Microchip Technology Inc.

PIC18FXX2

TABLE 1-3: PIC18F4X2 pinout I / O DESCRIPCIONES (CONTINUACIÓN)

Pin Nombre

Pin Número

Pin

Type

Buffer

Type

Descripción

DIP PLCC TQFP

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

19

20

21

22

27

28

29

30

21

22

23

24

30

31

32

33

38

39

40

41

2

3

4

5

I /

O I

/ O

I /

O I

/ O

I /

O I

/ O

I /

O

I / O

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

PORTD es un bi-direccional puerto I / O, o un puerto

esclavo paralelo (PSP) para la conexión con un

puerto de microprocesador. Estos pernos tienen

buffers de entrada TTL cuando PSP módulo está

habilitado.

Digital I / O.

Parallel Data puerto de

esclavos. Digital I / O.

Parallel Data puerto de esclavos.

Digital I / O.

Parallel Data puerto de

esclavos. Digital I / O.

Parallel Data puerto de esclavos.

Digital I / O.

Parallel Data puerto de

esclavos. Digital I / O.

Parallel Data puerto de esclavos.

Digital I / O.

Parallel Data puerto de

esclavos. Digital I / O.

Parallel Data puerto de esclavos.

RE0/RD/AN5

RE0

RD

AN5

RE1/WR/AN6

RE1

WR

AN6

RE2/CS/AN7

RE2

CS

AN7

8

9

10

9

10

11

25

26

27

I / O

I / O

I / O

ST

TTL

Analógi

ca

ST

TTL

Analógi

ca

ST

TTL

Analógi

ca

PORTE es un bi-direccional de E / S del puerto.

Digital I / O.

Lea el control para el puerto

paralelo esclavo (véase también

WR y los pines CS). Entrada

analógica 5.

Digital I / O.

Writo de control para el puerto paralelo esclavo

(Ver los pins CS y

RD). Entrada

analógica 6.

Digital I / O.

Chip Select para el control del puerto paralelo esclavo

(See relacionada con RD

y WR). Entrada analógica

7.

VSS 12, 31 13, 34 6, 29 P - GReferencia ronda para la lógica y los pines de E / S.

VDD 11, 32 12, 35 7, 28 P - Positive suministro para los pines lógicos y de I / O.

Leyenda: TTL = TTL compatible CMOS de entrada = entrada o salida CMOS compatible

ST = entrada Trigger Schmitt CMOS con niveles de entrada I =

O = P = Potencia de salida

OD = Open Drain (sin diodo P a VDD)

2006 Microchip Technology Inc. DS39564C páginas 19

PIC18FXX2

Rangos Probado:

Modo Freq C1 C2

XT 455 kHz

2.0 MHz

4.0 MHz

68 a 100 pF

15 a 68 pF

15 a 68 pF

68 a 100 pF

15 a 68 pF

15 a 68 pF HS 80,0 MHz

16.0 MHz 10 a 68 pF

10 a 22 pF 10 a 68 pF

10 a 22 pF These valores son orientativos diseño único.

See notas que siguen a esta tabla.

Resonadores utilizado:

455 kHz Panasonic EFO-A455K04B ± 00,3% 2,0 MHz Murata Erie CSA2.00MG ± 00,5% 4,0 MHz Murata Erie CSA4.00MG ± 00,5% 8,0 MHz Murata Erie CSA8.00MT ± 00,5% 160,0 MHz

Murata Erie CSA16.00MX ± 00,5% Todos los resonadores utilizados no han incorporado en los condensadores.

R

2,0 OSCONFIGURACIONES oscilador

2.1 Tipos de oscilador

El PIC18FXX2 puede ser operado en ocho modos de

oscilador diferentes. El usuario puede programar tres

Configuraciones de bits (FOSC2, FOSC1 y FOSC0)

para seleccionar uno de los ocho modos:

TABLE 2-1: CAPACITOR DE SELECCIÓN

PARA resonadores de

cerámica

1. LP Helow Power Crystal 2. XT Cristal / Resonador 3. HS Cristal de alta velocidad /

Resonator 4. HS + PLL Cristal de alta velocidad /

Resonador con PLL activado 5. RC External resistencia /

condensador 6. Rcio Resistencia externa / condensador con

YoPin E / S activada 7. CE Reloj externo 8. ECIO Reloj externo con pin I / O

activada

2.2 Oscilador de Cristal / Cerámica

Resonadores

Yon XT, LP, SA o SA + modos oscilador PLL, un

resonador de cristal o de cerámica está conectado a

los OSC1 y OSC2 pins para establecer oscilación. La

Figura 2-1 muestra las conexiones de los pines.

The diseño de oscilador PIC18FXX2 requiere el uso

de un cristal de corte paralelo.

Nota: El uso de un cristal de corte en serie

puede dar una frecuencia fuera de las

especificaciones de los fabricantes de

cristal.

FIGURA 2-1: CRYSTAL / CERAMIC

RESONATOR

OPERACIÓN (HS, XT o

configuración LP)

Nota 1: Una mayor capacitancia aumenta la

estabilidad del oscilador, pero también

aumenta el tiempo de puesta en marcha.

2:When operativo por debajo de 3V VDD, o

cuando se utilizan ciertas resonadores

de cerámica en cualquier tensión, puede

ser necesario el uso de alta ganancia en

modo HS, trate de un resonador de

frecuencia más baja, o cambiar a un

oscilador de cristal.

3:Since cada resonador / cristal tiene sus

propias características, el usuario debe

consultar al fabricante del resonador /

cristal para valores apropiados de los

componentes externos, o verificar el

funcionamiento del oscilador.

C1(1)

OSC1

XTAL

RF

)

A Interno Lógica

(3

C2(1)

(2) S

OSC2

SLEEP

PIC18FXXX

Noe 1: See la Tabla 2-1 y la Tabla 2-2 para los

valores recomendados de C1 y C2.

2:Una resistencia en serie (RS) puede ser requerido para

LaT tira cortada cristales.

3:RF varía con el modo oscilador elegido.

DS39564C-page20 2006 Microchip Technology Inc.

PIC18FXX2

Rangos Probado:

Modo Freq C1 C2

LP 32.0 kHz 33 pF 33 pF

200 kHz 15 pF 15 pF

XT 200 kHz 22-68 pF 22-68 pF

10,0 MHz 15 pF 15 pF

40,0 MHz 15 pF 15 pF

HS 40,0 MHz 15 pF 15 pF

80,0 MHz 15-33 pF 15-33 pF

20.0 MHz 15-33 pF 15-33 pF

25.0 MHz 15-33 pF 15-33 pF

These valores son orientativos diseño único.

See notas que siguen a esta tabla.

Cristales usado

32.0 kHz Epson C-001R32.768K-A ± 20 PPM

200 kHz STD XTL 200.000KHz ± 20 PPM

10,0 MHz ECS ECS-10-13-1 ± 50 PPM

40,0 MHz ECS ECS-40-20-1 ± 50 PPM

80,0 MHz EPSOn 8.000m CA-301-C ± 30 PPM

200,0 MHz Epson CA-301-C 20.000m ± 30 PPM

TABLE 2-2: SELECCIÓN DE CONDENSADOR

PARA OSCILADOR DE

CRISTAL

2.3 RC Oscilador

Por el momento las aplicaciones no sensibles, el "RC"

y "Comércio" Opciones de dispositivos ofrecen un

ahorro adicional de costes. La frecuencia del oscilador

RC es una función de la tensión de alimentación, la

resistencia (REXT) y el condensador (CEXT) los

valores y la temperatura de funcionamiento. Además

de esto, la frecuencia del oscilador puede variar de

una unidad a otra debido a variaciones normales de

parámetros de proceso. Además, la diferencia en

capacitancia de bastidor de conductores entre los

tipos de paquete también afectará a la frecuencia de

oscilación, especialmente para valores bajos CEXT.

El usuario también debe tener en cuenta la variación

debido a la tolerancia de los componentes externos

de I y C utilizados. La figura 2-3 muestra cómo la

combinación R / C está conectado.

Yon el modo de oscilador RC, la frecuencia del

oscilador dividida por 4 está disponible en el pin

OSC2. Esta señal puede ser usada para fines de

prueba o para sincronizar la lógica otro.

Nota: Yof la frecuencia del oscilador dividida por

4 señal no se requiere en la aplicación, se

recomienda utilizar el modo rcio para

ahorrar energía.

FIGURA 2-3: MODO RC OSCILLATOR

VDD

Nota 1: Una mayor capacitancia aumenta la

estabilidad del oscilador, pero también

aumenta el tiempo de puesta en marcha.

2:Rs puede ser necesario en modo HS, así

como el modo XT, para evitar

sobrecargas cristales con especificación

de bajo nivel de accionamiento.

REXT

CEXT

VSS

FOSC / 4

OSC1 OSC2/CLKO

Internal

Clock PIC18FXXX

3:Since cada resonador / cristal tiene sus

propias características, el usuario debe

consultar al fabricante del resonador /

cristal para valores apropiados de los

componentes externos., o verificar el

funcionamiento del oscilador.

Lan fuente de reloj externa también puede ser

conectado al pin OSC1 en los modos de HS, XT y LP,

como se muestra en la Figura 2-2.

FIGURA 2-2: OPERACIÓN EXTERNA entrada

de reloj (HS, XT o LP OSC

CONFIGURACIÓN)

Recomvalores recomendadas: 3 kΩ ≤ REXT≤ 100 kΩ

CEXT> 20pF

The Comércio funciones de oscilador modo como el

modo RC, con la salvedad de que el pin OSC2 se

convierte en un adicional de propósito ge-neral I / O

pin. El pin de E / S se convierte en el bit 6 de PORTA

(RA6).

Clock de OSC1

Ext. Sistema PIC18FXXX

Abierto OSC2

2006 Microchip Technology Inc. DS39564C páginas 21

PIC18FXX2

MU

X

2.4 Entrada de reloj externo

The CE y modos de ECIO oscilador requieren una

fuente de reloj externa para ser conectada al pin

OSC1. El dispositivo de retroalimentación entre OSC1

y OSC2 está activado

FIGURA 2-5: OPERACIÓN EXTERNA DE

ENTRADA DEL RELOJ

(ECIO CONFIGURACIÓN)

def en estos modos para ahorrar energía. No hay oscilación

Clock de OSC1

tor de arranque tiempo necesario después de un reinicio de encendido o

Ext. Sistema PIC18FXXX

unespués de una recuperación desde el modo SLEEP.

Yon el modo de oscilador CE, la frecuencia del

oscilador dividida por 4 está disponible en el pin

OSC2. Esta señal puede ser usada para fines de

prueba o para sincronizar la lógica otro. La Figura 2-4

muestra las conexiones de patillas para la CE

RA6

2.5 HS / PLL

I /O (OSC2)

Oscilacióntor modo.

FIGURA 2-4: OPERACIÓN EXTERNA DE

ENTRADA DEL RELOJ

(CE CONFIGURACIÓN)

A Phase Locked Loop circuito se proporciona como un programa-

MABLe opción para los usuarios que desean

multiplicar la frecuencia de la señal de oscilador de

cristal de entrada por 4. Para una frecuencia de

entrada de reloj de 10 MHz, la frecuencia del reloj

interno se multiplicará a 40 MHz. Esto es útil para los

clientes que están interesados en debido a los

cristales de alta frecuencia EMI. Clock de OSC1

Ext. Sistema PIC18FXXX The PLL sólo se puede activar cuando el oscilador con-

Figuración pedacitos están programados para el modo HS. Si están

FOSC / 4 OSC2 programad por cualquier otro modo, el PLL no está

habilitado y el reloj del sistema vendrá directamente

de OSC1. The ECIO funciones del oscilador de modo como el modo de CE,

excepciónt que el pin OSC2 adicional se convierte en

un objetivo gene-ral I / O pin. El pin de E / S se

convierte en el bit 6 de PORTA (RA6). La Figura 2-5

muestra las conexiones de los pines para el modo de

oscilador ECIO.

The PLL es uno de los modos de la FOSC <2:00>

URACIÓN config-bits. El modo de oscilador se

especifica durante la programación del dispositivo.

Un temporizador de bloqueo de PLL se utiliza para

asegurar que el PLL se ha cerrado antes de la

ejecución dispositivo se inicia. El temporizador de

bloqueo de PLL tiene un tiempo de espera que se

llama TPLL.

FIGURA 2-6: DIAGRAMA DE BLOQUE PLL

(Configuración de HS poco

Osc Registrarse)

PLL Enable

OSC2

Cristal

Osc

Phase Comparator

FIN

Bucle

Filter

VCO

OSC1

FOUT SYSCLK

Divide por 4

DS39564C-page22 2006 Microchip Technology Inc.

PIC18FXX2

MU

X

2.6 Oscilador de funciones de conmutación

Thdispositivos electrónicos PIC18FXX2 incluyen una

característica que permite que la fuente de reloj del

sistema que se conecta desde el oscilador principal a

un suplente fuente de reloj de baja frecuencia. Para

los dispositivos PIC18FXX2, esta fuente alternativa de

reloj es el oscilador Timer1. Si un cristal de baja

frecuencia (32 kHz, por ejemplo) se ha unido a las

Timer1 pins del oscilador y el oscilador Timer1 se ha

activado, el dispositivo puede cambiar a un bajo

consumo Eje-

tion modo. La Figura 2-7 muestra un diagrama de

bloques de las fuentes de reloj del sistema. La función

de conmutación del reloj se activa programando el

oscilador de conmutación de habilitación (OSCSEN)

bit en Register1H configuración en un

'0 '. Conmutación del reloj se desactiva en un

dispositivo de borrado. Vea la Sección 11.0 para más

detalles sobre el Timer1 oscilador. Vea la Sección

19.0 para más detalles registro de configuración.

FIGURA 2-7: FUENTES DE DISPOSITIVOS DE RELOJ

PIC18FXXX

OSC2

OSC1

T1OSO

T1OSI

Main oscilador

DORMIR

TimerUn oscilador

T1OScen oscilador Enable

4 x PLL

TOS

C

TT1P

TOSC / 4

Clock

Fuente

TSCLK

Clock opción

Fuente para otros

módulos

2006 Microchip Technology Inc. DS39564C páginas 23

PIC18FXX2

R = poco legible W = bit Writable U = bit no implementado, leído como '0 '

- N = Valor en POR '1'Bit = se establece

'0'Bit = se borra x Bit = se desconoce

2.6.1 SISTEMA DE RELOJ INTERRUPTOR BIT

Thsistema electrónico reloj conmutación de fuente se

realiza bajo control de software. El reloj del sistema bit

switch, SCS (OSCCON <0>) controla la conmutación

del reloj. Cuando el bit SCS es '0 ', la fuente de reloj

del sistema proviene del oscilador principal que es

seleccionado por la FOSC configura-ción bits en

Register1H configuración. Cuando el bit SCS está

establecido, la fuente de reloj del sistema vendrá del

oscilador Timer1. El bit SCS está desactivada en

todas las formas de RESET.

REGISTRO 2-1: OSCCON REGISTRO

Nota: The oscilador Timer1 debe estar

habilitado y operativo para cambiar la

fuente de reloj del sistema. El oscilador

Timer1 se habilita estableciendo el bit

T1OSCEN en el registro Timer1 control

(T1CON). Si el oscilador Timer1 no está

activada ninguna de escritura en el bit

SCS serán ignorados (bit SCS forzado

borra) y el oscilador principal seguirá

siendo la fuente de reloj del sistema.

U-0-0 U U U-0-0-0 U U U-0-0 R/W-1

- - - - - - - SCS bit 7 bit 0

bit 7-1 Naciones

Unidasimplementado: Leer como 0 bit

'0 ' SCS: SysReloj tem poco

Interruptor

When OSCSEN configuración de bits = '0 'y poco T1OSCEN se establece:

1= Cambiar a Timer1 oscilador / reloj pin

0= Utilizar oscilador primario / reloj pin de entrada

When OSCSEN y T1OSCEN se encuentran en otros estados:

bit es forzado claro

Leyenda:

DS39564C-page24 2006 Microchip Technology Inc.

PIC18FXX2

2.6.2 TRANSICIONES OSCILADOR

Thdispositivos electrónicos PIC18FXX2 contienen

circuitos para evitar "interferencias" cuando se cambia

entre las fuentes del oscilador. Esencialmente, el

circuito de espera por ocho bordes ascendentes de la

fuente de reloj que el procesador está cambiando.

Esto asegura que la nueva fuente de reloj es estable y

que su ancho de pulso no será menor que el ancho

más corto de pulso de las dos fuentes de reloj.

La diagrama de tiempos que indica la transición desde

el oscilador principal para el oscilador Timer1 se

muestra en la Figura 2-8. El oscilador Timer1 se

supone que funciona mucho todo el tiempo. Después

de que el bit SCS está establecido, el procesador se

congela en el ciclo siguiente Q1 ocurriendo. Después

de ocho ciclos de sincronización se cuentan desde el

Timer1 oscilador, se reanuda la operación. No hay

retrasos adicionales son necesarios después de los

ciclos de sincronización.

Figura 2-8: Diagrama de tiempos para la transición del OSC1 A TIMER1 OSCILLATOR

T1OSI

OSC1

Q1 Q2 Q3 Q1 Q4

1

TT1P

2

Q1

3 4 5 6 7 8

Tscs

Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1

Reloj interno del sistema

(SCSOSCCON <0>)

PrOGRAMA Contador

TOSC

Ordenador personal

TDLY

PC + 2

PC + 4

Noe 1: Deponer en el reloj interno del sistema es de ocho ciclos del oscilador de sincronización.

The secuencia de eventos que tiene lugar cuando de

conmutación del oscilador Timer1 al oscilador

principal dependerá del modo del oscilador principal.

Además de los ocho ciclos de reloj del oscilador

principal, los retrasos adicionales pueden tener lugar.

Yof del oscilador principal está configurado para un

externo crys-tal (HS, XT, LP), entonces la transición

se llevará a cabo después de un oscilador de puesta

en marcha (TOST) ha ocurrido. Un diagrama de

tiempo, lo que indica la transición de la Timer1

oscilador para el oscilador principal para HS, XT y

modos LP, se muestra en la Figura 2-9.

FIGURA 2-9: TIEMPO DE TRANSICIÓN ENTRE TIMER1 Y OSC1 (HS, XT, LP)

Q3 Q4 Q1 TT1P

Q1 Q2 Q3 Q4 Q1 Q2 Q3

T1OSYo

OSC1

TOST

1 2 3 4 5 6 7 8

TSCS

OSC2

Sistema Interno Reloj

TOSC

(SCS

OSCCON <0>)

PrOGRAMA Contador PC PC + 2

Nota 1: TOST = 1024 TOSC (dibujo no está a escala).

PC + 6

2006 Microchip Technology Inc. DS39564C páginas 25

PIC18FXX2

Yof del oscilador principal está configurado para HS-

PLL modo, un oscilador de tiempo de inicio (TOST)

más un PLL adicional de tiempo de espera (TPLL) se

va a producir. El PLL tiempo de espera suele ser

2 ms y permite que el PLL para bloquear la frecuencia

del oscilador principal. Un diagrama de tiempo que

indica la transición desde el oscilador Timer1 al

oscilador principal para HS-PLL modo se muestra en

la figura 2-10.

FIGURA 2-10: TIEMPO DE TRANSICIÓN ENTRE TIMER1 Y OSC1 (HS CON PLL)

Q1 Q4 TT1P Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

T1OSI

OSC1

OSC2

Reloj PLL

TOST

TPLL

TOSC

TSCS

De entrada 1 2 3 4 5 6 7 8

Sistema Interno Reloj

SCS

(OSCCON <0>)

Contador de Programa PC PC + 2

Nota 1: TOST = 1024 TOSC (dibujo no está a escala).

PC + 4

Yof del oscilador principal está configurado en el RC,

rcio, CE o modos de ECIO, no hay ningún oscilador

de puesta en marcha de tiempo de espera. La

operación se reanudará después de ocho ciclos del

oscilador principal han sido contados. Un diagrama de

tiempo, lo que indica la transición desde el oscilador

Timer1 al oscilador principal para RC, rcio, CE y

modos de ECIO, se muestra en la figura 2-11.

FIGURA 2-11: TIEMPO DE TRANSICIÓN ENTRE TIMER1 Y OSC1 (CC, CE)

T1OS

Yo

OSC1

Q3 Q1 Q4

TT1P

TOSC

1 2 3 4 5 6 7 8

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

OSC2

Sistema Interno

Reloj

(SCSOSCCON <0>)

TSCS

PrOGRAMA Contador PC PC + 2

Nota 1: Modo RC Oscilador asumido.

PC + 4

DS39564C-page26 2006 Microchip Technology Inc.

PIC18FXX2

2.7 Efectos del modo de suspensión en el

El Chi-p oscilador

When el dispositivo ejecuta un DORMIR instrucción,

los relojes en el chip y el oscilador están apagados y

el dispositivo se lleva a cabo al comienzo de un ciclo

de instrucción (estado Q1). Con el oscilador de

apagado, los OSC1 y OSC2 señales se detendrá

oscilante. Dado que todo el transistor

scorrientes witching se han eliminado, el modo

SLEEP logra el más bajo consumo de corriente del

dispositivo (solamente las corrientes de fuga).

Habilitación de alguna de las funciones en el chip que

operará durante SLEEP aumentará la corriente

consumida durante el sueño. El usuario puede

despertar de su sueño a través de RESET externo,

Reset Watchdog Timer, o por medio de una

interrupción.

TABLE 2-3: OSC1 y OSC2 ESTADOS PIN en modo de reposo

OSC Mode OSC1 Pin OSC2 Pin

RC Resistencia flotante,

externo debe tirar

alto

A nivel lógico bajo

Rcio Resistencia flotante,

externo debe tirar

alto

Configurado como PORTA, bit 6

ECIO Floridaotante

Configurado como PORTA, bit 6 CE Floridaot

ante A nivel

lógico bajo LP, XT y HS Feedback convertidor

deshabilitado, en el nivel

de tensión de reposo

Feedback convertidor

deshabilitado, en el nivel

de tensión de reposo Nota: See la Tabla 3-1, en la "Reset " segundoción, por los tiempos de espera debidos a dormir y MCLR Reset.

2.8 Power-up retrasos

Encienda los retrasos son controlados por dos

temporizadores, para que nadie circuito de RESET

externo es necesario para la mayoría de aplicaciones.

Los retrasos asegurar que el dispositivo se mantiene

en RESET, hasta que la fuente de alimentación y

dispositivo de reloj son estables. Para obtener

información adicional sobre la operación RESET,

consulte la Sección 3.0.

El primer contador de tiempo es el temporizador de

encendido (PWRT), que proporciona opcionalmente

un retardo fijo de 72 ms (nominal) en el arranque

solamente (POR y BOR). El temporizador de segundo

es el oscilador de puesta en marcha del temporizador

(OST), destinado a mantener el chip en RESET hasta

que el oscilador de cristal es estable.

Ingenioh habilitado el PLL (SA / PLL modo de

oscilador), la secuencia de tiempo de espera después

de un Power-on Reset es diferente de otros modos de

oscilador. La secuencia de tiempo de espera es el

siguiente: En primer lugar, la PWRT de tiempo de

espera se invoca después de un retardo de tiempo

POR ha expirado. Entonces, el Oscilador Start-up

Timer (OST) se invoca. Sin embargo, esto todavía no

es una cantidad de tiempo suficiente para permitir que

el PLL para bloquear a altas frecuencias. El

temporizador PWRT se utiliza para proporcionar un

adicional fijo 2 ms (nominal) de tiempo de espera para

permitir que el PLL tiempo suficiente para bloquear la

frecuencia de reloj entrante.

2006 Microchip Technology Inc. DS39564C páginas 27

PIC18FXX2

DeteConnecticut Power-on Res

Brown Salida Reset

BORES

30.0 de RESET

El PIC18FXXX distingue entre varios tipos de RESET:

un) Power-on Reset (POR)

b) MCLR Restauración durante la

operación normal c) Reset MCLR durante

el sueño

dWatchdog) Timer (WDT) Reset (durante el

funcionamiento normal)

e) Programable Brown-out Reset (BOR)

f) REINICIO

Instrucción g) Tubo de

escape de Reposición

Total

h) Pila Cambiar Underflow

Mosregistros T no se ven afectados por un RESET.

Su estado es desconocido en POR e inalterada de

todas las restauraciones otro. Los otros registros se

ven obligados a un "estado RESET" en Power-on

Reset, MCLR, Reset WDT, Brown-out Reset, reinicio

MCLR durante el sueño y por la REINICIO

instrucción.

Mosregistros T no se ven afectados por un WDT-

despertador, ya que este es visto como la

reanudación de la normalidad el funcionamiento. Bits

de estado del registro RCON, RI, TO, PD, POR y

BOR, se activa o se desactiva de manera diferente en

diferentes situaciones de RESET, según se indica en

la Tabla 3-2. Estos bits se utilizan en software para

determinar el tipo de RESET. Consulte la tabla 3-3

para obtener una descripción completa de los estados

de RESET de todos los registros.

Un diagrama de bloques simplificado del circuito de

reset on-chip se muestra en la Figura 3-1.

Thelectrónicos mejorados dispositivos MCU tienen un

filtro de ruido MCLR en el trayecto Cambiar MCLR. El

filtro detectar e ignorar pequeños pulsos.

The MCLR pin no se conduce bajo cualquier interno

RESTABLECIMIENTOS, incluyendo el WDT.

FIGURA 3-1: diagrama de bloques simplificado del circuito de rearme ON-CHIP

REINI

CIO Entrucción

Stack

PointePila r completo / Restaurar Underflow

ECambiar Xternal

MCLR

WDT

WDT

SLEEP

VDD

Módulo

Rise VDD

Tiempo muerto Reestablecer

et

S

OSC1

OST / PWRT

OST

10-bit contador de rizado

Chip_Reset

R Q

El chip RC OSC(1)

PWRT

10-bit contador de rizado

Habilitar PWRT

Act vace

OST(2)

DS39564C-page28 2006 Microchip Technology Inc.

PIC18FXX2

Noe 1: This es un oscilador separado del oscilador RC del pasador CLKI.

2:See la Tabla 3-1 para las situaciones de tiempo de espera.

2006 Microchip Technology Inc. DS39564C páginas 29

PIC18FXX2

3.1 Power-On Reset (POR)

A Power-on reset pulso se genera en el chip cuando

se detecta aumento VDD. Para aprovechar las

ventajas del POR cir-cuitry, sólo empatar el pin MCLR

directamente (oa través de un resistor) a VDD. Esto

eliminará los componentes externos de RC por lo

general se necesitan para crear un retardo de

encendido Reset. Una tasa de incremento mínimo

para VDD se especifica (parámetro D004). Durante un

tiempo lento ascenso, ver Figura 3-2.

When el dispositivo inicia la operación normal (es

decir, sale de la condición RESET), los parámetros

operativos del dispositivo (de voltaje, frecuencia,

temperatura, etc) deben cumplirse para asegurar la

operación. Si estas condiciones no se cumplen, el

dispositivo debe realizarse en RESET hasta que las

condiciones de funcionamiento se cumplen.

FIGURA 3-2: POWER-ON Circuito exterior

RESET (DE VDD LENTO

ENCENDIDO)

VDD

D R

R1 MCLR

CPIC18FXXX

Noe 1: External encendido Circuito de rearme sólo es

necesario si el VDD encendido pendiente es

demasiado lento. El diodo D ayuda a

descargar el condensador rápidamente

cuando los poderes VDD hacia abajo.

2:R <40 kΩ yos recomendado para asegurarse

de que la caída de voltaje a través de R no

viola las especificaciones eléctricas del

dispositivo.

3:R1 = 100Ω a 1 kΩ will limitar cualquier

corriente de flujo-ción en MCLR del

condensador C externo, en caso de MCLR /

VPP pin ruptura debido a descargas

electrostáticas (ESD) o sobretensión

eléctrica (EOS).

3.2 Power-up Timer (PWRT)

The Power-up Timer proporciona un valor nominal fijo

de tiempo de espera (parámetro 33) sólo en el

arranque del POR. El temporizador de encendido

funciona con un oscilador interno RC. El chip se

mantiene en RESET mientras el PWRT está activo. El

retardo de tiempo permite PWRT VDD para alcanzar

un nivel aceptable. Un bit de configuración se

proporciona para habilitar / deshabilitar la PWRT.

The power-up de retardo de tiempo variará de viruta a

viruta debido a VDD, la temperatura y la variación del

proceso. Ver D033 DC parámetros para obtener más

información.

DS39564C-page30 2006 Microchip Technology Inc.

PIC18FXX2

3.3 Oscilador Start-up Timer (OST)

ThOscilador electrónico Start-up Timer (OST) ofrece

un ciclo de oscilador de 1024 (a partir de la entrada

OSC1) Retardo tras el retraso es de más PWRT

(parámetro 32). Esto asegura que el oscilador de

cristal o resonador se ha iniciado y estabilizado.

The OST de tiempo de espera se invoca sólo para XT,

LP y los modos del SA, y sólo en Power-on Reset o

despertar de su sueño-.

3.4 PLL Time Lock-out

Ingenioh el PLL activado, la secuencia de tiempo de

espera después de un Power-on Reset es diferente

de otros modos de oscilador. Una porción del

temporizador de encendido se utiliza para pro-vide un

fijo de tiempo de espera que sea suficiente para el

PLL para bloquear la frecuencia del oscilador

principal. Este bloqueo de PLL de tiempo de espera

(TPLL) es típicamente de 2 ms y sigue el oscilador de

tiempo de inicio de salida (OST).

3.5 Brown-out Reset (BOR)

Un poco de configuración, Boren, puede desactivar (si

claro / programada) o habilitar (si está ajustado) el

circuito de reset Brown-out. Si VDD cae por debajo

del parámetro D005 para mayor que el parámetro 35,

la situación brown-out se restablecerá el chip. Un

RESET no se puede producir si VDD cae por debajo

de parámetro D005 por menos de parámetro 35. El

chip se mantendrá en Brown-out Reset hasta que se

eleva por encima de VDD BVDD. Si el temporizador

de encendido está activado, se invoca después se

eleva por encima de VDD BVDD, entonces será

mantener el chip en RESET durante un retardo

adicional (parámetro 33). Si VDD cae por debajo de

BVDD mientras el temporizador de encendido está

funcionando, el chip se regrese a un reinicio Brown-

out y el temporizador de encendido será inicializado.

Una vez que se eleva por encima de VDD BVDD, el

temporizador de encendido se ejecutará el retardo de

tiempo adicional.

3.6 Tiempo de espera de secuencia

On power-up, la secuencia de tiempo de espera es el

siguiente: En primer lugar, PWRT de tiempo de

espera se invoca después del retardo de tiempo POR

ha expirado. Entonces, se activa OST. El total de

tiempo de espera puede variar en función de la

configuración del oscilador y el estado de la PWRT.

Por ejemplo, en el modo de RC con el PWRT

desactivado, no habrá tiempo de espera en absoluto.

Figura 3-3 Figura 3-4 Figura, 3-5, Figura 3-6 y la

Figura 3-7 muestran las secuencias de tiempo de

espera en el encendido.

Since los tiempos de espera se producen a partir del

impulso POR, MCLR si se mantiene baja lo suficiente,

los tiempos de espera expira. Llevar MCLR alta

comenzará la ejecución inmediatamente (Figura 3-5).

Esto es útil para propósitos de prueba o para

sincronizar más de un dispositivo PIC18FXXX

operando en paralelo.

Tcapaz 3-2 muestra las condiciones de reinicio

durante algunos registros de funciones especiales,

mientras que la Tabla 3-3 se muestran las

condiciones de RESET para todos los registros.

2006 Microchip Technology Inc. DS39564C páginas 31

PIC18FXX2

Ososcilador

Configuración

(2) Brown-out

Despertar-Up de

suspensión o

interruptor

oscilador

PWRTE = 0

PWRTE = 1

HS con PLL

habilitado(1)

72 ms + 1024 TOSC

+ 2ms

1024 TOSC

+ 2 ms

72 ms(2) + 1024 TOSC

+ 2 ms

1024 TOSC + 2 ms

HS, XT, LP 72 ms + 1024 TOSC 1024 TOSC 72 ms(2) + 1024 TOSC 1024 TOSC

CE 72 ms - 72 ms(2) -

External RC 72 ms - 72 ms(2) -

TABLE 3-1: tiempo de espera en diferentes situaciones

Power-up

NoTE 1: 2 ms es el tiempo nominal necesario para el 4x PLL para bloquear.

2:72 ms es el valor nominal de encendido de retardo del temporizador, si se aplica.

REGISTRO 3-1: BITS RCON REGISTRO Y POSICIONES

R/W-0 U-0 U-0 R/W-1 R-1 R-1 R/W-0 R/W-0

IPEN - - Rhode Island

A PD POR BOR

bit 7 bit 0

Nota 1: Consulte la Sección 4.14 (página 53) para obtener definiciones de bit.

TABLE 3-2: BITS DE ESTADO, su significado y las condiciones de iniciación PARA REGISTRO

RCON

Condición Programa

Contador RCON

Registra

rse

Rhode Island

A

PD

POR

BOR

STKFUL

STKUNF

Power-on reset 0000h 0 a 1

1100 1 1 1 0 0 u u

MCLR Restablecer durante

el funcionamiento normal 0000h 0 - u

uuuu u u u u u u u

Restablecimiento de software

durante el funcionamiento

normal

0000h 0 a 0

uuuu 0 u u u u u u

Stack cero completa durante el

funcionamiento normal 0000h 0 - u

uu11 u u u u u u 1

Stack Cambiar Rebase

durante el funcionamiento

normal

0000h 0 - u

uu11 u u u u u 1 u

MCLR Restablecer durante el sueño

0000h 0 - u

10uu u 1 0 u u u u

WDT Restablecer 0000h 0 - u

01uu 1 0 1 u u u u

WDT Wake-up PC + 2 u - u

00uu u 0 0 u u u u

Brown-out reset 0000h 0 a 1

11u0 1 1 1 1 0 u u

Interrupción de despertar de un sueño

PC + 2(1) u - u

00uu u 1 0 u u u u

Leyenda:u= Sin cambios, x= Desconocido, - = bit sin aplicarse, leído como '0 '

Nota 1: When el despertador se debe a una interrupción y el GIEH o bits Giel se establece, el PC se carga

con el vector de interrupción (0x000008h or0x000018h).

DS39564C-page32 2006 Microchip Technology Inc.

PIC18FXX2

TABLE 3-3: CONDICIONES inicialización de todos los registros

Registro

Dispositivos aplicables

Power-on Reset,

reinicio Brown-

out

MRestablece CLR

WDT Restablecer REINICIO

Instrucción Stack

Restablece

DespertarEn

marcha a través de WDT

Interrumpir o Tosu 242 442 252 452 --- 0 0000 --- 0 0000 --- 0 uuuu(3)

TOSH 242 442 252 452 0000 0000 0000 0000 uuuu uuuu(3)

TOSL 242 442 252 452 0000 0000 0000 0000 uuuu uuuu(3)

STKPTR 242 442 252 452 00-0 0000 uu-0 0000 uu-u uuuu(3)

PCLATU 242 442 252 452 --- 0 0000 --- 0 0000 --- U uuuu

PCLATH 242 442 252 452 0000 0000 0000 0000 uuuu uuuu

PCL 242 442 252 452 0000 0000 0000 0000 PC + 2(2)

TBLPTRU 242 442 252 452 - 00 0000 - 00 0000 - Uu uuuu

TBLPTRH 242 442 252 452 0000 0000 0000 0000 uuuu uuuu

TBLPTRL 242 442 252 452 0000 0000 0000 0000 uuuu uuuu

TABLAT 242 442 252 452 0000 0000 0000 0000 uuuu uuuu

PRODH 242 442 252 452 xxxx xxxx uuuu uuuu uuuu uuuu

Prödl 242 442 252 452 xxxx xxxx uuuu uuuu uuuu uuuu

YoNTCON 242 442 252 452 0000 000X 0000 000U uuuu uuuu(1)

INTCON2 242 442 252 452 -1-1 1111 -1-1 1111 uuuu-u-u(1)

INTCON3 242 442 252 452 11-0 0-00 11-0 0-00 uu-u u-uu(1)

INDF0 242 442 252 452 N / A

N / A

N / A POSTINC0 242 442 252 452 N /

A N / A

N / A POSTDEC0 242 442 252 452 N /

A N / A

N / A PREINC0 242 442 252 452 N /

A N / A

N / A PLUSW0 242 442 252 452 N /

A N / A

N / A FSR0H 242 442 252 452 ---- Xxxx ---- Uuuu ---- Uuuu

FSR0L 242 442 252 452 xxxx xxxx uuuu uuuu uuuu uuuu

WREG 242 442 252 452 xxxx xxxx uuuu uuuu uuuu uuuu

INDF1 242 442 252 452 N / A

N / A

N / A POSTINC1 242 442 252 452 N /

A N / A

N / A POSTDEC1 242 442 252 452 N /

A N / A

N / A PREINC1 242 442 252 452 N /

A N / A

N / A PLUSW1 242 442 252 452 N /

A N / A

N / A Leyenda:u= Sin cambios, x= Desconocido, -= Bit sin aplicarse, leído como '0 ', q= Valor depende de la condición.

Sombracélulas D indican condiciones no se aplican para el dispositivo designado.

Nota 1: Ene o más bits en los registros INTCONx o Pirx se verá afectada (causar despertar).

2:When el despertador se debe a una interrupción y el bit GIEL o GIEH está establecida, el PC se carga con

el vector de interrupción (0008h or0018h).

3:Wuando el despertador se debe a una interrupción y el bit GIEL o GIEH está establecida, el Tosu, Tosh y TOSL son

actualizard con el valor actual de la PC. El STKPTR se modifica para apuntar a la siguiente

ubicación en la pila de hardware.

4:Consulte la Tabla 3-2 para obtener valor de restablecimiento de la condición específica.

5:Bit 6 de PORTA, LATA, TRISA y están habilitados en ECIO y modos de Comércio oscilador solamente. En

todos los demás

Oscilaciónmodos de Tor, que sean discapacitados y '0 '.