AHDL

-

Upload

ivonne-diaz -

Category

Documents

-

view

16 -

download

1

Transcript of AHDL

Copyright© Guillermo Jaquenod,1999

Lenguajes de descripciónde Hardware I

Una breve visión sobrelos HDLs en general y

AHDL en particular

Copyright© Guillermo Jaquenod,1999

Discretos vs. continuos

IMPORTANTE!

Existen lenguajes de descripción de hardwarepensados para el diseño de sistemas continuos

(analógicos), y otros concebidos para trabajar con sistemas discretos (usualmente binarios)

Este curso trata sobre lenguajes de descripciónde hardware de sistemas discretos

Copyright© Guillermo Jaquenod,1999

Qué es un HDL?

• Un lenguaje HDL para descripción de hardware (HDL: Hardware

Description Language) es una herramienta formal para describir

el comportamiento y la estructura de sistemas (usualmente

electrónicos pero a veces también de otros tipos) usando un

esquema textual

• Usando HDL el diseñador puede describir la operación del

sistema con diferentes niveles de abstracción (o “estilos”):

– describiendo QUÉ es lo que el sistema debe hacer

(comportamiento)

– describiendo CÓMO hacerlo (algorítmico)

– detallando CON QUÉ hacerlo (flujo de datos y estructural)

Copyright© Guillermo Jaquenod,1999

Características de un HDL

• Describe actividades que ocurren en forma simultánea

(CONCURRENCIA)

• Permite describir módulos con acciones que serán evaluadas en

forma secuencial (procedural), donde todo el módulo será visto

como una acción concurrente más

• Posibilita la construcción de una estructura jerárquica, donde es

posible combinar descripciones estructurales y de flujo de datos

con descripciones de comportamiento (BEHAVIOR)

• Permite modelizar el concepto de “tiempo”, fundamental para la

descripción de sistemas electrónicos

Copyright© Guillermo Jaquenod,1999

Que ventajas da el uso de HDLs?

• Como herramienta de especificación

– es posible su uso para la de especificación general de unsistema, tanto a nivel de hardware como de software

– permite describir el hardware, tanto a nivel de sistemas ysubsistemas, como de componentes

• Como herramienta de diseño

– Mejor documentación y facilidad de reuso

– Posibilidad de parametrización

– Portabilidad de un diseño. Independencia tecnológica

• Como herramienta de simulación

– Disponibilidad de modelos de distintos componentes defabricantes variados en HDLs normalizados

– Facilidad para la generación de vectores de test complejos

Copyright© Guillermo Jaquenod,1999

Dónde es posible usar HDL?

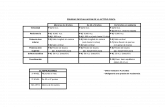

ESPECIFICACIÓN DEL SISTEMA

PARTICIÓN HARDWARE/SOFTWARE

ESPECIFICACIÓNDE SOFTWARE

SOFTWAREPLD

PartesEstándar

ASIC

PLAQUETAS

Y

SISTEMAS

ESPECIFICACIÓNDE HARDWARE

FPGA

DISEÑO

ESPECIFICACIÓN

Copyright© Guillermo Jaquenod,1999

Qué es un estilo de “descripción de hardware”?

Es la manera en que el diseñador describe el sistema. Puede ser:

– Comportamiento (Behavioral): detalla la función entrada-salida

del diseño, sin profundizar la arquitectura o los registros empleados

– Algoritmico: detalla las acciones a realizar para alcanzar los

objetivos, a modo de un algoritmo de software

– Flujo de datos a nivel de registros: describe la solución en forma

de una máquina secuencial, detallando los registros y la lógica que

los une, sin incluir cómo resolver esa lógica. Es una descripción de

la arquitectura del sistema, pero no de la tecnología

– Estructural, a nivel de registros: describe una red de compuertas

y registros, incorporando posibles esquemas de conexión

Copyright© Guillermo Jaquenod,1999

Niveles de abstraccion versusdominios de descripcion

Dominio de descripcion Comportamiento Estructural Fisico

Especificaciones CPUs, memorias ParticionPerformance switches, buses fisica

Algoritmos de manejo Modulos de Hardware Clustersde estructuras de Estructuras de datosdatos

Operaciones a nivel de ALUs, multiplexores Cableadoregistros RegistrosSecuencias de estado Microsecuenciadores

Ecuaciones booleanas Compuertas, flipflops Celdas logicas

Niv

el d

e ab

stra

ccio

n

Logi

co F

unci

onal

Alg

oritm

ico

Arq

uite

ctur

al

Copyright© Guillermo Jaquenod,1999

Qué HDLs existen?

• De bajo nivel: permiten definir un circuito a nivel de arquitectura(FlipFlops, compuertas básicas, ecuaciones lógicas)

– PALASM, CUPL, ABEL• De nivel medio: superset de los previos, permiten definir un circuito

en modo jerárquico, así como la generación condicional/iterativa dehardware; en ciertos permiten el uso de descripciones decomportamiento (funciones aritméticas, máquinas de estado).

– AHDL• De alto nivel: superset de los previos, no sólo posibilitan mayor nivel

de abstracción, sino que también son usados para la simulación,para la síntesis del generador de estímulos y el monitor de salidas

– VHDL, VERILOG HDL

Copyright© Guillermo Jaquenod,1999

Estructura jerárquica

diseño de jerarquía tope

subdiseño 1

subdiseño 4

subdiseño 3subdiseño 2

..... ...............

subdiseño tope

Copyright© Guillermo Jaquenod,1999

módulo full_adder...instancia de half_adder...instancia de half_adder....

Diseño jerárquico

• El diseño jerárquico permite– descomponer un sistema complejo en subsistemas, y asignar

el diseño de cada subsistema a una persona diferente

– generar sudiseños reutilizables

– posibilidad de usar diseños realizados por terceros (IP:Intellectual Property)

módulo half_adder.....

full_adder

halfadder

halfadder

OR

Copyright© Guillermo Jaquenod,1999

Instancias y Jerarquías

• Como elementos constructivos de sucomportamiento, un módulo puede incluirdentro de sí bloques de menor nivel (otrosmódulos) definidos separadamente, los queserán usados a través de sus puertas,excitando sus entradas y utilizando losvalores que aparezcan en sus salidas

• La inclusión de un módulo dentro de otro demayor nivel se llama crear una INSTANCIAde ese módulo

• Esta facilidad permite generar estructurasjerárquicas sin restricciones de anidamiento,así como el reuso de subdiseños

modulo A

otra instancia del módulo B

instancia del módulo C

módulo B

módulo C

instancia delmódulo B

Copyright© Guillermo Jaquenod,1999

Encapsulamiento de módulos

• La interfase de un módulo con losdemás se realiza mediante puertas,que pueden ser de entrada, desalida, o bidireccionales, y estainterfase es la única parte visible delmódulo por el resto del diseño

• El comportamiento interno de unmódulo puede ser definido mediantediferentes estilos, y sólo puede serobservado desde el exterior delmódulo por los efectos que provocaen la interfase

• Este tipo de operación permite elencapsulamiento del diseño

COMPORTAMIENTOINTERNO

INTERFASE

PUERTAS

Copyright© Guillermo Jaquenod,1999

Ejemplo elemental en AHDL

• el campo subdesign define elnombre del módulo y las puertas através de las cuales el mundoexterior ve al bloque funcional

• el campo lógico (BEGIN..END)define el comportamiento internodel bloque

-- nombre del bloque-- y de sus puertas

SUBDESIGN ejemplo_1 ( a,b,e : INPUT; c,d : OUTPUT;)

-- descripción del-- comportamiento

BEGIN c = a & b; d = e; END;

AND

ejemplo_1

a

bc

de

Copyright© Guillermo Jaquenod,1999

Ese ejemplo en VHDL

• Se define separadamente elcomportamiento desde elpunto de vista externo(ENTITY) a la realizacióninterna (ARCHITECTURE)

• Es posible definir distintasarquitecturas de un mismobloque funcional

-- descripcion del nombre y-- las puertasENTITY ejemplo_1 IS PORT ( a, b, e : IN BIT; c, d : OUT BIT; );END ejemplo1;

--y del comportamientoARCHITECTURE comporta OF ejemplo_1 ISBEGIN c <= a AND b; d <= e;END comporta;

AND

ejemplo_1

a

bc

de

Copyright© Guillermo Jaquenod,1999

AHDLALTERA Hardware

Description Language

Copyright© Guillermo Jaquenod,1999

Lenguaje de descripción deHardware ALTERA

• AHDL permite la descripción del hardware a través de sucomportamiento (behavior), en lugar de hacerlo a través de uncircuito esquemático

• Usa ecuaciones lógicas, variables, constantes, funciones,operadores aritméticos, tablas de verdad, y expresionescondicionales, en forma similar a la de un lenguaje de software dealto nivel.

• Está especialmente orientado para definir máquinas de estado degran complejidad

• Toda la descripción del comportamiento es resuelta en formaconcurrente

• Facilita el diseño mediante el uso de plantillas• Soporta todas las familias de ALTERA

Copyright© Guillermo Jaquenod,1999

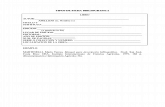

Flujo de diseño mediante AHDL yel MAX+PLUS II

Editor deformas de ondaMAX+PLUS II

Compiladorfuncional o

fisico

Simulador

Archivo .tdf

Estimulos:.scf

Archivo .snf

Funciona OK?

Editor de textode AHDL

MAX+PLUS II

Editor detexto

Estimulos:.vec

no

MAX+PLUS II

Copyright© Guillermo Jaquenod,1999

AHDL: seccionesde un archivo .tdf

• Título (opcional)• Include (opcional)• Constant (opcional)• Define (opcional)• Parameters (opcional)• Function prototype (opcional)• Options(opcional)• Assert (opcional)• Subdesign (necesario)• Variable (opcional). Puede contener:

– Declaraciones: Instancias, Nodos, Registros y Máquinasde estado

• Logic (necesario). Puede contener:– Construcciones: Default, Assert, , Case, For_Generate,

If_Generate, If_Then, y Tablas de verdad– Ecuaciones: lógicas y de control– Referencias: a funciones In_Line

TITULOINCLUDE

CONSTANT

DEFINEPARAMETERS

PROTOTYPEOPTIONS

ASSERTSUBDESIGN

VARIABLE

LOGIC

opcionalobligatoria

Copyright© Guillermo Jaquenod,1999

AHDL: la sección TITULO

• Es un campo opcional, único, que noafecta a la descripción del hardware

• Permite incorporar comentarios queluego serán incorporados al reporte decompilación

• Importante a los fines de ladocumentación del diseño

TITULO

La sintaxis es:

TITLE “nombre del diseño”;

keyword TITLE

comentarios,entre comillas

terminación

Copyright© Guillermo Jaquenod,1999

AHDL: la sección INCLUDE

• Es un campo opcional, múltiple

• Permite importar texto desde otrosarchivos escritos en AHDL (cuya extensiónpor defecto es .inc) al corriente diseñopara la compilación

• Usualmente usado para incluir prototiposde funciones de menor nivelLa sintaxis es:

INCLUDE “archivo.inc”;

keyword INCLUDEnombre del archivo a importar

TITULO

INCLUDE

terminación

Copyright© Guillermo Jaquenod,1999

AHDL: la sección CONSTANT

• Es un campo opcional, múltiple• Permite definir un nombre simbólico y

asociarlo a un valor constante.• Posteriores usos del nombre serán

reemplazados por el valor constantedurante la compilación

La sintaxis es:

CONSTANT nombre = valor ;

keyword CONSTANTnombre de la constante

TITULO

INCLUDE

CONSTANT

valor constante

Copyright© Guillermo Jaquenod,1999

AHDL: la sección PARAMETERS

• Es un campo opcional, múltiple

• Permite declarar parámetros que controlan laimplementación de una megafunción omacrofunción parametrizada

• Los parámetros pueden ser nombres definidospor el usuario, o por ALTERA

• Un parámetro puede ser usado sólo luego deser declarado

• No se permiten referencias cruzadas

• En la declaración se puede asignar a losparámetros valores por default

• El compilador busca el valor del parámetrodesde la instancia de la función hasta el niveltope. Se sigue luego por los valores de default.

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERS

Copyright© Guillermo Jaquenod,1999

AHDL: la sección PARAMETERS

• Ejemplo de una sección PARAMETERS:

valores pordefault

PARAMETERS ( NOMBRE = “pedro”, ANCHO, AD_ANCHO = 8, NUMPALA = 2^AD_ANCHO );

keyword PARAMETERSnombre de losparámetros

AD_ANCHO puede ser usado puesya fué definido en la línea anterior

Copyright© Guillermo Jaquenod,1999

AHDL: la sección FUNCTIONPROTOTYPE

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERS

PROTOTYPE

• El prototipo es la descripción de unafunción, compuesta por:– nombre de la función– entradas– parámetros– salidas y puertas bidireccionales

FUNCTION nombrefunción (ent1,..,entK)

WITH (param1,param2,..,paramL)

RETURNS (sal1,..,salM,bidi1,..,bidiN);

keywords FUNCTION

WITH, yRETURNS

nombre de la función lista de entradaslista deparámetros

lista de salidas y puertas bidireccionales

Copyright© Guillermo Jaquenod,1999

AHDL: la sección SUBDESIGN

• SUBDESIGN declara tipo y nombrede las puertas de un diseño .tdf

• Comienza con SUBDESIGN seguidopor el nombre del diseño, que debeser el mismo que el del archivo .tdf

• el tipo básico de las puertas puedeser INPUT, OUTPUT, y BIDIR.

• se puede usar MACHINE INPUT yMACHINE OUTPUT para importar yexportar máquinas de estado

• Es posible asignar un valor pordefault de GND o VCC para lasentradas en caso que no seanusadas en un nivel superior

SUBDESIGN mi_diseño ( en1,clk1: INPUT = VCC; a[4..0]: OUTPUT; dual: BIDIR; )

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERSPROTOTYPE

OPTIONSASSERT

SUBDESIGN

Copyright© Guillermo Jaquenod,1999

AHDL: la sección VARIABLE

• en esta sección se declaran lasvariables usadas en la sección LOGICpara definir lógica interna (o buried)

• Puede incluir las siguientesconstrucciones:– Declaración de nodos– Declaración de registros– Declaración de instancias de

funciones– Declaración de Máquinas de estado– Asignación de ALIAS a Máquinas

de estado

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERSPROTOTYPE

OPTIONSASSERT

SUBDESIGN

VARIABLE

Copyright© Guillermo Jaquenod,1999

AHDL: la sección VARIABLE

• La palabra clave VARIABLE indica el inicio de esta sección

• Un conjunto de variables de igual tipo puede definirse:

– mediante la lista de nombres simbólicos, separados porcomas.

– dos puntos, y el tipo de variable

– punto y coma, como terminación

• Donde el tipo de puede ser:

– <primitiva>, NODE, TRI_STATE_NODE,<megafunción>, <macrofunción>, o <declaración demáquina de estado>

Copyright© Guillermo Jaquenod,1999

AHDL: la sección VARIABLE

Ejemplo de una sección VARIABLE

VARIABLE a,b,c : NODE; temp : halfadd; tsnodo: TRI_STATE_NODE; adder : lpm_add_sub WITH (LPM_WIDTH=8);

keyword VARIABLE: inicio de la sección

listas de nombres simbólicos

tipos básicosde nodos

instancia de unamacrofunción(half adder)

instancia de una megafunción(lpm_add_sub) con unparámetro (LPM_WIDTH)

Copyright© Guillermo Jaquenod,1999

la sección VARIABLE: instancias

Declarar una instancia de una función significa asignarrecursos específicos de hardware para realizar esafunciónPor ejemplo, dada una función “comparar”, con prototipo:

FUNCTION comparar (a[3..0],b[3..0]) RETURNS (igual);

el poner en la sección VARIABLE la instancia

VARIABLE mi_comp : comparar;

define los nodos mi_comp.a[..], mi_comp.b[..] y mi_comp.igual

Copyright© Guillermo Jaquenod,1999

La sección VARIABLE: los buffers

Buffers:– CARRY: conexión mediante el uso de la cadena de CARRY– CASCADE: conexión mediante el uso de la cadena de CASCADE– EXP: término que determina el uso de un expansor– GLOBAL: indica que una señal debe usar una línea global de Clock,

Clear, Preset, o Output Enable (todas las familias)– LCELL: fuerza que la señal a la que se asigne sea la salida de una

celda lógica, y que no sea removida por el compilador durante laminimización

– SOFT: propone un lugar para una celda lógica, de ser ésta requerida.Puede ser removido por el compilador durante la minimización

– TRI: buffer TRI_STATE (Ej: FUNCTION TRI (in,oe) RETURNS (out);)– OPNDRN: equivale a TRI con in==GND

Copyright© Guillermo Jaquenod,1999

La sección VARIABLE: los registros

• AHDL ofrece primitivas para definir los siguientes tipos deregistros:– flipflops:

• D: DFF y DFFE (con clock Enable)• T: TFF y TFFE• JK: JKFF y JKFFE• SR: SRFF y SRFFE

– latches: LATCH• Por ejemplo, el prototipo de un flipflop D es:

– FUNCTION DFF (d,clk,clrn,prn) RETURNS (q);• Si en la sección VARIABLE se declara: mi_ff : DFF; en la

sección de lógica se podrán utilizar las entradas mi_ff.d, mi_ff.clk, mi_ff.clrn, mi_ff.prn y la salida mi_ff.q

Copyright© Guillermo Jaquenod,1999

la sección VARIABLE: los nodos

• AHDL acepta dos tipos de nodos: NODE yTRI_STATE_NODE

• son variables locales similares a las variables globalesINPUT, OUTPUT o BIDIR declaradas en la secciónSUBDESIGN, en cuanto representan una línea quetransporta una señal.

• un nodo de tipo NODE con múltiples asignaciones juntalas señales mediante funciones wired-AND o wired-OR,según los defaults sean VCC o GND, respectivamente.

• un nodo de tipo TRI_STATE_NODE con múltiplesasignaciones junta las señales directamente entre sí. Unnodo de este tipo con una única asignación es tratadocomo un nodo tipo NODE

Copyright© Guillermo Jaquenod,1999

la sección VARIABLE: los nodos

Ejemplo elemental de diseño con especificaciónde nodos :

SUBDESIGN node_ex( a, oe : INPUT ;

out : OUTPUT ;c : BIDIR ; )

VARIABLE b: NODE ; t: TRI_STATE_NODE ;BEGIN b = a ; out = b ; t = TRI (a, oe) ; c = t ;END ;

a out

oe

ct

node_ex

b

FUNCTION node_ex (a,oe) RETURNS (c,out);

Copyright© Guillermo Jaquenod,1999

declaración de máquinas de estado

• Se puede crear una máquina de estados declarando sunombre, sus estados, y opcionalmente sus bits

• La declaración se compone de:

– el nombre simbólico, seguido de (:) y la palabra claveMACHINE

– (opcional) el nombre de los bits de estado, con la frase claveOF BITS (..)

– la lista de estados, compuesta por la frase clave WITHSTATES (..) con la enumeración de los nombres simbólicosde los estados, separados por comas, con susasignaciones opcionales.

Copyright© Guillermo Jaquenod,1999

declaración de máquinas de estado

• Ejemplo:VARIABLE me : MACHINE WITH STATES (e1,e2,e3);

nombre dela máquina

estados:e1,e2 y e3

se fuerza a que use tres bits q1, q2, q3 (opcional)

se fija el valor de los bits para cadauno de los estados(op[cional)

el primer estadoes el de RESET

VARIABLE me : MACHINE OF BITS (q1,q2,q3) WITH STATES ( e1 = B”000”, e2 = B”010”, e3 = B”111”);

Copyright© Guillermo Jaquenod,1999

AHDL: la sección LOGIC

• Define las operaciones lógicas del.tdf

• Se encuadra entre las palabrasclave BEGIN y END;

• Se compone de– Ecuaciones: lógicas y de control– Expresiones: Case, If_Then,

Tablas de verdad, Default,If_Generate, y For_Generate

– Referencias: a funcionesIn_Line

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERSPROTOTYPE

OPTIONSASSERT

SUBDESIGNVARIABLE

LOGIC

Copyright© Guillermo Jaquenod,1999

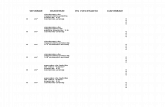

La sección LOGIC: operadores

Operadores

+-!^

MODDIV

*LOG2

+-

==!=>>=<<=

& o AND!& o NAND

$ o XOR!$ o XNOR

# u OR!# o NOR

?

Ejemplo

+1-1!a

a ^ 24 MOD 24 DIV 2

a * 2LOG2(4-3)

1+12-1

5 == 55 != 45 > 4

5 >= 5a < b+2

a <= b+2a & b1 !& 01 $ 11 !$ 1a # ba !# b

(5<4)?3:4

Descripción

+ unario- unario

NOT lógicoexponente

módulodivisiónproducto

log.base 2sumaresta

igualdaddesigualdad

mayormayor o igual

menormenor o igual

ANDAND negadaOR exclusivoXOR negadoOR inclusivoOR negado

IF compacto

Prioridad

11112222334444445566778

• La sección lógica evalúaexpresiones, usandooperadores y reglas deprecedencia.

• La expresiones pueden serlógicas y aritméticas.

Copyright© Guillermo Jaquenod,1999

Sección LOGIC: ecuaciones lógicas

Ejemplo de un diseño simple usando ecuaciones lógicasBooleanas

SUBDESIGN boole1 ( a0, a1, a2 : INPUT; out1, out2 : OUTPUT;)BEGIN out1 = a1 & !a0; out2 = out1 # a2; END;

boole1

AND

OR

a0

a1

a2

out1

out2

boole1

FUNCTION boole1 (a0,a1,a2) RETURNS (out1,out2);

Copyright© Guillermo Jaquenod,1999

Sección LOGIC: ecuaciones lógicas

Ejemplo de una ecuación lógica compleja

a[ ] = ((c[ ] & -B”001101”) + e[6..1]) # (p,q,r,s,t,v);

equivale a c[ ] & B”110011“es el grupo (c[6]&1,c[5]&1,c[4]&0,c[3]&0,c[2]&1,c[1]&1)minimiza a (c[6],c[5],0,0,c[2],c[1])

estos dos grupos se suman de formanumérica, mediante adders

entre estos dos grupos se hace el OR, bit a bit

c[6] c[5] 0 0 c[2] c[1]e[6] e[5] e[4] e[3] e[2] e[1] ... ... ... ... ... ...

+

Copyright© Guillermo Jaquenod,1999

Sección LOGIC: ecuaciones lógicas

a[ ] = ((c[ ] & -B”001101”) + e[6..1]) # (p,q,r,s,t,v);

a[6] a[5] a[4] a[3] a[2] a[1]

OR

HAFAHAHAFAFA

OR OR OR OROR

pqrstv

c[6] c[5] c[2] c[1] e[6] e[5] e[4] e[3] e[2] e[1]

Copyright© Guillermo Jaquenod,1999

La sección LOGIC: la sentencia CASE

CASE f[ ].q IS

WHEN H”00” =>

f[ ].d = 0;

WHEN H”01” =>

f[ ].d = count[ ].q+1;

WHEN H”02”, H”03”, H”04” =>

f[].d = addr[];

WHEN OTHERS =>

f[ ].d = f[ ].q;

END CASE;fin de lasentencia CASE

expresiones a activar si la expresióncoincide

expresiones a activarsi ninguna coincide

expresióna evaluar

condicionesCONSTANTES!cuya exclusiónpuede serverificada en lacompilación

inicio de lasentencia CASE

Copyright© Guillermo Jaquenod,1999

La sección LOGIC:la construcción IF..THEN

Permite definir una relaciónsalidas=f(entradas)parecida a CASESu forma general es como ladel ejemplo: condiciones

VARIABLESa evaluar enhardware

expresionesde activacióncondicional

IF a[ ] == b[ ] THEN

f[ ].d = addr[ ] + 1;

ELSIF g3 $ g4 THEN

f[ ].d = addr[ ];

ELSE d = VCC;END IF;

Copyright© Guillermo Jaquenod,1999

IF..THEN versus CASE

• CASE evalúa una única expresión y luego detecta su coincidenciacon expresiones constantes cuyo carácter excluyente entre sípuede ser verificado por software en la compilación

• IF..THEN evalúa varias expresiones en las sentencias IF.. yELSIF.., donde la posible validez de varias expresiones fuerza aque el compilador genere hardware para impedirlo

• Use CASE en lugar de IF..THEN siempre que le sea posible!!!Si la construcción dice

IF a THEN c=d;ELSIF b THEN c=e;ELSE c=f;END IF:

El compilador lo traduce a:

IF a THEN c=d; END IF; IF !a & b THEN c=e; END IF; IF !a & !b THEN c=f; END IF;

Copyright© Guillermo Jaquenod,1999

más sobre IF..THEN

• Lo parecido:– Una construcción IF..THEN..ELSE en software genera código

tanto para analizar las distintas condiciones como para laejecución de las sentencias.

– De igual modo, una construcción IF..THEN..ELSE en AHDLgenera hardware tanto para analizar las distintas condicionescomo para la ejecución de las sentencias.

• Lo diferente:– El carácter secuencial del software hace que al analizar la

validez de la condición de un ELSIF esté implícito la invalidezde las condiciones de las sentencias IF y ELSIF previas.

– La operación en paralelo del hardware hace que estapresunción no valga.

HARDWARE versus SOFTWARE

Copyright© Guillermo Jaquenod,1999

Sección LOGIC: tablas de verdad

• Usadas para especificar lógica combinacional en general y tablas detransiciones en máquinas de estado

• La primera línea indica el orden de las variables, y las líneas siguientesindican la correspondencia de valores

SUBDESIGN cod_prioridad ( menor, medio, mayor : INPUT; priori[1..0] : OUTPUT; )BEGIN TABLE mayor, medio, menor => priori[ ]; 1 , X , X => 3; 0 , 1 , X => 2; 0 , 0 , 1 => 1; 0 , 0 , 0 => 0; END TABLE;END;

tabla de verdadcombinatoria.Permite el uso detérminos “don’t care”!

mayormediomenor

priori

FUNCTION cod_prioridad (menor,medio,mayor) RETURNS (priori[1..0]);

Copyright© Guillermo Jaquenod,1999

Maquinas de estado tipo Mealy y tipo Moore

memoria

E(k+1)=EF=f(ent{},EA)

reloj

E(k)=EA

ent{}

Bloquecombinatorio

SAL{} = g(E(k))

SAL{} = g(E(k),ent{})

MEALY

MOORE

Copyright© Guillermo Jaquenod,1999

SUBDESIGN digilock (clk, reset, ent0, ent1 :INPUT; sali :OUTPUT;)

VARIABLE ss: MACHINE WITH STATES (s0,s1,s2,s3,s4);

BEGIN

ss.clk = clk; ss.reset = reset;

TABLE

ss, ent0, ent1 => sali, ss;

s0, X, X => 1, s1;

s1, X, X => 1, s3;

s2, 0, 0 => 1, s1;

s2, 1, 1 => 1, s1;

s2, 0, 1 => 1, s0;

s2, 1, 0 => 1, s3;

s3, X, X => 0, s4;

s4, X, X => 0, s2;

END TABLE;

END;

Tablas de verdad ymáquinas de estado

XX/0

S0

S1 S2

S3 S4

00/1

XX/0

01/1

10/1

11/1

XX/1

XX/1

digilocksali

ent0ent1resetclock

FUNCTION digilock(ent0,ent1,reset,clock) RETURNS (sali);

Copyright© Guillermo Jaquenod,1999

Maquinas de estado tipo Mealy

nMaquinas tipo Mealy: las salidas sonfuncion de las entradas y del estado actual

SUBDESIGN mealy( clk : INPUT; reset : INPUT; y : INPUT; z : OUTPUT;)VARIABLE ss: MACHINE WITH STATES (s0, s1,s2, s3);BEGIN ss.clk = clk; ss.reset = reset;

TABLE % estado entrada salida estado % % actual actual futura futuro % ss, y => z, ss;

s0, 0 => 0, s0; s0, 1 => 1, s1;

s1, 0 => 1, s1; s1, 1 => 0, s2; s2, 0 => 0, s2; s2, 1 => 1, s3; s3, 0 => 0, s3; s3, 1 => 1, s0; END TABLE;END;

Copyright© Guillermo Jaquenod,1999

Maquinas de estado tipo Moore

n Maquinas tipo Moore: las salidas sonfuncion solo del estado actual

SUBDESIGN moore( clk : INPUT; reset : INPUT; y : INPUT; z : OUTPUT;)VARIABLEss: MACHINE OF BITS(z) WITH STATES(s0=0, s1 = 1, s2 = 1, s3 = 0);BEGIN ss.clk = clk; ss.reset = reset;

TABLEss, y => ss;

s0, 0 => s0; s0, 1 => s2; s1, 0 => s0; s1, 1 => s2; s2, 0 => s2; s2, 1 => s3; s3, 0 => s3; s3, 1 => s1; END TABLE; TABLE

ss => z; s0 => GND;

s1 => VCC;s2 => VCC;s3 => GND;

END TABLE;END;

Copyright© Guillermo Jaquenod,1999

La sección LOGIC: IF..GENERATE

• Es una sentencia para controlar la compilación condicional dehardware

• Puede ser usada tanto en la sección LOGIC como en lasección VARIABLE

• Usa las keywords IF..GENERATE, ELSE GENERATE, ENDGENERATE;

IF DEVICE_FAMILY == ‘FLEX8K” GENERATE c[ ] = 8kadder (a[ ], b[ ], cin);ELSE GENERATE c[ ] = otroadder (a[ ], b[ ], cin);END GENERATE;

Copyright© Guillermo Jaquenod,1999

PARAMETERS N_ADDERS;SUBDESIGN suma_var ( a[N_ADDERS..1], b[N_ADDERS..1],cin: INPUT; c[N_ADDERS..1], cout : OUTPUT;)VARIABLE cy [(N_ADDERS+1)..1] : NODE;

BEGIN cy[1] = cin;

FOR i IN 1 TO N_ADDERS GENERATE c[i] = a[i] $ b[i] $ cy[i]; cy [i+1] = a[i]&b[i] # a[i]&cy[i] # b[i]&cy[i];END GENERATE;

cout = cy [N_ADDERS+1];END;

La sección LOGIC: FOR.GENERATE

n Es una sentencia decontrol de compilación utilpara especificar hardwareen forma parametrizada

n Usa las keywordsFOR..IN..TO..GENERATE,END GENERATE;

n Ejemplo: definir elhardware de un sumadoren base a una cascada defull-adders en formaparamétrica

ecuación deun full-adder

Copyright© Guillermo Jaquenod,1999

AHDL: mas secciones, lasmacrofunciones y las LPMs

• La seccion LOGIC: los DEFAULTS• La seccion ASSERT• La seccion DEFINE• El uso de macrofunciones y LPMs

Copyright© Guillermo Jaquenod,1999

La sección LOGIC: DEFAULTS

• Permite que el compilador sepaqué valor asignar a una variable siel programa deja este valor sindefinir

• Facilita la autodocumentación• Usa las keywords DEFAULTS y

END DEFAULTS• Sólo es posible una sentencia

DEFAULTS en la sección LOGIC• Ejemplo:

BEGIN

DEFAULTS no_a = VCC; END DEFAULTS;

IF y & z THEN no_a = GND; END IF;

END;

el estado inactivo de no_a sedefine como VCC ==> es unseñal activa baja

sólo es necesario especificarcuando no_a se activa

Copyright© Guillermo Jaquenod,1999

AHDL: la sección DEFINE

• Es un campo opcional, múltiple• Permite definir una función evaluable, que

devuelve un valor en base a susargumentos

• El compilador evalúa las expresiones ycalcula el valor numérico

• La expresión DEFINE no genera hardware• Ejemplo:

TITULO

INCLUDE

CONSTANT

DEFINE

argumentos

DEFINE MAX(a,b) = (a > b) ? a : b ;

keyword DEFINE nombre de la función

expresiónaritméticaa evaluar

Copyright© Guillermo Jaquenod,1999

AHDL: la sección ASSERT

• ASSERT permite testear la validez deuna expresión que use parámetros,números, funciones evaluables, o elestado de uso de una puerta

• ASSERT se activa si la expresión esfalsa o nula. En ese caso el mensaje quesigue al término REPORT es mostradopor el Message Processor

TITULOINCLUDE

CONSTANTDEFINE

PARAMETERSPROTOTYPE

OPTIONS

ASSERT

ASSERT (ANCHO > 0) REPORT “ANCHO (%) debe ser entero positivo” ANCHO SEVERITY ERROR;

Copyright© Guillermo Jaquenod,1999

AHDL y las macrofunciones

• Se denomina macrofuncion a un modulo de menor jerarquia,cuando este es empleado dentro de uno de mayor nivel

• El sistema MAX+PLUS II provee en forma estandar, a la manerade macrofunciones:

– Mas de 300 componentes de la familia TTL

– Algunas funciones propias de ALTERA

• Con ellos se dispone de soluciones para el diseno de Sumadores,Unidades Aritmetico Logicas (ALUs), Latches, Multiplicadores,Buffers, Multiplexadores, Comparadores, Generadores yverificadores de Paridad, Contadores, Registros, Codificadores yDecodificadores, Shift Registers, Filtros Digitales, Elementos dememoria, Circuitos para deteccion y correccion de errores,Funciones SSI, y algunos mas

Copyright© Guillermo Jaquenod,1999

Como se usa una macrofuncion?

El proceso de uso de una macrofuncion consta de tres etapas:

• Definicion: esta parte implica el ingreso del prototipo de la<funcion>, ya sea directamente o a traves de un archivo deINCLUDE. Esto permite que al instanciarse una variable de estetipo (ya sea en la seccion variable o por una referencia in_line) elcompilador sepa cuantas son, y cual es el nombre y tipo de laspuertas de la <funcion>.

• Instanciacion: al instanciar una variable declarandola como detipo <macrofuncion>, cuando se le asigna un <nombre>

• Referenciacion: al referenciar la variable <nombre>, las puertasde esta variable tendran similar nombre a las puertas de la<funcion>

Copyright© Guillermo Jaquenod,1999

Include “7483.inc”Include “7483.inc”

Ejemplo de uso de unamacrofuncion

VARIABLE misuma: 7483; ope1[3..0],ope2[3..0] : NODE; resulta[3..0], arrastre : NODE;

VARIABLE misuma: 7483; ope1[3..0],ope2[3..0] : NODE; resulta[3..0], arrastre : NODE;

…misuma.a[] = ope1[];misuma.b[] = ope2[];resulta[] = misuma.s[];arrastre = misuma.c4;….

…misuma.a[] = ope1[];misuma.b[] = ope2[];resulta[] = misuma.s[];arrastre = misuma.c4;….

Defino el prototipo de la funcion,siendo equivalente a haberescrito:FUNCTION 7483 (a[4..1], b[4..1], c0) RETURNS (s[4..1], c4);

Creo una instancia de sumador,llamada misuma, de tipo 7483

Actuo sobre las puertas de esainstancia, cuyo nombre se copiadel de las puertas del prototipo

Seccion VARIABLE

Seccion LOGICA

Seccion INCLUDE

Copyright© Guillermo Jaquenod,1999

AHDL y las LPMs

• LPM: Consorcio de fabricantes de software y de componentes– Bibliotecas completas y consistentes de Cadence, Intergraph,

Mentor Graphics, y Viewlogic support– Los fabricantes de componentes aseguran el uso eficiente de sus

recursos• Bloques constructivos genéricos y parametrizados

– Compuertas, FlipFlops,Sumador/Restador, Comparador,Contadores, Decodificadores, Latches, Multiplicadores,Multiplexadores, RAM/ROM, etc.

– Parametrizados. Por ejemplo LPM_COUNTER ( LPM_WIDTH=8,LPM_DIRECTION=Up, etc.)

• Biblioteca estándar– La familia TTL de la próxima etapa

Copyright© Guillermo Jaquenod,1999

Como se usa una LPM?

• Definicion: similar al uso de una macrofuncion, el prototipoindica no solo los nombres de las puertas, sino tambien el detodos los posibles parametros

• Instanciacion: al definir una variable usando LPMs, no solo secrea una variable de tipo <funcion>, con el <nombre> dado,sino que en ese momento tambien debe darse un cierto valor alos parametros. Si no se define este valor se asumira para elparametro su valor de default, y si no lo tuviera se dara un errorde compilacion

• Referenciacion: similar al caso de la macrofuncion, alreferenciar la variable <nombre>, las puertas de esta variabletendran el mismo nombre que las puertas de la <funcion>

Copyright© Guillermo Jaquenod,1999

Ejemplo de uso de una LPM

INCLUDE "lpm_add_sub.inc";

SUBDESIGN lpm_add2 ( a[8..1], b[8..1] : INPUT; c[8..1], carry_out : OUTPUT;)

VARIABLE 8bitadder : lpm_add_sub WITH (LPM_WIDTH=8, LPM_REPRESENTATION="unsigned");BEGIN 8bitadder.cin = GND 8bitadder.dataa[] = a[] 8bitadder.datab[] = b[] 8bitadder.add_sub = GND c[] = 8bitadder.result[] carry_out = 8bitadder.coutEND;

DEFINICION: este INCLUDE es equivalente

a haber ingresado lo siguiente:

FUNCTION lpm_add_sub (

dataa[LPM_WIDTH-1..0],

datab[LPM_WIDTH-1..0],

cin, add_sub, clock, aclr)

WITH (LPM_WIDTH,

LPM_REPRESENTATION,

LPM_DIRECTION, LPM_PIPELINE,

ONE_INPUT_IS_CONSTANT)

RETURNS

(result[LPM_WIDTH-1..0], cout, overflow);

INSTANCIACION: se define que sera de 8bits y sumara numeros sin signo

USO: se usa el nombre de la instancia conlos nombres de puertas de la LPM

Copyright© Guillermo Jaquenod,1999

taller en AHDL #1

• Especifique un registro parametrizado de “n” bits

(tipo 74LS374, con Reset asincronico activo bajo

y salida TRI-STATE)

• Escriba el prototipo de su diseño

• Cree el símbolo de su diseño

Creación de un registro de n-Bits

Copyright© Guillermo Jaquenod,1999

taller en AHDL #1

PARAMETERS ( NUM_FF);

SUBDESIGN mi_ls374 ( d[NUM_FF-1..0], clk, oe : INPUT; q[NUM_FF-1..0] : OUTPUT;)

VARIABLE ff[NUM_FF-1..0] : DFF;

BEGIN ff[ ].clk = clk; ff[ ].d = d[ ];

FOR i IN 0 TO NUM_FF-1 GENERATE q[i] = TRI (ff[i].q, oe); END GENERATE;END;

FUNCTION mi_ls374 (d[NUM_FF-1..0], clk, oe) WITH (NUM_FF=8) RETURNS (q[NUM_FF-1..0]);

dn-1...d5d4d3d2d1d0

oeclk

qn-1...q5q4q3q2q1q0

Copyright© Guillermo Jaquenod,1999

taller en AHDL #2

• Especifique un contador UP/DOWN parametrizado de“n” bits, con:

– nClearS: clear sincrónico (activo bajo)

– nLoad: carga sincrónica (activa baja)

– ClearA: clear asincrónico (activo alto)

• Escriba el prototipo de su diseño

• Cree el símbolo de su diseño

Creación de un contador up/down de n-Bits

Copyright© Guillermo Jaquenod,1999

taller en AHDL #2 (b)

PARAMETERS ( NUM_FF);

SUBDESIGN mi_udcnt ( clk,ud,ncl,nld,clra,d[NUM_FF-1..0]: INPUT; q[NUM_FF-1..0] : OUTPUT;)VARIABLE ff[NUM_FF-1..0] : DFF;

BEGIN ff[ ].clk = clk; ff[ ].reset = clra; IF ncl == GND THEN ff[].d = 0; ELSIF nld == GND THEN ff[].d = d[]; ELSIF ud == VCC THEN ff[].d = ff[].q + 1; ELSE ff[].d = ff[].q - 1; END IF;END;

• Pregunta: porqué seusó IF..THEN..ELSEen lugar de CASE?

nloadnclr

clraclockd0......

d(n-1)

q0....q(n-1)

FUNCTION mi_udcnt (clk,udncl, nld, clra ,d[NUM_FF-1..0])WITH (NUM_FF)RETURNS (q[NUM_FF-1..0]);

u/d

Copyright© Guillermo Jaquenod,1999

taller en AHDL #3: Diseño de un semaforo

• Se pretende diseñar un semaforo, cuya secuenciadependa de una entrada asociada a un sensor de luz

• El semaforo tendra dos ciclos de operación: uno diurno yotro nocturno, de acuerdo al dibujo siguiente

• Se supone que en cada flanco de reloj se produce uncambio de estado

• El diseño debe ser realizado en AHDL y empleandomaquinas de estado (primitiva MACHINE)

• La compilacion debe ser usando como dispositivo al MAXEPM7128SLC84-15

• Analizar la forma de minimizar el uso de macroceldas

Copyright© Guillermo Jaquenod,1999

Luz == 1

Luz == 0

Luz

Luz == X

Luz == X

Luz == X

Luz == X

Ciclo diurno Ciclo nocturno

taller en AHDL #3: Diseño de un semaforo

Copyright© Guillermo Jaquenod,1999

SUBDESIGN semaf01 ( timer,init,fotocelda : INPUT; luz_roja,luz_amarilla,luz_verde : OUTPUT;)

VARIABLEposte: MACHINE OF BITS (rojo,amarillo,verde) WITH STATES (pase = B"001",alerta = B"010",stop = "100",prepare = B"110",oscuro = B"000");

BEGINposte.clk = timer; poste.reset = init;

TABLEposte,fotocelda => poste;pase, X => alerta;alerta, 0 => oscuro;alerta, 1 => stop;stop, X => prepare;prepare, X => pase;oscuro, X => alerta;END TABLE;

(luz_roja,luz_amarilla,luz_verde)=(poste.rojo,poste.amarillo,poste.verde);

END;

Copyright© Guillermo Jaquenod,1999

• Se desea realizar un sumador/acumulador parametrizado

para numeros sin signo (rango para n bits: 0..(2^n)-1)

• Si en una suma se supera el valor maximo, el valor

registrado debe quedar “saturado” al maximo, y un

indicador “satur” debe marcar este suceso

• El circuito tiene una linea de puesta a cero, y debe poder

realizar una suma en cada ciclo de reloj

• El diseno debe ser realizado en AHDL, empleando

parametros y LPMs

Sumador acumulador consaturacion

Copyright© Guillermo Jaquenod,1999

SU

MA

DO

R

SA

TUR

AD

OR

AC

UM

ULA

DO

R

Sumador acumulador consaturacion

Coutsumandos suma

acumulada

Registrode

saturacion

clear clocksatur

Copyright© Guillermo Jaquenod,1999

• Disenar un sistema de conteo, multiplexado y display con UPx

• El reloj de 8 MHz, debe ser dividido por 2^23 para llegar a cercade 1 Hertz, y con el actualizar un contador BCD de tres digitos

• Las salidas de los contadores seran multiplexadas para excitarun codificador BCD a 7 segmentos y desde alli a un display

• A partir de dicha senal de control del multiplexado tambien segeneraran tres salidas de selección de digito

• El diseno debe ser escrito en AHDL mediante LPMs

• Debe ser sincronico, empleando para TODOS los contadores elmismo clock global de 8MHz

• Las salidas de excitación de segmentos y de selección dedigitos son activas en “0”.

Contador/Reloj usando la UPx

Copyright© Guillermo Jaquenod,1999

PRESCALER DE 23 ETAPAS

CONTADORBCD

DECENAS BC

D A

7 S

EG

ME

NTO

S

CONTADORBCD

UNIDADES

CONTADORBCD

CENTENAS

8 MHz

Contador/Reloj en hardware

Copyright© Guillermo Jaquenod,1999

Señal Pata del chip usando J1

Selector digito Centenas 49

Selector digito Decenas 51

Selector digito Unidades 48

Segmento A 40

Segmento B 41

Segmento C 35

Segmento D 36

Segmento E 33

Segmento F 39

Segmento G 37

Contador/Reloj en hardware

ab

cd

e

f g

epm7128slc84

definir las patas 81y 63 como salidasforzadas a 0

definir las patas 80y 64 como entradassin conectar

Copyright© Guillermo Jaquenod,1999

Bibliografía

• Thomas & Moorby. The Verilog Hardware Description Language,4th.Edition. Kluwer Academic Publishers, 1998.

• Michael J.S.Smith. Application Specific Integrated Circuits. AddisonWesley 1997.

• ALTERA Corp. MAX+PLUS II VHDL, Version 7.1. Altera Corp.,December 1996.

• J.Bhasker. A VHDL Primer, Revised Edition. Prentice Hall 1995.

• S.S.Leung & M.AA.Shanblatt. ASIC System Design with VHDL: AParadigm. 2nd.Edition, Kluwer Academic Publishers, 1989

• L.Terés et al. VHDL Lenguaje Estándar de Diseño Electrónico.McGraw Hill 1998

• J.Bhasker. A Guide to VHDL Syntax. Prentice Hall 1995.