Guia2_SDI-1_20161

-

Upload

armando-carranza -

Category

Documents

-

view

217 -

download

0

Transcript of Guia2_SDI-1_20161

-

7/26/2019 Guia2_SDI-1_20161

1/3

Universidad de El Salvador

Escuela de Ingeniera Elctrica

Sistemas Digitales

Gua No. 2: Mtodos de Simplificacin: Mapas K y QM.

Catedrtico: Ing. Salvador German.

Instructores: Br. Bryan No Castro Cortez.

Br. David Romeo Vsquez Rodrguez.

Introduccin:

Esta segunda gua pretende ser una introduccin al uso de las potentes herramientas de

simulacin para la verificacin del buen funcionamiento de cdigo escrito en VHDL (Very High

Speed Integrated Circuit Hardware Description Language) y a la vez seguir introduciendo alestudiante en la programacin en este lenguaje.

Asignaciones:

1-

Desarrollar y simular un convertidor de 8421 a 7 segmentos, el cual se describe en la

siguiente figura:

Figura 1: Visualizacin del display y cmo funciona.

Para las combinaciones no vlidas, rellene con ceros.

Obtenga las ecuaciones simplificadas para las salidas utilizando Mapas K (dejando

constancia del proceso), trabajando con MINTERMINOS, codifique cada una en Quartus II

(VHDL) y obtenga la simulacin para las combinaciones validas utilizando ModelSim.

-

7/26/2019 Guia2_SDI-1_20161

2/3

2-

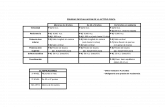

Desarrollar un convertidor de cdigos BCD: 2421, 5421, 7421 y Exceso3, todos al cdigoBCD 8421; estrictamente utilizar solo compuertas bsicas, sern 6 entradas, las primeras 2Entradas, A Y B sern de control, es decir, 00=7421 a 8421, 01= Exceso 3 a 8421, 10=2421a 8421 y 11= 5421 a 8421, y 4 entradas las cuales sern el cdigo BCD que se convertirn;y las salidas sern las 4 del cdigo 8421.

En las salidas no validas de los cdigos BCD se rellenaran con X (dont care conditions).

Obtenga las ecuaciones simplificadas para las salidas utilizando Mapas K (dejandoconstancia del proceso), codifique cada una en Quartus II (VHDL) y obtenga la simulacinpara las combinaciones validas utilizando ModelSim.

3- Simplifique utilizando el mtodo de QM, la ecuacin de la salida de un circuitocomparador de 2 nmeros binarios (K y L) de 2 bits cada uno, que genera un 1 en la

salida cuando K es mayor que L.

Cuando los nmeros sean iguales rellenar con 0.

Habiendo obtenido la ecuacin simplificada por el mtodo antes mencionado, codifquelaen VHDL y obtenga la simulacin utilizando ModelSim.

Investigacin:

Investigue las libreras existentes para VHDL, las caractersticas, elementos que contiene,como accesar a stas y cmo utilizarlas.

Acerca de la tarea:

Un reporte impreso 70%

Contenido del reporte: Portada. 5%

Objetivos (General y especficos). 5%

Introduccin (mx. 1 pgina). 5%

Marco terico (mx. 5 pginas). 5%

Desarrollo de los circuitos:

o Descripcin de los pasos seguidos para la solucin. 10%

o Cdigo VHDL. 15%

o Grficos obtenidos para cada circuito (3 a 5 imgenes por circuito). 10%

o Observaciones. 10%

Respuesta a la seccin de investigacin. 10%

Conclusiones (mx. 1 pgina). 20%

Bibliografa. 5%

-

7/26/2019 Guia2_SDI-1_20161

3/3

Un Archivo .rar 30%

Contenido del archivo .rar:

Reporte en formato PDF y WORD. 25%

Cdigos utilizados (*.vhd) y todos los que genera el proceso de compilacin y ejecucin. 40%

Imgenes de los resultados. 35%

NOTA:El reporte se entregara en un sobre manila rotulado con los nombres y carnet. Elcontenido del archivo .rar deber ir ordenado, con carpetas individuales para cada temmencionado, ejemplo: IMGENES, CIRCUITO1, etc. Si existen conflictos sobre el tamaodel archivo a adjuntar, nicamente dividirlo en las partes necesarias. Ej: tarea2_parte1,tarea2_parte2, etc. Favor en el asunto de el/los correos agregar los carnets de losintegrantesSe recibirn estos archivos y tomaran como vlidos los que sean enviados como fecha yhora lmite: lunes 25 de abril a las 11:59PM.Direccin de correo electrnico a la cual se debe enviar el archivo .rar:[email protected]

Bibliografa:

VHDL Lenguaje para descripcin y modelado de circuitos, Fernando Pardo Carpio,

Universidad de Valencia 1997.

DIGLENSY SAC Primera Empresa del Per Dedicada al Desarrollo Electrnico, tutorial VHDL,

http://www.diglensy.com/

Anlisis y diseo de circuitos lgicos digitales, Vctor Nelson, 1 Ed.

mailto:[email protected]:[email protected]://www.diglensy.com/http://www.diglensy.com/http://www.diglensy.com/mailto:[email protected]