IP11

-

Upload

felix-valentin-santos-canari -

Category

Documents

-

view

15 -

download

1

Transcript of IP11

“Año de la Inversión para el Desarrollo Rural y la Seguridad Alimentaria”

INFORME PREVIO - LABORATORIO N° 11

TEMA: AMPLIFICADOR CON TRANSISTOR FET

PROFESOR: López Aramburú Fernando CURSO: Laboratorio de Electrónica I EE441-M ESTUDIANTE: Santos Cañari, Félix V. 20090150A

ESPECIALIDAD: Ingeniería Eléctrica

FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA 21 de noviembre del 2013

OBJETIVOS

Analizar la polarización de transistores Unipolares y familiarizarse con los cuidados al utilizar

estos dispositivos, trazar las rectas de carga, transferencia y verificar la ganancia de tensión.

FUNDAMENTO TEÓRICO

El desempeño del transistor de efecto de campo (FET, field-effect transistor) propuesto por W. Shockley en 1952, es diferente del desempeño del BJT. El parámetro de control para un FET es la tensión en vez de la corriente.

El FET es un dispositivo unipolar, ya que la corriente existe tanto en forma de electrones como de huecos. En un FET de canal n, la corriente se debe a los electrones, mientras que un FET de canal p, se deben a los huecos. Ambos tipos de FET se controlan por una tensión entre la compuerta y la fuente.

Al comparar el FET con el BJT se aprecia que el drenaje(D) es análogo al colector, en tanto que la fuente(S) es análoga al emisor. Un tercer contacto, la compuerta(G) , es análogo a la base. La fuente y el drenaje de un FET se pueden intercambiar sin afectar la operación del transistor.

Operación y Construcción del JFET

Al igual que el BJT, el fet es un dispositivo de tres terminales, pero sólo tiene una unión pn en vez de dos, como en el BJT. En la figura 1 se muestra un esquema de la estructura física del JFET.

El JFET de canal n, mostrado en la figura 1(a), se construye utilizando una cinta de material de tipo n, con dos materiales de tipo p difundidos en ella, uno en cada lado. El JFET de canal p tiene una cinta de material de tipo p con dos materiales de tipo n difundidos en ella, como se muestra en la figura 1(b).

Figura 1 Para entender la operación del JFET, se conecta el JFET de canal n de la figura 1(a) a un circuito externo.

Se aplica una fuente de tensión, VDD, al drenaje (ésta es análoga a la fuente de tensión VCC para el BJT) y

se envía a tierra. Una fuente de tensión de compuerta, VGG , se aplica a la compuerta (aquélla análoga a la

VBB para el BJT) y se puede observar en la figura2(a).

Figura 2 VDD proporciona una tensión drenaje a fuente, VDS, que provoca una corriente de drenaje, id, del drenaje a la fuente. La corriente de drenaje, id, que es idéntica a la corriente de la fuente, existe en el canal

rodeado por la compuerta de tipo p. La tensión compuerta a fuente, VGS, que es igual a -VGG (obsérvese la figura 2(a)), crea una región desértica en el canal, que reduce el ancho de este y por tanto aumenta la resistencia entre drenaje y fuente. Como la unión compuerta-fuente está polarizada en inverso, el resultado es una corriente de compuerta nula.

Considérese la operación de un JFET con VGS = 0, como se muestra en la figura 2(b). La corriente de drenaje, iD, a través del canal n del drenaje a la fuente, provoca una caída de tensión a lo largo del canal, con el potencial más alto en la unión drenaje-compuerta. Esta tensión positiva en la unión drenaje-fuente polariza en inverso la unión pn y produce una región desértica, como se muestra en el área sombrada en la figura 2(b). Cuando se incrementa VDS, también aumenta la corriente de drenaje, iD, como se muestra en la figura 3. El resultado de esta acción es un aumento de la región desértica y dela resistencia del canal entre el drenaje y la fuente. Conforme aumenta VDS más allá de este punto, id permanece constante.

Figura 3 Característica de transferencia del JFET.

De gran valor en el diseño con JFET es la característica de transferencia, que es una gráfica de la corriente de drenaje, id, como función de la tensión compuerta a fuente, VGS , por encima del estrangulamiento. Se gráfica con VDS igual a una constante, aunque la característica de transferencia es en esencia independiente de VDS . Esto se puede ver a partir de las curvas iD-VDS de la figura 4, donde cada curva se vuelve plana para los valores de VDS>Vp. Cada curva tiene un punto de saturación diferente.

Figura 4 En la figura 5, se muestran las característica de transferencia y las características iD- VGS para un JFET de

canal n. Se grafican con el eje iD común. Las características de transferencia se pueden obtener de una

extensión de las curvas iD-vDS. Un método útil de determinar la característica de transferencia es con ayuda

de la siguiente relación:

iD / IDSS ( 1 - vGS / vp )2 ............(1)

Por tanto, sólo se necesita conocer IDSS y Vp y toda la característica queda determinada.

Figura 5

Las hojas de datos de los fabricantes a menudo dan estos parámetros, por lo que se puede construir la

característica de transferencia o utilizar la ecuación anterior directamente. Nótese que iD se satura (es

decir, se vuelve constante) conforme vDS excede la tensión necesaria para vDS excede la tensión necesaria

para que el canal estrangule. Esto puede expresar como una ecuación para vDS(sat) para cada curva, como

sigue:

vDS(sat) = vGS + VP

Conforme vGS se vuelve más negativo, el estrangulamiento se produce a menores valores de vDS y la

corriente de saturación se vuelve más pequeña. La región útil para operación lineal es por arriba del

estrangulamiento y por debajo de la tensión de ruptura. En esta región de acuerdo a la ecuación (1) o con

la característica de transferencia. Las curvas características de transferencia e iD- vGS para el JFET, que

muestra en la figura 5. El FET es un dispositivo controlado por tensión, mientras que el BJT se controla por

corriente. El parámetro de control para el FET es la tensión compuerta-fuente en lugar de la corriente de

base, como en el BJT.

La tensión de ruptura es función de vGS así como de vDS. Conforme aumenta la magnitud de la tensión entre compuerta y fuente (más negativa para el canal n y más positiva para el canal p), disminuye la tensión de ruptura. Con vGS = vp, la corriente de drenaje es cero (excepto por una pequeña corriente de fuga), y con vGS = 0, la corriente de drenaje se satura a un valor: iD = IDSS

donde IDSS es la corriente de saturación drenaje a fuente.

Entre el estrangulamiento y la ruptura, la corriente de drenaje está saturada y no cambia significativamente como función de vDS. La corriente de saturación drenaje a fuente, IDSS, es función de la temperatura:

IDSS = K.T - 3/2

donde K es una constante. La tensión de estrangulamiento es una función aproximadamente lineal de la temperatura; por lo tanto:

VP = - KP.T

donde KP 2 mV/C.

MATERIAL Y EQUIPO.

1 Osciloscopio.

1 Multimetro.

1 Fuente DC.

1 Generador.

1 Protoboard.

Transistor JFET : 2N5485 ó 2N5486 (canal N)

Resistencias : 1M, 33K, 10K, 10K, 5.6K, 3.3K, 1K (1/4W)

Condensadores : 0.1uF, 10uF, 22uF (16V)

PROCEDIMIENTO

1). Armar el circuito de la figura 1.

Figura 1 2). Teniendo cuidado de verificar la conexión del JFET, medir el punto de operación tomando las tensiones de los terminales del transistor respecto a tierra, las corrientes tomadas en forma indirecta (VRs / Irs). No tomar entre terminales del dispositivo, ni medir las resistencias internas con el multimetro, pues se pueden exceder las corrientes permitidas en directa conociendo que trabaja con el Gate polarizado en inversa.

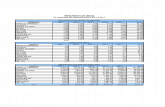

Cto. Orig. Rs = 1K Rs = 5.6K Rs = 3.3K y R3 = 5.6K

Vd

Vs

Vg

3). Con el ckto. original, aplicar una señal senoidal de 20mV (pico) a una frecuencia de 1khz y determinar, la ganancia de tensión midiendo la salida Vo = ................... 4). Aumentar el nivel de Vi hasta observar una distorsión en la señal de salida Vo. La deformación no debe llegar a recortes de la señal. Sino hasta apreciar una alineación, deformando las ondulaciones positivas y negativas en distinta proporción Vomás = ...................

5). Manteniendo Vi constante, variar la frecuencia del generador llenando la tabla adjunta.

f (Hz) 50 100 200 500 1K 2K 5K 10K 20K 50K 100K 200K 500K

Vo

(verificar en cada medición que Vi , NO VARÍE) 6). Retirar el condensador C1=22uF y determinar la ganancia de tensión. (Vo/Vi) = AV =.......

PREGUNTAS DEL INFORME PREVIO

1). Obtener de los manuales, información sobre los dispositivos a utilizar y presentar los datos más

importantes.

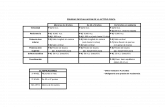

Hoja de especificaciones del Transistor 2N5485.

JFET canal n (UHF/VHF) amplificador de alta frecuencia, 4 dB máximo a 400 MHz.

Transconductancia (valor típico) ............................................................................... 4000 u -1

Voltaje de ruptura (VDS = Vpo) ..................................................................................... 25 V

Corriente IDSS .................................................................................................. IDSS(min) = 4 mA

IDSS(máx) = 10 mA

VGS(máx) Vpo (voltaje en corto circuito) .......................................................................... 4V

Potencia máxima .......................................................................................................... 310 mW

Especificaciones del transistor FET 2N5485 2). Resolver teóricamente el circuito propuesto, obteniendo la ganancia en pequeña señal y usando los

parámetros respectivos.

Análisis del circuito JFET

Conocemos: IDSS(min)=4mA, IDSS(máx)=10 mA, Vp=4V. Trabajando los dos valores: * Para IDSS(min) = 4 mA, calculando el punto Q, de donde hallaremos gm ==> VGSQ = - Rs.IDQ = -3.3IDQ y tambíen IDQ = IDSS. ( 1 - VGSQ / Vp )2 = ( 1 - (-3.3IDQ/-VP))2 IDQ

2 - 5.22 IDQ + 1.469 = 0 de donde IDQ = 4.9169 mA y IDQ = 0.2938 mA Como IDSS = 4mA descartamos 4.9169mA.

VGSQ = -3.3 * 0.2988 = - 0.986 V

==> gm = IDS / VGS = -2IDSS / Vp (1 - VGSQ / Vp) = (4(2)/-(-4)).(1-(-0.986)/(-4)) ==> gm = 1.507 ms

==> V = (-RDRL)/(Rsca+ 1/gm ) = -11.55

==> i = V.Ri / RL = -11.56* 106 / 33.103 = - 350.26 * Para IDSS(max) = 8mA, calculando el punto Q, de donde hallaremos gm. ==> VGSQ = - Rs.IDQ = -3.3IDQ y también IDQ = IDSS. ( 1 - VGSQ / Vp )2 = ( 1 - (-3.3IDQ/-4))2 IDQ

2 - 5.032IDQ + 1.469 = 0

IDQ = 0.31117 mA

VGSQ = -3.3 * 0.331117 = - 1.02686 V

==> gm = IDS / VGS = -2IDSS / Vp (1 - VGSQ / Vp) = (2(8)/(4)).(1-(-1.02686)/(-4)) ==> gm = 2.973 ms

==> V = (-RDRL)/(Rsca+ 1/gm ) = 22.80

==> i = V.Ri / RL = 22.80* 106 / 33.103 = 690.99

BIBLIOGRAFÍA.

1) Manual de Laboratorio de Circuitos Electrónicos I. Universidad Nacional de Ingeniería. Facultad de Ingeniería Eléctrica y Electrónica.

2) Diseño Electrónico. Circuitos y Sistemas. Savant / Roden / Carpenter. Segunda edición. 1992.