9sdd

-

Upload

karen-martinez -

Category

Documents

-

view

49 -

download

0

Transcript of 9sdd

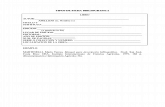

SISTEMAS DIGITALES ______

C. Baena, J.I. Escudero, I. Gmez y M. Valencia

UNIVERSIDAD DE SEVILLA DEPARTAMENTO DE TECNOLOGA ELECTRNICA

Carmen Baena Jos Ignacio Escudero Isabel Gmez Manuel Valencia

Sistemas Digitales

Departamento de Tecnologa Electrnica ETS Ingeniera Informtica. Universidad de Sevilla Avda. Reina Mercedes, s/n 41012 Sevilla Tfos. + 34 954 552 785, + 34 954 556 159. Fax: +34 954 552 764 Primera edicin. 1997 (N TESP - 9702 -012) Revisin actual: 2008

Este documento es una actualizacin de la primera edicin de 1997 de:

Prlogo (actualizando la ed. 1997)

En los estudios de Informtica en la Universidad de Sevilla, inicialmente en la asignatura Circuitos y Sistemas Digitales I y, tras el cambio de los planes de estudio de 1997, en las asignaturas Estructura de Computadores (de I.I. y de ITIS) y Estructura y Tecnologa de Computadores 2 (de ITIG), se desarrolla la materia sobre sistemas digitales a nivel RT y su aplicacin al diseo de computadores, necesariamente simples. En 1997 no conocamos la existencia de ningn texto en el que se pudiera estudiar adecuadamente esta materia. Esto nos condujo, en dicha fecha, a desarrollar este libro, con el principal objetivo de disponer de un texto donde estudiar y aprender esta interesante e importante materia en la que, adems de establecer metodologas y realizar diseos complejos, se tiende el puente entre el hardware y el software. En los tres captulos del libro los autores intentaron aportar su dilatada experiencia como profesores de las mencionadas asignaturas. No obstante, aunque el libro lo firmaron slo cuatro autores, no hubiera sido posible sin la aportacin y colaboracin de los restantes profesores: as que, muchas gracias a Manolo Bellido, Alberto Molina, Pilar Parra y Paco Prez. Desde que se dio por finalizada la primera edicin de 1997, el libro ha sido puesto a libre disposicin de los alumnos en la copistera del centro todos los cursos, sin ms coste que el propio de su reproduccin en fotocopias. En los ms de 10 aos transcurridos, centenares de alumnos del primer curso de cualquiera de las titulaciones de Informtica han estudiado dichas materias en este libro, localizando varias erratas. En la presente edicin no slo se pretende corregir los fallos detectados sino, sobre todo, actualizar los contenidos con lo aportado durante el periodo de tiempo transcurrido. No obstante, hemos deseado mantener la estructura original, aadiendo anexos como forma de incluir los nuevos contenidos. El original de 1997 haba sido creado con diferentes procesadores de texto, cuya traslacin de uno a otro no es directa. En esta edicin, pues, ha sido necesario volver a editar buena parte de la materia en el nuevo procesador. El presente libro expone los aspectos tericos de los sistemas digitales a nivel RT. Aunque contiene algunos ejercicios, su estudio debe completarse con la realizacin de problemas (cuyos enunciados no se incluyen en esta obra). Al estudiar esta nueva edicin del libro posiblemente que se detectarn erratas, partes desarrolladas defectuosamente o fallos de cualquier tipo. Estaramos muy agradecidos si nos comunican todos los errores que encuentren (p. ej., enviando un mail a [email protected]). Los tres captulos incluidos son: 1. Introduccin a los sistemas digitales. En l se plantean las formas de disear, describir y realizar los sistemas digitales a nivel RT. Como ejemplo de diseo, se desarrolla como una calculadora de sumas y restas.

2. Diseo de unidades de control. Se aborda la realizacin del controlador de los sistemas digitales, principalmente utilizando la tcnica de un biestable por estado, pero presentando diversas opciones ms, entre las que se incluye el control microprogramado con ROM y con PLA. 3. Diseo a nivel RT de un computador simple. Se introduce el concepto y modo de operacin de los computadores desde una perspectiva de diseo, partiendo de la calculadora diseada en el captulo 1. Se desarrollan dos computadores simples. El segundo de ellos tiene un juego de instrucciones que permite ejecutar programas de bajo nivel para resolver tareas medianamente complejas. De este computador simple se dispone de un emulador que ser utilizado en las prcticas de programacin en ensamblador. Anexos: * Ensamblador del Computador Simple: Se describe el ensamblador y se realizan mltiples ejemplos de programacin con este lenguaje ensamblador. Tambin se presenta el emulador que permite ejecutar estos programas y ver el flujo de datos tanto instruccin a instruccin (nivel ISP) como operacin a operacin (nivel RT). Este emulador se utiliza en prcticas de laboratorio. * Multiplicacin de magnitudes: Se describen diferentes formas de multiplicar en binario. Tres de ellas se aplicarn en prcticas de laboratorio. * Glosario: Un extenso nmero de conceptos son explicados brevemente en este anexo. * Referencias: Contiene las referencias a la bibliografa consultada para elaborar el libro.

ndice

CAPTULO 1: INTRODUCCIN A LOS SISTEMAS DIGITALES1.1 INTRODUCCIN 1.2 EL NIVEL DE TRANSFERENCIA ENTRE REGISTROS (RT) 1.2.1 Descripcin de registros a nivel RT 1.2.2 Operaciones de transferencias entre registros 1.3 TCNICAS DE INTERCONEXIN MEDIANTE BUSES 1.4 REALIZACIN DE SISTEMAS DIGITALES 1.5 CARTAS ASM 1.5.1 Definiciones 1.5.2 Relacin entre cartas ASM y tablas de estado 1.5.3 Ejemplos de cartas ASM 1.5.4 Consideraciones temporales 1.5.5 Carta ASM del ejemplo 1.5.6 Unin entre cartas ASM 1.6 LENGUAJE DE DESCRIPCIN DE HARDWARE (HDL) SIMPLIFICADO 1.6.1 Descripcin del HDL 1.6.2 Programa HDL de la calculadora del ejemplo 1.7 EL DISEO DE LA UNIDAD DE CONTROL 1.8 EL USO DEL SISTEMA DEL EJEMPLO 1 3 3 11 14 20 29 29 33 35 41 44 47 49 49 51 51 53

CAPTULO 2: DISEO DE UNIDADES DE CONTROL2.1 INTRODUCCIN 2.2 ESTRATEGIAS DE REALIZACIN DE CONTROLADORES 2.2.1 Objetivos y criterios de diseo 2.2.2 Una clasificacin de estrategias de implementacin 2.3 REALIZACIN LGICA DISCRETA 2.4 REALIZACIN BASADA EN UN BIESTABLE POR ESTADO 2.4.1 Fundamentos 2.4.2 Asociacin carta ASM con circuito de control 2.4.3 Casos particulares 55 57 57 58 58 64 64 66 68

2.4.3.1 Bifurcacin de acciones en una microoperacin 2.4.3.2 Macrooperaciones de longitud variable 2.4.3.3 Repeticin de microoperaciones 2.4.3.4 Anulacin de comandos 2.4.4 Solucin a la unidad de control de la calculadora de nuestro ejemplo 2.5 PROBLEMAS DE COMIENZO 2.6 OTROS TIPOS DE REALIZACIN 2.6.1 Implementacin con multiplexores y flip-flops D 2.6.2 Realizacin con dispositivos lgicos programables PLDs 2.6.2.1 Realizacin con PLA 2.6.2.2 Realizacin con PAL 2.6.2.3 Realizacin con ROM 2.6.2.4 Introduccin al control microprogramado 2. 7 RESUMEN

68 69 70 70 71 72 77 77 81 81 86 86 92 96

CAPTULO 3: DISEO A NIVEL RT DE UN COMPUTADOR SIMPLE3.1 INTRODUCCIN 3.2 COMPUTADOR SIMPLE 1 (CS1) 3.2.1 Unidad de datos 3.2.2 Ejecucin automtica del programa 3.2.3 El sistema digital CS1 3.2.3.1 El conjunto de instrucciones 3.2.3.2 Requisitos hardware 3.2.3.3 Unidad de control 3.2.4 Ejemplo de uso del computador simple 1 3.3 COMPUTADOR SIMPLE 2 (CS2) 3.3.1 La pluralidad de instrucciones a nivel ISP 3.3.1.1 Tipos de instrucciones 3.2.1.2 Modos de direccionamiento 3.3.2 Conjunto de instrucciones del CS2 3.3.3 Estructura del computador simple 2 3.3.4 Ejemplos de uso del computador simple 2 3.3.4.1 Ejemplo I: suma de "n" sumandos 3.3.4.2 Ejemplo II: multiplicacin 3.3.4.3 Ejemplo III: suma de productos 3.4 CONCEPTO DE COMPUTADOR 3.4.1 Organizacin bsica 3.4.2 Instrucciones multipalabras 3.4.3 La operacin de entrada/salida Anexo I Ensamblador del Computador Simple Anexo II Multiplicacin de magnitudes Anexo III Glosario Anexo IV Referencias 97 99 99 103 106 106 107 108 113 114 115 115 117 119 124 128 128 130 133 135 136 142 145 149 167 171 181

CAPTULO 1: Introduccin a los sistemas digitales

1.1 INTRODUCCINEl aumento de la complejidad al evolucionar desde los CIRCUITOS hasta los SISTEMAS digitales tiene mltiples consecuencias en distintos niveles, algunos de los cuales se resumen en la Fig. 1.1. Una de las primeras es la necesidad de incrementar el nivel de abstraccin de la informacin que se manipula. En nuestro caso esto significa que debemos pasar de manejar variables binarias (0 y 1) a agrupaciones de estas seales, agrupaciones en las que la informacin significativa es el dato que llevan. Con esta nueva perspectiva, la funcionalidad del Sistema Digital consiste en el procesado que se realiza sobre los datos. Por ejemplo, si se desea sumar el dato A con el dato B, lo que es significativo desde el nivel de Sistema es la operacin A + B sin importar el valor binario concreto de A o de B.

CIRCUITOS Informacin Nivel/Lenguaje Funcionalidad Componentes Conexin Organizacin 0,1 De conmutacin Mquinas de estados finitos Puertas y biestables Lneas (cables) Combinacional y almacenamiento (memoria)

SISTEMAS Palabras de datos RT(Register Transfer) Operaciones (instrucciones) MUX, ALU, ..., registros,... Buses Procesado de datos y control

Figura 1.1: Circuitos versus Sistemas.

Por otra parte, el lenguaje de conmutacin (combinacional y secuencial) muy til al manejar 0's y 1's, no puede describir adecuadamente el procesado entre datos. Surge, pues, la necesidad de emplear un nuevo lenguaje, ms abstracto, apropiado para dicho procesado. Este lenguaje es denominado de transferencia entre registros (RT). Este nombre procede del que reciben genricamente los dispositivos (registros) que almacenan datos. El lenguaje de descripcin establece pues, otra diferencia: mientras que los circuitos ocupan el denominado nivel de conmutacin, los sistemas se sitan en el nivel RT.

2

INTRODUCCIN A LOS SISTEMAS DIGITALES

Desde la perspectiva funcional, los circuitos realizan mquinas de estados finitos. Estrictamente hablando, los sistemas tambin. Sin embargo, como la utilidad principal de estos sistemas consiste en el procesado de datos, es preferible describir su funcionalidad en trminos de operaciones entre datos, tambin llamados macrooperaciones o instrucciones del sistema. Ello permite, por una parte, manejar funciones ms complejas ya que es posible encadenar secuencias de estas instrucciones (hacer un programa) para resolver problemas mucho ms complicados que los resueltos por cada instruccin por separado. Por otra parte, tambin se consigue aproximar el lenguaje de la mquina al del ser humano, aunque simultneamente esto signifique un alejamiento entre el lenguaje de descripcin usado y la ejecucin real de las tareas por los circuitos. El nivel de la macrooperacin se sita en un punto intermedio entre las operaciones de conmutacin del hardware y las instrucciones software. Adems, la descripcin funcional mediante operaciones entre datos comparte la resolucin algortmica de problemas con otras muchas aproximaciones (como la de la programacin). Con todo ello se tiende un importante puente de conexin entre el hardware y el software. Particularizando sobre la realizacin de los Sistemas Digitales, el nuevo enfoque supone cambios en los componentes de diseo y en las conexiones entre ellos. En relacin a los componentes, se utilizan subsistemas (secuenciales y combinacionales) preferentemente a puertas y biestables. Con ello se consigue una mayor aproximacin entre el lenguaje de descripcin y los componentes utilizados, a la vez que se aprovecha la mayor potencia y flexibilidad de los subsistemas frente a las puertas y biestables. Adems, el uso de estos componentes est en consonancia con los propios cambios en los criterios de diseo en los que ahora priman los aspectos de modularidad, sencillez en el proceso de diseo, fiabilidad, testabilidad, etc., sobre el del coste en nmero de puertas. Por otra parte, la interconexin entre los componentes se realiza mediante buses (conjunto de lneas con un significado global claro: p. ej., bus de datos) pero en el que pierde sentido cada una de sus lneas en concreto. Es por estos buses por donde viajan los datos sin importar mucho si una de estas lneas lleva un 1 un 0. De todo lo anterior surge un cambio sustancial en la organizacin del Sistema en relacin a la del Circuito, tal como se muestra en la Fig. 1.2. En vez de diferenciar las partes combinacional (funciones de prximo estado y salida) y secuencial (elementos de almacenamiento de estado), un Sistema Digital se organiza en una Unidad de Procesado de Datos(UPD) y una Unidad de Control (UC). La UPD tambin llamada simplemente Unidad de Procesado o Unidad de Datos, es la parte del Sistema que: - recibe los datos de entrada DIN. - procesa esos datos, para lo cual realiza las transferencias entre registros indicadas en el algoritmo que se desea ejecutar. - saca al exterior los resultados de salida DOUT. Por su parte, la UC es la parte del Sistema que controla las tareas que realiza la UPD. En particular las funciones de la UC son: - generar la seales de control (Z) que necesitan los componentes de la unidad de datos, para realizar el proceso correspondiente. Asmismo, deber generar las posibles salidas al exterior que correspondan a seales de control (ZOUT), como es, por ejemplo, una seal de fin de tarea. A las seales de salida del controlador se les denominan comandos. - establecer la secuencia de acciones a la que obliga el algoritmo que se ejecuta. Esto significa que, para todo estado, adems de generar los comandos, la UC debe conocer su prximo estado y alcanzarlo en el siguiente ciclo. La posible evolucin de la secuencia de estados depender de un conjunto de seales (X, XIN) que actan como entradas de control y a las que se denomina cualificadores. Al igual que los comandos, los cualificadores pueden provenir del exterior (XIN) o de la unidad de datos (X) en cuyo caso a veces se les denomina sealesDpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

3

de estado, nombre que a su vez alude al estado del procesado: si hay acarreo, resultado nulo, .... (En ingls, procede de status que no debe confundirse con el estado interno de una mquina secuencial : state).

Cada unidad del sistema, tanto si se trata de la de datos como si es la de control, es en realidad una mquina de estados, por lo que realiza funciones combinacionales y secuenciales y pueden, por tanto, ser estudiadas como circuito secuencial. Esta perspectiva ser, en efecto, til para tratar algunas formas de realizacin de unidades de control. Sin embargo, es de nula utilidad al describir las unidades de procesado de datos. A lo largo de este texto y salvo expresa indicacion en contra, los Sistemas Digitales que manejaremos sern sncronos y la misma seal de reloj gobernar ambas unidades: en la de datos el reloj controlar las distintas operaciones de escritura en los registros; en la de control, gobernar los cambios de estado mediante los que se establece la secuencia de transferencias de datos entre los registros. El tratamiento de operaciones asncronas no ser, pues, objeto de estudio en este texto.X1 Xn Z1 Zk ... ... XIN Unidad de control Z ZOUT

circuito combinacional

reloj y1 ... B1 ... ... DIN

X

Unidad de procesado

DOUT

yr reloj

Br

(a)

X: cualificadores o entradas de control Z: comandos o salidas de control D: datos (b)

Figura 1.2: (a)Estructura general de una FSM (Mquina de estados finitos). (b)Estructura general de un sistema digital.

1.2 EL NIVEL DE TRANSFERENCIA ENTRE REGISTROS (RT)El nivel RT (Register Transfer) es una forma de descripcin de sistemas digitales mediante datos almacenados en registros. El trmino registro, en el nivel RT de los sistemas digitales, es un trmino ms amplio que el asociado al subsistema secuencial concreto del que toma el nombre. En efecto, con registro nos referimos a cualquier dispositivo capaz de almacenar datos, englobando: los biestables como registros de 1 bit; los contadores como registros que incrementan/decrementan el dato almacenado; las memorias como banco de registros; y los propios registros (de carga en paralelo y de desplazamiento) que son los que dan nombre a este nivel de descripcin.

1.2.1 Descripcin de registros a nivel RT.Al ser el componente bsico de este nivel, el registro debe ser adecuadamente conocido y descrito bajo las perspectivas de uso en los sistemas digitales: 1) como bloque o componente del sistema (representacin estructural); 2) como elemento de almacenamiento de la informacin (representacin de datos); y 3) como circuito que tiene una forma dada de operar (representacin funcional). A conti-

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

4

INTRODUCCIN A LOS SISTEMAS DIGITALES

nuacin se detallan estas tres perspectivas. Representacin estructural. A nivel estructural un registro genrico es (Fig. 1.3) un bloque de n bits con m seales de control: s1, ..., sm, que dependiendo de la combinacin binaria que posean, harn que el registro realice una operacin u otra. Adems poseer un conjunto de lneas de entrada de datos (de las que en la Fig. 1.3 se han representado las n lneas de entrada en paralelo), as como otro conjunto de lneas de salida de datos por donde se podr acceder al contenido (salidas en paralelo en la Fig. 1.3). Adems, al ser dispositivos secuenciales, poseern su entrada de reloj que, salvo indicacin en contra, supondremos en adelante que ser activa en el flanco de subida.DIN n s1 sm reloj sx: entradas de seleccin o control de operacin A[n] n DOUTFigura 1.3: Representacin estructural de un registro.

...

Dxx: terminales de datos

Representacin de datos. Con esta representacin nos referimos al contenido que tiene almacenado el registro y que, en general, es un dato. A este se puede acceder completamente, esto es, a toda la palabra binaria en l almacenada, o parcialmente, es decir, slo a algunos bits del dato. La representacin del dato se esquematiza en la Fig. 1.4, en la que hemos supuesto que el nombre del registro con el que trabajamos es A. Si hacemos referencia al dato almacenado al completo lo llamaremos [A] o, cuando no haya posibilidad de confundir el dato y el dispositivo, simplemente A. Sin embargo, si queremos referirnos a bits sueltos del dato lo haremos escribiendo los subndices correspondientes teniendo en cuenta que en este texto representamos a la derecha el bit menos significativo (posicin 0). As, [Ai-j,k] = [A]i-j,k hace mecin a los bits correlativos desde el i hasta el j, y, adems, al bit k-simo. Al igual que antes, si no hay confusin entre lneas y bits de datos, tambin puede ponerse Ai-j,k.n -1 ........ 1 0 A

[A] A = 01110011 [A7,4-2,0] A7,4-2,0 = 01001

7 0

6 1

5 1

4 1

3 0

2 0

1 1

0 1

A

Figura 1.4: Representacin de datos.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

5

Representacin funcional. La representacin funcional debe describir la operacin y suele ser la representacin ms compleja del registro. En general se pueden distinguir tres tipos de funcionalidades: la operacin de escritura, la operacin de lectura y la activacin de las seales de control. Pasemos a describirlas en ms detalle. - Escritura en R: aquellas acciones sobre el registro que conducen a una modificacin del dato almacenado. R nuevo dato Se trata de una operacin de tipo secuencial. Es decir, el nuevo dato se carga en el registro R de forma sincronizada con su seal de reloj. Las operaciones ms comunes de escritura y su expresin a nivel RT se muestran en la Tabla 1.1. OperacinCarga en paralelo Desplazamiento a derecha Desplazamiento a izquierda Incremento (Decremento) Puesta a 0 ( 1) A DIN An-1 Dr, Ai Ai+1 i n-1; A SHR(A,Dr) A0 Dl, Ai Ai-1 i 0; A SHL(A,Dl) A A + 1, (A A - 1) (Ai 1 i A 1 . . . 1)

Notacin RT

Ai 0 i A 0 AA

Inhibicin (NOP)

Tabla 1.1: Principales operaciones de un registro a nivel RT. En la operacin de carga en paralelo, el nuevo dato del registro es el que hay en las entradas DIN (Fig. 1.3) cuando se activa el flanco de reloj. Las operaciones de desplazamiento a derecha y a izquierda (Fig. 1.5), adems del desplazamiento interno de los bits, supone la entrada de un nuevo bit por una lnea (Dr y Dl, respectivamente) que se almacena en una de las celdas extremas del registro (An-1 y A0, respectivamente). El nuevo dato que se almacena est constituido, pues, por n-1 bits del dato antiguo, pero ocupando ahora las posiciones consecutivas, ms el nuevo bit que entra por la lnea Dr Dl. En notacin RT estas operaciones tienen dos formas de escribirse: una, expresando la operacin de las distintas celdas individualmente; la otra, englobndolas bajo la operacin SHR SHL(registro, bit)1. Por su parte, las operaciones tpicas del contador, de incremento y de decremento, se describen sumando o restando la unidad al dato presente, sin especificar nada ms ya que se asume que son contadores de magnitud y que hacen la cuenta. La operacin de borrado o puesta a 0 se escribe poniendo 0 como nuevo dato. La operacin de puesta a 1 no puede ponerse escribiendo 1 como nuevo dato ya que el nuevo dato es todos los biestables a 1, con magnitud de 2n-1; en su lugar es simple poner 11...11 como nuevo dato. Por ltimo, la operacin de inhibicin o de no-operacin (NOP) deja en el registro1. Ntese que el significado de A vara segn donde aparezca: si est a la derecha de la flecha (posicin fuente) representa el dato actualmente almacenado en el registro, mientras que si est a la izquierda (posicin destino) indica el registro que, tras la actuacin del flanco activo de reloj, almacenar el nuevo dato.

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

6

INTRODUCCIN A LOS SISTEMAS DIGITALES

el mismo dato que haba.1 Dr Ck 0 0 1 1 0 1 A Ck 0 0 SHL(A,Dl) 0 1 Dl 0 0 1 1 0 0 A Ck 0 0 1 1 0 1 1 A 0 1 1 0 1 Dl 1 A

1 SHL(A,Dr) 0 1 Dr Ck 1

(a)Figura 1.5: Operaciones de desplazamiento: (a) A derecha; (b) A izquierda.

(b)

- Lectura de R: bsicamente consiste en acceder al dato almacenado o a alguna funcin combinacional del mismo a travs de las lneas de salida del registro. En notacin RT se escribe: SAL = dato/funcin del dato donde SAL es el nombre de las salidas. El smbolo = hace alusin a que la lectura es una operacin de tipo combinacional. Esto es, salvo los retrasos de propagacin de la lgica, las salidas SAL muestran el valor actual del dato o de la funcin del dato. Por ejemplo, si el registro de la Fig. 1.3 se lee en paralelo cuando su contenido es el de la Fig. 1.4, la operacin de lectura en notacin RT es: DOUT = 73 donde el nmero 73 est en hexadecimal, que es la notacin habitual para dar datos binarios cuando no se usa el propio valor binario. Un ejemplo de lectura de una funcin del dato se muestra en la Fig. 1.6. La salida CERO se activa cuando el registro A est borrado. A nivel RT se escribe: CERO = NOR(An-1, ..., A0) aunque tambin puede escribirse como: CERO = 0 CERO = 1 si A 0 si A = 0

Otros casos de salida tipo funcin del dato son las seales de fin de ciclo de cuenta de los contadores (llamadas carry en los ascendentes y borrow en los descendentes).n -1 . . . 1 0

A >1 CERO

...

Figura 1.6: Lectura tipo funcin del dato.

La operacin de lectura, sea del dato o de una funcin del dato, puede ser incondicional o condicional. - Lectura incondicional. Es la que ocurre si el acceso desde la salida no est condicionado por ninguna seal: las salidas del registro muestran siempre el dato almacenado (Fig. 1.7-a)Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

7

o la funcin combinacional del dato. - Lectura condicional. En este caso slo se podr acceder al dato almacenado en el registro si cierta condicin de control, que aqu llamaremos seal de lectura R (read), es verdadera. En notacin RT se escribir: R=1 R=0 DOUT = A DOUT = ?

Por lo general, cuando el registro comparte el bus desde el que se accede a sus datos (vase apartado 1.3), en sus lneas de salida se muestra el estado HI. Otras alternativas son fijar las lneas de salida al valor 0 al 1. En la Fig. 1.7.b-d se muestran las distintas implementaciones de salida de una etapa tpica de un registro segn tenga salida condicional de uno u otro tipo, as como su descripcin RT.

qi

qi

qi

qi

& R zi zi Lectura incondicional zi = qi (a) Lectura condicional R = 0 zi = 0 R = 1 zi = qi (b) R

>1

R

zi

zi Lectura condicional R = 1 z i = qi R = 0 zi = 1 (c) Lectura condicional R = 0 zi = HI R = 1 zi = qi (d)

Figura 1.7: Implementaciones para la lectura sobre un registro

- Control. En general, un dispositivo-registro tendr un conjunto de seales de control (s) que seleccionarn cul de las operaciones posibles en el registro es la que se va a realizar. Cada vez que cierta funcin combinacional de las seales se haga verdadera, se realizar una operacin en particular. A nivel RT se escribe: f(s): operacin Para el manejo personal es muy til describir las actuaciones de control mediante una tabla, en la que para cada combinacin significativa de las seales de control se especifican todas las acciones secuenciales (escritura) como combinacionales (lectura). En muchos de los ejemplos que siguen se usa la descripcin mediante tablas ya que es muy clara de entender. Con mucha frecuencia cada operacin del registro es controlada por una nica seal que es activada cuando se desea ejecutar dicha operacin. En estos casos el nombre que se le da a la seal suele recordar la operacin que controla. En la tabla Tabla 1.2 se han representado algunos nombres frecuentes, casi siempre procedentes de la terminologa inglesa. As, para la carga en paralelo se usa W (Write), junto con T (Transfer) y L (Load). Para las operaciones de desplazamiento se usa S (Shift)

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

8

INTRODUCCIN A LOS SISTEMAS DIGITALES

junto con R (Right) si es a la derecha o L (Left) si es a la izquierda. Las operaciones tpicas del contador usan I (Increment) o UP y D (Decrement) o DOWN. El borrado o puesta a 0 usa CL (CLear) o Z (Zero), mientras que S (Set) indica la puesta a 1. La inhibicin ocurre si no se activa ninguna operacin, por lo que estar indicada cuando no hay ninguna seal de control activa; tambin se indica cuando no se activa la seal de seleccin de chip CS (Chip Selection) o de habilitacin EN (ENable) o cuando est activa la seal de deshabilitacin DIS (DISable). Por ltimo, para la lectura se suele usar R (Read). OperacinCarga en paralelo Desplazamiento derecha/izquierda Incrementa/Decrementa Puesta a 0/1 Inhibicin Lectura W (T,L) SR/SL I/D (UP/DOWN) CL, (Z) / S Ninguna seal activa (CS,EN,DIS) R

Seal de control

Tabla 1.2: Algunas seales frecuentes para controlar operaciones. A continuacin aplicaremos la descripcin de registros a nivel RT sobre diversos dispositivos como ejemplo. Ejemplo1. Descripcin de un registro de n bits bidireccional con carga en paralelo. Las figuras 1.8 y 1.9 muestran dos formas distintas del mismo registro: uno de n bits, con carga en paralelo y desplazamiento bidireccional con dos entradas de dato serie (DR y DL) y cuya lectura es incondicional. Su diferencia est nicamente en cmo se selecciona cada operacin.DR W SR SL CK n-1 n-1 DIN ... ... A[n] ... ... DOUT W SR SL 0 1 0 0 0 0 1 0 0 0 0 1 AA A DIN A SHR(A,DR) A SHL(A,DL) 1 0 1 0 DL

Escritura en AInhibicin Carga en paralelo Desplazamiento a la derecha Desplazamiento a la izquierda

Lectura de A

DOUT = A

Otras

Prohibidas

Figura 1.8: Registro del Ejemplo 1 con seal de control especfica para cada operacin

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

9

DR S1 S0 CK n-1 n-1

DIN ... ... A[n] ... ... DOUT 10 1 0

DL

S1 S0 0 0 1 1 0 1 0 1 AA A DIN A SHR(A,DR) A SHL(A,DL)

Escritura en AInhibicin Carga en paralelo Desplazamiento a la derecha Desplazamiento a la izquierda

Lectura de A

DOUT = A

Figura 1.9: Registro del Ejemplo1 con seales de seleccin de operacin mediante cdigo de valores.

En el caso de la Fig. 1.8 cada operacin sobre el registro lleva una seal de control asociada, de forma que cuando esta seal vale 1 se realiza la operacin correspondiente. Asmismo, como se prohibe la realizacin de ms de una operacin sobre el registro simultneamente entre las seales de control slo una podr tener el valor lgico 1 cada vez. Se dice a veces que, en este tipo de registros, las seales de control estn decodificadas. La situacin ninguna activa indica la inhibicin. La forma algebraica de describir el registro de la Fig. 1.8 a nivel RT, bajo las dos suposiciones ya comentadas (prohibir dos o ms seales activas y que la inhibicin es no activar seales), es: W: A DIN SR: A SHR(A,DR) SL: A SHL(A,DL) De forma anloga, pueden encontrarse dispositivos cuyas seales de control estn codificadas. Esto significa que, en cada combinacin binaria distinta de las seales de control S1, ..., Sm se realiza una operacin diferente sobre el registro, pudiendo estar ms de una seal de control activa simultneamente. As, cada operacin se ejecuta en un cdigo de entrada. De esta forma podr elegirse siempre el mnimo nmero de seales de control necesarias para codificar al nmero de operaciones distintas que se quieran realizar sobre el registro. En la Fig. 1.9 se aplica esta alternativa a un registro como el anterior (Fig. 1.8). Obsrvese que ahora slo se usan dos seales de control y que cada cdigo de dichas seales selecciona una operacin. De forma algebraica a nivel RT la descripcin ser: S1S0: A DIN S1S0: A SHR(A,DR) S1S0: A SHR(A,DL) donde hemos asumido que el cuarto cdigo (S1S0), al causar una no operacin (inhibicin), no es necesario explicitarlo.

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

10

INTRODUCCIN A LOS SISTEMAS DIGITALES

Ejemplo2. Descripcin de una RAM comercial: RAM 2114. Como segundo ejemplo de descripcin a nivel RT se presenta la de un dispositivo comercial relativamente complejo: el CI1 2114 (Fig. 1.10). Se trata de una RAM de 10 lneas de direccin, 4 lneas bidireccionales de datos, con una capacidad de 4096 bits (organizados como 1K 4) y con dos seales de control: una activa en baja para seleccionar el chip y la otra que controla si la operacin es de lectura de la RAM (R/W = 1) o de escritura en ella (R/W = 0). Obsrvese que el dato que se encuentra en las salidas D3-0 durante la lectura es el que se encuentra almacenado en la palabra de la RAM direccionada por las lneas de direccin A (A = A9:0). D = [RAM(A)] Como las lneas de datos D son bidireccionales, durante la operacin de escritura actan como entradas hacia la RAM portando el dato DIN a escribir, dato que habr situado otro circuito no contemplado aqu. El dato DIN se escribir en la palabra seleccionada por las lneas de direccin A que acta como registro en el que escribir: RAM(A) DIN entendiendo que el resto de registros de la RAM no cambian: RAM(B) RAM(B) De forma algebraica se escribir:

B A

CS R W : D = [RAM(A)] CS R W : RAM(A) DINentendiendo que los casos no especificados estn inhibidos (no hay cambio de datos y las salidas en HI).

A9:0 CS R/W

10

RAM 1K4 2114

4

D3:0

CS R/W 1 0 0 1 0

RAMRAM RAM RAM RAM RAM(A) D

D3-0 HI [RAM(A)] D3-0

Comentarios Lectura Escritura

Figura 1.10: Descripcin RT de la RAM 2114.

1. CI: Circuito Integrado

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

11

1.2.2 Operaciones de transferencias entre registros.La unidad de procesado de datos (Fig. 1.2-b) de un sistema digital genrico contiene varios registros interconectados entre s a travs de lneas conductoras y circuitos combinacionales. Como el propio nombre indica, a nivel RT la principal operacin dentro de dicha unidad es la transferencia entre registros, nombre con el que se denomina al movimiento y transformacin de datos desde uno o ms registros fuentes a un registro destino. En general, la descripcin a nivel RT de una transferencia entre registros se podra expresar de la siguiente forma:

f(x): A G(B, C, ...)

(1.1)

donde f(x) expresa la condicin que debe satisfacerse para realizar la transferencia, A es el registro destino del dato-resultado y G(B, C, ...) indica la operacin que se realiza sobre los datos fuentes. El sistema digital tiene que estar construido para poder realizar cualquiera de las transferencias entre registros que precise la solucin del problema a resolver. De aqu que haya una fuerte relacin entre las sentencias RT (ecuacin 1.1) y la realizacin del sistema digital. En lo que sigue estableceremos dicha realizacin. De la ecuacin 1.1 se entiende que los argumentos B, C, ... son registros que participan, mediante la operacin de lectura de sus datos, en la instruccin (registros fuentes). La funcin G es una funcin combinacional que maneja los datos almacenados en dichos registros (B, C, ...). En el registro A (registro destino) se realiza la carga en paralelo del dato resultante de la funcin G slo si la funcin f(x) tiene el valor lgico correcto. La funcin f(x) tiene carcter combinacional y su evaluacin corresponde a la Unidad de Control del Sistema Digital. Por tanto, para poder realizar una transferencia entre registros se necesitan una serie de requisitos: 1) de componentes, como son los propios registros y los dispositivos combinacionales para realizar las funciones f(x) y G; 2) de conexin, para el camino de los datos desde las fuentes hasta su destino y para las seales de control de todo el proceso; y 3) de organizacin, mediante la cual se realiza la distribucin de componentes y tareas, as como se hace el diseo arquitectural del sistema. En general son posibles muchas alternativas de solucin para el mismo problema.Control - Evala f(x) x - Genera seales de control - Establece secuencia de RT WA RB R B nb Unidad de datos

C

Circuito combinacional que realiza na G (B, C, ...)

nc...

W CKFigura 1.11: Sistema digital para la sentencia RT de la ecuacin 1.1.

A

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

12

INTRODUCCIN A LOS SISTEMAS DIGITALES

A modo de ejemplo, en la Fig. 1.11 aparece un sistema digital que permite ejecutar la sentencia RT de la ecuacin 1.1. El sistema digital est dividido en dos grandes bloques, la unidad de control y la de datos. La unidad de control se encarga, a partir de sus entradas x, de evaluar la funcin f(x) en cada momento. Si esta funcin toma el valor adecuado, deber hacer efectiva la transferencia entre registros en curso. Tras ello, la unidad de control debe saber qu nueva transferencia ha de ejecutarse a continuacin. Esto es, la unidad de control establece la secuencia de RT. Ntese que, por ser una operacin secuencial (escritura en registro) se realizar coincidiendo con un flanco activo de reloj Ck. De aqu que la unidad de control sea un circuito secuencial (mquina de estados finitos). Para llevar a cabo una transferencia, la unidad de control activar las seales necesarias en los componentes que participan en la transferencia. En la unidad de datos estn estos componentes junto con la ruta de datos adecuada para conectar las fuentes y el destino. Por ejemplo, en la Fig. 1.11 tanto el registro B (de nb bits) como el C (de nc bits) tienen sus salidas conectadas a las entradas del circuito combinacional que realiza la funcin G(B,C, ...). A su vez las salidas de ste estn conectadas a las na entradas de carga en paralelo del registro A. Dicho registro tiene una entrada de control de escritura (WA) que le es suministrada desde la unidad de control. El reloj de todo el sistema es nico, gobernando tanto los cambios de estado en la unidad de control como los instantes en que se almacenan los nuevos datos. Obsrvese que, en esta unidad de datos, el registro B posee salida triestado por lo que la lectura de B est controlada por la seal de lectura RB. La unidad de control debe generar tambin dicha seal RB. La Fig. 1.12 muestra cmo es la operacin en el tiempo. Se ha supuesto que la funcin G(B, C, ...) es simplemente la suma aritmtica de B y C y, para dar valores concretos, que inicialmente A = F1, B = 72 y C = 24. La Unidad de Control activa las seales RB y WA slo en el ciclo de reloj donde ha de ejecutarse la sentencia RT del ejemplo (A B + C). As, slo en ese ciclo las salidas de B muestran el contenido del registro B y, con ello, las salidas del bloque G muestran el valor deseado (96 = 72 + 24) que se sita por tanto como entrada de carga en paralelo del registro A. Como, adems, este registro tiene su entrada de escritura activada (WA = 1), cuando llega el flanco activo de reloj se produce la carga con lo que queda ejecutada la sentencia RT. Simultneamente la Unidad de Control habr cambiado al prximo estado en el que ejecutar la sentencia RT posterior.Ck RT anterior RB WA Salidas de B HI 24 ??? F1 72 24 72+24 = 96 F1 HI AB+C RT posterior

Salidas de C Salidas de G A

24 ??? 96

Figura 1.12: Diagrama temporal para ilustrar A B + C.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

13

Aunque tericamente son posibles transferencias entre registros muy complejas que involucran a mltiples datos, las de inters a nivel RT slo afectan a 1, 2, 3 registros. As, las transferencias entre registros a nivel RT pueden ser clasificadas en: Transferencias entre varios registros (tpicamente 2 3): - De movimiento de datos: - Aritmticas: A B + C - Lgicas: AB AB AB-1 AC

C

Estas transferncias exigen una ruta de datos entre los registros fuentes y el destino, ruta que incluye circuitos combinacionales y buses de interconexin. El registro destino operar en escritura y los fuentes en lectura. Si un registro es a la vez fuente y destino, como es el caso del Acumulador de los procesadores, deber estar diseado para que sea posible operar en lectura y en escritura simultneamente. Sobre un nico registro: - Desplazamiento: a derecha o a izquierda - Cuenta: ascendente o descendente - De inicializacin: tpicamente de Puesta a 0 o de Puesta a 1 Las transferencias de un nico registro no exigen ms que el registro tenga definida la operacin correspondiente.

Ejemplos. Transferencias condicionales entre registros y unidades de datos que las realizan. La Fig. 1.13 muestra cuatro ejemplos de transferencias entre registros cuando se cumplen las condiciones X1, X2, X3 y X4, respectivamente, junto con un posible circuito que realiza esa transferencia.X1: A B B ALU X1 W A B a b X2: A B C C.C. R B C X3=1

X3: A A - B - 1

a*b

A W

control

X4: A A + 1 X2 W A X4 I A

Figura 1.13: Algunas sentencias RT y posibles circuitos que las realizan.

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

14

INTRODUCCIN A LOS SISTEMAS DIGITALES

a) En el primer caso se mueve el dato de B (lectura incondicional) hacia A (escritura); b) en el segundo hay una operacin lgica XOR entre los datos de B y de C, que precisa la lectura del registro B pero no la de C; c) en el tercero hay dos aspectos de inters: 1) que el registro A es fuente y destino, y 2) que se ha usado una ALU para realizar la operacin aritmtica por lo que la seal X3 a travs del circuito combinacional CC, debe seleccionar la operacin adecuada en la ALU; d) en el cuarto caso el registro A es un contador ascendente simplemente.

1.3 TCNICAS DE INTERCONEXIN MEDIANTE BUSESLas operaciones bsicas a nivel RT son las transferencias entre registros. En un sistema digital genrico hay mltiples transferencias de unos registros a otros, siendo frecuente que un registro dado sea a veces emisor del dato (registro fuente) y otras, receptor de un resultado (registro destino). Surge as la necesidad de muy diversas rutas de datos. El sistema digital tiene que estar construido de forma que sean transitables todas las rutas de datos necesarias. Desde la perspectiva del hardware esto significa que el sistema deber estar dotado con la adecuada conexin entre los componentes almacenadores y procesadores de los datos (esto es, los registros y los bloques combinacionales). La presentacin de algunas tcnicas de interconexin es el propsito de este apartado para lo cual inicialmente se describirn los trminos bsicos relacionados con los buses de interconexin; a continuacin se considerarn las operaciones con los buses y, por ltimo, se presentarn algunos ejemplos tpicos de interconexiones entre registros. La entrada y salida de datos de los registros que lleva asociada una transferencia estndar utiliza los buses como principal va de interconexin. Entendemos por bus el conjunto de lneas de conexin entre dispositivos que se utiliza para transmitir informacin. Todas las lneas del bus son similares entre s salvo en el propio orden de cada lnea respecto a las dems. As, hay buses de lneas de direccin como son las usadas en los mapas de memoria, buses de datos externos a una CPU, buses de datos internos en una CPU, etc. La Fig. 1.14 muestra algunas de las representaciones habituales para un bus, denominado B, de n lneas . Siempre es conveniente explicitar el nombre y el nmero de lneas al representar un bus. Si se quiere aludir a una lnea concreta basta indicarlo subindicando el nombre del bus (por ejemplo, B3-5 alude a las lneas 3, 4 y 5 del bus B).

...

BUS

{

B0 B1

n B[n] = B0:n-1

n

Bn-1

Figura 1.14: Representacin del bus B de n lneas.

La clasificacin de los buses puede hacerse atendiendo a distintos conceptos, como son: Segn el sentido en el que fluye la informacin en el bus podemos distinguir: - buses unidireccionales: la informacin va en un nico sentido, de un registro fuente a uno o varios registros destino (Fig. 1.15.a). - buses bidireccionales: la informacin puede fluir en cualquier direccin. Cada registro

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

15

puede actuar de fuente o destino segn el caso (Fig. 1.15.b). Obsrvese que los terminales de los registros conectados a buses bidireccionales deben ser triestado para evitar colisiones entre los datos de entrada y de salida de cada registro.registro fuente n registro destino2 registro destino1 registro 1 n registro 2

...

...

(a)Figura 1.15: (a) Bus unidireccional. (b) Bus bidireccional.

(b)

Atendiendo a si la informacin que transmite el bus es compartida slo por dos registros o puede serlo por ms, podemos clasificar los buses en dedicados y compartidos (Fig. 1.16).

n n bus dedicado

Figura 1.16: Buses dedicado y compartido

bus compartido

Atendiendo ahora a las operaciones que se pueden realizar sobre un bus, stas son de lectura y de escritura. La operacin de lectura de un bus por parte de un registro lleva asociado el almacenamiento en el registro del dato que porta el bus. Para realizar esta accin debe existir, pues, un camino desde el bus a las lneas de entrada del registro y, a su vez, que se realice una operacin de escritura en el registro mediante la cual la informacin quede almacenada en l. Hay que tener precaucin con la terminologa ya que la lectura del bus es escritura en el registro. Para realizar la conexin necesaria que lleve a cabo esta operacin pueden plantearse dos circunstancias. En la primera un registro lee de un nico bus. La conexin del bus con las entradas en este caso es directa a travs de conductores (Fig. 1.17). De esta forma, cuando la seal de control de escritura del registro W est activa se realizar la operacin de carga en paralelo del dato ledo del bus.BUS: Bn-1:0 n nFigura 1.17: Conexin para la lectura de un nico bus

A W

Sin embargo, la lectura por parte del registro puede hacerse de ms de un bus. Para ello la circuitera debe permitir un camino de conexin entre cada uno de los diversos buses y las lneas de

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

16

INTRODUCCIN A LOS SISTEMAS DIGITALES

entrada del registro. Adems, para elegir en cada ocasin cul de entre los posibles buses va a ser ledo, se utilizarn unas seales de seleccin. Una solucin muy fcil es la del multiplexor, en la que sern n multiplexores los que permitan pasar de varios buses de entrada a uno en particular dependiendo de las entradas de seleccin (Fig. 1.18). Si hay k buses habr que utilizar como mnimo s seales de seleccin con k < 2s (por ejemplo, si k = 3 4, s = 2). Los n multiplexores tendrn k ms canales de entrada. Por su parte, la seal de control de escritura W del registro deber activarse con las k combinaciones vlidas de las seales de seleccin.BUS0: B0n-1:0 BUS1: B1n-1:0 BUS2: B2n-1:0 ...0 1 2 ...

n n n A W

n

lneas de seleccinFigura 1.18: Conexin para la lectura desde varios buses

Un mismo bus puede ser ledo simultneamente por mltiples registros sin que existan problemas a nivel lgico. As, por ejemplo, la Fig. 1.19 muestra un caso en que BUS1 es el nico bus que pueden leer los registros A, B, ..., mientras que el registro R tambin puede leer al BUS2. Si las seales de control poseen el valor indicado todos los registros leen BUS1 sobre el flanco activo de reloj. El nico problema que puede existir no es de tipo lgico sino de tipo elctrico; en concreto, que las lneas BUS1 tengan una carga superior al fan-out mximo en cuyo caso, adems de las lneas de conduccin, BUS1 deber incorporar buffers.BUS1 n ... S0 n WA CkFigura 1.19: Lectura de un bus nico por parte de diferentes registros1 0

BUS2 n

n WB B ... WR R

n

A

En cuanto a la operacin de escritura en bus, sta va asociada a la lectura de un registro: el dato almacenado en el registro al ser ledo, es el que se escribe en el bus. La operacin es BUS = [REGISTRO] En general, se pueden hacer consideraciones similares a las de la operacin de lectura de buses. Sin embargo hay una diferencia sustancial en cuanto a realizar la operacin simultneamente con mltiples registros: mientras que en el caso anterior (lectura de bus y escritura en registros) no existe problema a nivel lgico, ahora (escritura en bus y lectura de registro) en cada instante slo un registro puede poner sus datos en el bus para evitar colisiones de datos. Respecto a buses unidireccionales con un solo registro fuente se dan dos posiblilidades: 1) escritura en un nico bus, y 2) escritura en un determinado bus de entre varios (Fig. 1.20). En este ltimo caso, el bus concreto se selecciona mediante un demultiplexor. Dado que la informacin procede de un nico registro de donde se lee, es suficiente con que este dispositivo tenga lneas de salida estndares,

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

17

BUS0 BUS1 BUS2 n A n A 0 1 2 ... n n n

n

n

W ...

lneas de seleccin

Figura 1.20: Conexin para la escritura en un bus usando buses unidireccionales

sin necesidad de buffers triestado. En el caso en el que los buses utilizados sean bidireccionales y, en general, cuando haya dos o ms dispositivos que puedan escribir sobre el mismo bus, la conexin para poder realizar escritura en un bus se muestra en la Fig. 1.21 . Puede comprobarse que en este caso, como diversos registros pueden escribir en un mismo bus, estos registros necesitan lneas de salidas con buffers triestado, de forma que cuando no se est leyendo el contenido de un registro ste tendr su salida en HI y as, no entrar en conflicto con otros contenidos que pueden estar presentes en ese momento en el bus. Por tanto una restriccin de operacin es que slo se puede realizar la lectura de un nico registro en cada ocasin. As, en el circuito de la Fig. 1.21 slo una seal de lectura (RA1, RA2 RA3) puede estar activa en cada instante.n n n n

A1

A2

A3

...

WA1 RA1

WA2 RA2

WA3 RA3

Figura 1.21: Operacin de escritura en un bus usando buses bidireccionales

Ejemplo de interconexin: Se pretende determinar el interconexionado que se requiere para poder intercambiar informacin entre cuatro registros cualesquiera. Sean A0, A1, A2 y A3 dichos registros. A nivel RT, la operacin a realizar se puede expresar como A D AF donde con AD se indica el registro destino y con AF el fuente, y cualquiera de los dos papeles puede ser asignado a cualquiera de los cuatro registros del problema. Para elegir el que actuar como registro destino de la transferencia se dispone de dos lneas D1 y D0, de forma que cada una de las cuatro combinaciones binarias de dichas variables selecciona a un nico registro. De forma anloga, las lneas F1 y F0 determinarn el registro fuente. Para resolver el problema se presentarn tres estrategias de conexionado distintas, cada una de las cuales relacionar un tipo de bus y un tipo de registro. Las tres soluciones son:C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

18

INTRODUCCIN A LOS SISTEMAS DIGITALES

- Solucin multiplexada; registros con terminales de entrada I y de salida O separados. - Solucin con bus compartido; registros con terminales de entrada I y de salida O separados pero con salidas triestado. - Solucin con un nico bus compartido bidireccional; registros con terminales de entrada/salida I/O. En la primera solucin al problema (Fig. 1.22) se usa un multiplexor a travs del cual se realiza la escritura en el bus unidireccional de entrada BI del dato surgido en la operacin de lectura de los distintos registros. Con esta forma de conexionado, los registros vierten su contenido a buses dedicados diferentes, terminando cada uno de ellos en uno de los canales de entrada de los multiplexores. Para elegir el registro fuente las lneas F1 y F0 controlarn las entradas de seleccin del multiplexor. De esta forma, segn la combinacin binaria que tengan estas seales slo el contenido del registro apuntado pasar a la salida del multiplexor. Las salidas de ste irn conectadas al bus BI, a su vez directamente conectado con las lneas de entrada de los registros. Slo aquel que acta de registro destino ver activa su seal de control de escritura WD, con lo que ser el nico que realizar la operacin de lectura del bus BI y cargar el contenido que en l hubiera. La eleccin del registro destino la realizar un circuito combinacional, en este caso un decodificador 2:4, de forma que cada una de sus cuatro lneas de salida va conectada a la lnea de control de escritura del correspondiente registro.D1 D0 1 0 3 2 1 0 W BI F1 F0 n n A0 B01 0

DEC 2 : 4 W n A1 B1 0 2 1 n MUX 4 : 1 W n A2 B2 3 W n B3 A3

Figura 1.22: Ejemplo de interconexin mediante multiplexado

En la segunda solucin que presentamos Fig. 1.23 los registros poseen terminales de entrada I y de salida O separados, estos ltimos salidas triestados. Todos los registros vierten su contenido a un nico bus interno, BINT, compartido por todos ellos. Debido a este hecho, los registros necesitan disponer de salida tipo tres-estados con la correspondiente seal de control para la lectura. De esta forma, el registro que tenga activa su seal de control para lectura, volcar su contenido en el bus. Si por el contrario tuviera dicha seal desactivada las lneas de salida se encontraran en estado de alta impedancia no afectando, pues, al dato escrito por el registro fuente. La restriccin de que una y slo una de las seales de lectura de los registros puede estar activa en cada ocasin, se cumple en este circuito al generarse las seales de lectura mediante un decodificador 2:4 de la seales F1 F0. De esta forma, segn la combinacin de estas dos seales, slo una de las salidas del decodificador se activa. Dado que cada una de ellas se conecta con la seal de lectura R de un registro, se garantiza as que slo se lee de uno, el que ser el registro fuente. De forma anloga al caso anterior, para determinar el registro destino de la transferencia, se usar tambin un decodificador 2:4 que decodifica el valor de D1 D0, determinando as cul de las seales de escritura W de los registros est activa. Aqul registro que tenga dicha seal activa ser el que acte como registro destino.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

19

D1 D0

1 0 DEC 2 : 4

3 2 1 0

BINT n F1 F0 0 1 2 3

W R n

A0

W A R 1 n

W R A2 n

W A R 3 n

1 0 DEC 2 : 4

Figura 1.23: Ejemplo de transferencia entre registros con terminales separados de entrada y salida y bus compartido.

Por ltimo, en la tercera solucin al problema se utiliza un bus compartido bidireccional. Los registros tienen terminales de entrada/salida y dos seales de control (R, W) para poder realizar adecuadamente las operaciones de lectura y escritura. Al igual que en la solucin anterior, dado que el bus es compartido por todos los registros, en cada momento slo puede realizarse la operacin de lectura sobre uno de ellos. Para llevar a cabo la transferencia de informacin, la eleccin de los registros fuente y destino se realiza tambin mediante dos decodificadores 2:4 uno con entradas D1 D0 y el otro con F1 F0. Con estos decodificadores se controla la activacin del grupo de lneas de lectura (para determinar el registro fuente) y de escritura (para seleccionar el registro destino).D1 D0 1 0 DEC 2 : 4 3 2 1 0

W A R 0 n

W A R 1 n

W A R 2 n

W A R 3 n

F1 F0

1 0 DEC 2 : 4

0 1 2 3

Figura 1.24: Ejemplo de conexin entre registros mediante bus nico

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

20

INTRODUCCIN A LOS SISTEMAS DIGITALES

1.4 REALIZACIN DE SISTEMAS DIGITALESEn este apartado se aborda la tarea de diseo de un sistema digital. Debido a que un sistema digital se organiza mediante la unin de dos grandes bloques, la unidad de procesado de datos y la unidad de control, la tarea de diseo es en realidad doble, una por cada una de estas unidades. En general, cada sistema podr ejecutar una serie de instrucciones, llamadas tambin macrooperaciones. Por una parte, la unidad de procesado deber estar construida posibilitando todas las transferencias entre registros que se necesitan para realizar las operaciones de datos exigidas por las macrooperaciones. Por otra parte, la unidad de control se realizar para que ejerza el gobierno adecuado en la activacin de la unidad de datos: direccin de la secuencia, generacin de seales, etc. El diseo de sistemas digitales es una tarea compleja para la que no existe ningn mtodo sistemtico eficaz, por lo que la experiencia del diseador se convierte en un parmetro de suma eficacia, prcticamente decisivo. Al ser ste un captulo de introduccin al diseo de los sistemas digitales, nuestro principal propsito es aportar experiencia de diseo, ms que discutir tcnicas avanzadas, problemas de optimizacin, etc. Con el fin de aportar esa experiencia, en el desarrollo del tema utilizaremos un ejemplo sobre el cual se presentarn los principales conceptos de la realizacin de sistemas. Este ejemplo es simple pero posee gran valor en tanto que se utilizar en ste y en los siguientes captulos. Adems de desarrollar los aspectos concretos del ejemplo, en este apartado tambin realizaremos una aproximacin a la generalizacin sobre el proceso de diseo. El punto de partida suele ser una especificacin verbal ms o menos detallada. As, nuestro ejemplo de sistema digital ser una calculadora de sumas y restas. Este sistema realiza distintas operaciones entre dos datos A y B que estn almacenados en sendos registros. El resultado de la operacin se almacena en uno de estos dos registros. El primer paso del proceso de diseo consiste en especificar el sistema a alto nivel. Se trata de definir, con el mayor rigor y formalidad posibles, las caractersticas generales y globales del sistema, en concreto: - cul es la arquitectura u organizacin del sistema en trminos de grandes bloques funcionales. - cul es el conjunto de macrooperaciones o instrucciones que el sistema va a entender y a ejecutar. Esto se denomina describirlo a nivel ISP (Instruction Set Processor). - cul es el modo de ejecucin de esas instrucciones desde la perspectiva del usuario. Aqu se trata de establecer qu es lo que el usuario debe hacer y qu es lo que el sistema realizar automticamente. Comenzamos, pues, definiendo nuestro sistema en alto nivel. Para ello presentamos el conjunto de instrucciones (nivel ISP) que, en este caso, ser un conjunto de ocho instrucciones distintas (cada una de ellas es una macrooperacin). AA+B A-A+B BA+B B-A+B AA-B A-A-B BA-B B-A-B

En nuestro nivel la organizacin bsica de un sistema es la de la Fig. 1.2-b. Adems, tras la definicin a nivel ISP sabemos que, en nuestro caso, para llevar a cabo este conjunto de macrooperaciones se necesitar una unidad de datos en donde al menos se disponga de los dos registros donde estn almacenados A y B. En la Fig. 1.25 se muestra, a nivel de bloques, la organizacin del sistema.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

21

XS

FIN

A

B IR[3] 3 Control n Z Unidad de procesado

usuarioFigura 1.25: Organizacin del sistema digital ejemplo

sistema digital

A continuacin describiremos el modo de operacin sistema-usuario. El usuario que opera con el sistema se comunica con l mediante una serie de seales. Con un pulso positivo en la entrada Xs se ordena al sistema que ejecute una de las instrucciones. La seleccin de la misma se realiza mediante el registro de instrucciones IR (Instruction Register). En nuestro ejemplo (Fig. 1.25), se trata de un dispositivo de tres bits y, dependiendo de la combinacin binaria que en l escriba el usuario ste comunica al sistema cul de las ocho macrooperaciones se ha de realizar. Con esta informacin el sistema pasa a realizar la secuencia de acciones necesarias para llegar al resultado final. En el momento de finalizar la ejecucin se activa la seal de FIN y se regresa a un estado de espera aguardando una nueva seal de comienzo. De esta forma el usuario podra proceder a repetir los pasos dados (1o, escritura del cdigo en IR; 2o, activacin de XS) para conseguir llevar a cabo una nueva operacin. Para continuar con el desarrollo del sistema, es necesario realizar su especificacin a nivel RT, lo que conlleva un doble proceso fuertemente acoplado: por una parte hay que traducir las instrucciones ISP a operaciones de transferencia de datos y, por otra, hay que disear una unidad de datos que permita ejecutar todas esas transferencias. En general, las macrooperaciones realizadas por un sistema digital se llevan a cabo mediante una secuencia de operaciones de transferencia entre registros. El conjunto de transferencias a nivel RT que se realizan en un mismo ciclo de reloj se llama microoperacin (op). Una op puede consistir en una, en dos, en tres, ..., transferencias entre registros distintas; en el caso lmite, en ninguna, llamndose entonces No-OPeracin (NOP). Lo que caracteriza a una op es que se realiza en un solo ciclo de reloj. Con ello, cada macrooperacin del sistema ser equivalente a una secuencia de microoperaciones, cada una de ellas realizadas en un ciclo de reloj (Fig. 1.26). El conjunto de microoperaciones de que consta una determinada macrooperacin est ntimamente relacionado con la unidad de procesado del sistema. Esto quiere decir que la misma macrooperacin precisar ms o menos microoperaciones, dependiendo de cul sea el diseo de la unidad de procesado. Por ejemplo, la macrooperacin A A+B del sistema de ejemplo se realizar con cuatro microoperaciones para la unidad que utilizaremos (Fig. 1.28), mientras que en la unidad de la Fig. 1.27 se realizara con slo una microoperacin. La relacin macrooperacin/microoperacin/unidad de procesado pone de manifiesto la gran importancia de esta fase del proceso de diseo. Hablando en trminos ms precisos, cada unidad de

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

22

INTRODUCCIN A LOS SISTEMAS DIGITALES

Nivel ISP

Instruccin K

macro-operacin

RT1 Nivel RT RT2 RT3 ... RTNFigura 1.26: Relacin entre macrooperacin y microoperacin

micro-operaciones

procesado proporciona un conjunto de primitivas RT (que son las microoperaciones realizables en esa unidad) con las cuales hay que obtener el algoritmo de realizacin de las macrooperaciones. En un proceso de diseo genrico, la conversin desde macrooperacin a secuencia de microoperaciones (Fig. 1.26) va imponiendo unos componentes determinados a la Unidad de Datos (para que cada microoperacin sea, de hecho, una primitiva RT). En cada instante del proceso, adems, el conjunto de primitivas ya disponibles en la Unidad de Datos permite corregir la traduccin desde la macrooperacin hasta su secuencia de ops. De esta forma, esta fase de diseo obliga a ir teniendo en cuenta tanto el algoritmo de traduccin de la macrooperacin como el diseo de la Unidad de Datos con componentes RT.

B

a a+b

b

s r

AFigura 1.27: Unidad para A A+B en una op

W

1

Llevar a cabo adecuadamente esta doble tarea es ciertamente difcil, siendo sta la fase en la que se necesita gran experiencia. De aqu que en el desarrollo que sigue no afrontemos esta etapa de diseo sino que, sin disearla, propondremos una unidad de datos vlida para nuestro sistema. Antes de continuar sealemos otra relacin de gran inters que se produce al considerar el dominio temporal y que permite conectar las unidades de datos y de control. El tiempo viene caracterizado por los ciclos de reloj. En cada ciclo, por una parte se ejecuta una op en la unidad de datos y, por otra, la unidad de control est en un estado. Entonces, la funcionalidad de la unidad de control en ese estado aparece de forma clara:

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

23

1. durante ese estado deber activar las entradas de control involucradas en la ejecucin de la op en la unidad de datos; 2. cuando ocurra la transicin al siguiente ciclo, debe cambiar al estado que corresponda a la siguiente op de la secuencia. La Unidad de Control es, pues, una mquina de estados en la que su secuencia de estados sigue a la secuencia de ops y sus salidas activan las seales de control de los dispositivos de la Unidad de Datos. Para nuestro ejemplo, la unidad de procesado adoptada ser ampliamente descrita y apoyndonos en ella se desarrollar cada macro-operacin. La descripcin grfica de nuestra unidad de datos es la presentada en la Fig. 1.28.

DB Todo de n bits T

WT A RA WA

a ab [AC] AC

b

s r B RB WB RAC WAC ZAC

RA

WA

Figura 1.28: Unidad de procesado de una calculadora de sumas y restas

En la Fig. 1.28 pueden apreciarse dos grandes bloques separados por un bus interno de datos (DB) compartido por varios dispositivos. En la parte derecha del bus hay dos elementos de memoria, registros A y B, donde se almacenan los datos de nuestro problema. En la parte izquierda del bus es donde estn el resto de los dispositivos que nos servirn para llevar a cabo cada una de las macrooperaciones del sistema. Como se observa, esta subunidad consta de: un registro T que lee datos del bus DB y que suministra uno de los operandos; un sumador-restador entre el contenido del acumulador AC y del registro T; un registro acumulador AC que almacena los resultados de la operacin y, en su caso, los transfiere al bus DB. La unidad de procesado dispondr de dispositivos de n bits y, as mismo, todos

RB WB

UNIDAD DE PROCESADO

WT

s

r

RAC

WAC

ZAC

(del controlador)

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

24

INTRODUCCIN A LOS SISTEMAS DIGITALES

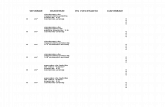

los buses tendrn igualmente esa dimensin. En cuanto a los buses, los hay de diversos tipos. Uno de ellos, el bus DB, es un bus compartido que es a travs del cual se pasa la informacin de una parte a otra dentro de la unidad de datos. En la Fig. 1.28 aparece dibujado con trazo fuerte. Los otros, en trazo dbil, son buses dedicados cada uno comunicando dos dispositivos entre s nicamente. El paso siguiente a la descripcin grfica de nuestro sistema es la descripcin detallada de cada uno de sus dispositivos. Esta descripcin debe ser lo ms formal y rigurosa posible y, para ello, de cada uno se dar su tabla de comportamiento a nivel RT. La descripcin de los registros A y B se representa en la tabla de la Fig. 1.29. Cada uno dispone de dos seales de control, una de escritura WX y otra de lectura RX, dado que su salida est conectada a un bus compartido por otros dispositivos. Su comunicacin con el bus interno de la unidad es mediante un bus bidireccional por lo que la activacin simultnea de las lneas de lectura y escritura est prohibida.RX 0 DD X RX WX 0 1 1Figura 1.29: Descripcin de componentes de la unidad de procesado. Los registros A y B

WX 0 1 0 1

X X DD X

DD = HI entrada [X]

De forma similar se describe el registro T (registro tampn). Como se ve en la Fig. 1.30, el registro T, cuya misin ser almacenar datos temporalmente, posee dos buses separados, uno de entrada y otro de salida. El dispositivo dispone de una nica seal de control, la de escritura WT, y su contenido siempre est presente en el bus de salida, es decir, es un registro con lectura incondicional.IN WT T WT 0 1 T T IN OUT = [T] [T]

Figura 1.30: Descripcin de componentes de la unidad de procesado. El registro tampn.

El dispositivo AC es el registro acumulador. Este es el registro en donde se vierten los resultados de las operaciones realizadas por el sumador restador. Como se refleja en la Fig. 1.31, el registro acumulador dispone de un bus de entrada y dos buses de salidas. Uno de ellos, OUT1, es el que vierte su contenido nuevamente a una de las entradas de datos del sumador-restador. Es un bus dedicado, por tanto en l siempre est presente el contenido del acumulador, es decir, el acceso al dato almacenado en AC va OUT1 es incondicional. El otro bus de salida, OUT2, se conecta al bus interno compartido de la unidad de datos, DB. Por tanto, el registro tendr una seal de control de lectura, RAC, y slo cuando sta est activa se podr acceder al dato almacenado en el acumulador a travs de OUT2. Las otras lneas de control del dispositivo son las de escritura (WAC) y la de puesta a cero (ZAC). Mediante la activacin de esta ltima seal, se logra hacer un clear sobre el contenido del registro, consiguiendo el dato 0 0....0.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

Prohibida

OUT

INTRODUCCIN

25

IN RAC WAC ZAC

ZAC 0 1 0 0

RAC 0 0 1 0 Otras

WAC 0 0 0 1

AC AC 0 AC IN

Figura 1.31: Descripcin de componentes de la unidad de procesado. El registro acumulador

Por ltimo describiremos el subsistema sumador-restador (que, en general, podra ser una ALU). Este componente combinacional tendr dos seales de control, s y r, que especifican si la operacin llevada a cabo es una suma de los datos de entrada o una resta. En la (Fig. 1.32) se muestra su diagrama de bloque y su comportamiento. (Ni el valor sr = 00 ni sr = 11 tienen significado por lo que ambos no importan; sin embargo como sr = 11 indicara que se ordenan dos acciones incompatibles, este valor se prohibe).IN1 IN2 s 0 a ab b s r 0 1 1 OUTFigura 1.32: Descripcin de componentes de la unidad de procesado. La ALU.

Una vez descritos todos los componentes de nuestra unidad de datos del sistema del ejemplo, el siguiente paso ser encontrar para cada macrooperacin el conjunto de microoperaciones que la realizan. En la Fig. 1.33 se presenta una tabla en donde cada una de las macrooperaciones del sistema es desarrollada en sus microoperaciones. Obsrvese que se ha intentado compartir al mximo las microoperaciones entre las distintas instrucciones del sistema. De esta forma se simplifica la descripcin del comportamiento de nuestro sistema como se ver en el siguiente apartado y se reflejar igualmente en un mejor diseo de la unidad de control, lo que se tratar en el siguiente tema. A modo de ejemplo se comenta detalladamente los pasos dados para desarrollar una macrooperacin, en este caso +. Se pretende cargar en el registro A el resultado de la suma de los datos A y B. Para ello se tiene la necesidad de llevar ambos datos a las dos entradas de la ALU, ya que es ella la que realiza la operacin de suma. Una vez realizado esto, se le dir a la ALU que sume ambos datos llevndose este resultado al registro A que acta en este caso como registro destino. En la unidad

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

OUT2 OUT1 = [AC] [AC] [AC] [AC] Prohibidas r 0 1 0 1

OUT1

AC

OUT2 = HI HI [AC] HI

OUT = No importa IN1 IN2 IN1 + IN2 Prohibida

26

INTRODUCCIN A LOS SISTEMAS DIGITALES

de datos de nuestro sistema (Fig. 1.28) las lneas de entrada de la ALU provienen del registro tampn T y del registro acumulador AC. Por tanto, sern esos dos registros los que tengan que recibir los datos A y B para que puedan ser sumados. El registro acumulador en nuestra arquitectura slo recibe los datos de las lneas de salida de la ALU. Por tanto, si queremos que uno de los datos iniciales, por ejemplo A, sea cargado en el acumulador, tendr que ser como resultado de una operacin con la ALU, en nuestro caso, mediante la de suma del dato con cero. Para ello inicialmente habr que efectuar dos transferencias entre registros: - poner a 0 el registro acumulador, lo que es posible activando la seal ZAC (Fig. 1.28); - escribir el dato A en el registro T, lo que es posible leyendo A y escribiendo en T (esto, es activando RA y WT). Ambas transferencias pueden ser realizadas simultneamente en el mismo ciclo de reloj y constituyen la primera microoperacin: 1. C 0, A continuacin, como cuando empiece el ciclo de reloj siguiente ya se han efectuado todas las transferencias entre registros ordenadas en el ciclo anterior ya estamos en disposicin de realizar una operacin de suma con la ALU, dado que los datos que sumar, A y cero, ya estn en los registros adecuados. Adems, en este mismo ciclo de reloj se puede ir adelantando una nueva transferencia RT consistente en grabar el dato B en el registro T, De esta forma, cuando empiece un nuevo ciclo de reloj ya se tendr al dato B en el registro T y al dato A en el acumulador. Ambas transferencias pueden realizarse en el mismo ciclo ya que el camino utilizado para cada una de ellas es distinto y constituyen la segunda microoperacin: 2. B , C AC+T En el tercer ciclo de reloj se efectuar de nuevo una suma con los datos existentes en ese momento en el registro T (dato B) y en el acumulador (dato A), almacenndose el resultado (A+B) en el acumulador. As, la tercera microoperacin es: 3. C AC+T Por ltimo, en el cuarto ciclo de reloj, una vez que ha sido grabado en el acumulador el resultado de la suma de A con B, ste se manda al registro destino, en este caso el registro A. Dado que ambos registros estn comunicados por el bus interno DB, la operacin a realizar es simplemente un movimiento de datos de un registro a otro. Con ello, se tiene la cuarta y ltima microoperacin. 4. C De esta forma, en cuatro ciclos de reloj, cuatro microoperaciones, se ha conseguido realizar con esta unidad de datos la primera de las macrooperaciones del sistema del ejemplo. De forma anloga se procedera con las restantes. Tras haber desarrollado separadamente cada macrooperacin en sus microoperaciones, el siguiente paso que hay que dar es ensamblarlas y depurarlas con el fin de obtener un nico conjunto de microoperaciones. En su obtencin normalmente se persigue compartir el mayor nmero posible de microoperaciones entre distintas macrooperaciones. De esta forma suele reducirse la unidad de control. En nuestro ejemplo, la Fig. 1.33 ya recoge en buena parte cmo se comparten: por ejemplo la primera op es comn a las ocho instrucciones, en la cuarta slo hay dos ops distintas (cada una compartida por cuatro instrucciones), etc.

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

27

OP 1 2 3 4

A A+B

B A+B

A A-B

B A-B

C0, B , CAC+T CAC+T C C CAC-T C C

OP 1 2 3 4

A(-A)+B

B(-A)+B

A(-A)-B

B(-A)-B

C0, B , CAC-T CAC+T C C CAC-T C C

Figura 1.33: Conjunto de microoperaciones del sistema del ejemplo

En general, sin embargo, tablas como la de la Fig. 1.33 no reflejan adecuadamente la secuencia de microoperaciones que forman el algoritmo global del sistema. Como veremos prximamente, existen otras formas de representar el algoritmo global, formas que dan una imagen mucho ms descriptiva de cmo opera el sistema entero. Esas formas de representacin deben permitir, adems, describir adecuadamente la secuencia de microoperaciones no slo bajo la perspectiva de procesamiento de datos, que es como est en la Fig. 1.33, sino tambin bajo la perspectiva del controlador; esto es, hace falta describir la secuencia en que se han de ir activando las diferentes seales de control de los registros y subsistemas que componen la unidad de datos. Continuando con el proceso de diseo genrico, una vez descritos los microprogramas de datos y de control, hay que realizar el diseo de las unidades correspondientes. Para ello, en el caso de la Unidad de Procesado de Datos habr que elegir el hardware concreto que se utilizar. En el caso de la Unidad de Control se aplicarn tcnicas de diseo que, en nuestro caso, se tratarn en el siguiente captulo. El ltimo paso del proceso de diseo consiste en implementar el sistema y verificar que opera correctamente. Antes de proseguir queremos prestar atencin a un aspecto que, aunque siempre importante, lo es mucho ms en los Sistemas Digitales. Nos referimos al uso de formas de descripcin adecuadas. En los Sistemas Digitales la utilidad es doble: - en el propio proceso de diseo, ya que lo hace ms fcil y directo y, adems, reduce mucho el tiempo de localizacin de posibles errores; - en la documentacin que obligadamente acompaa a sistemas de esta complejidad, ya que las formas de descripcin adecuadas constituyen normalmente la parte ms inequvoca, precisa y clara de documentacin.

C. Baena, J.I. Escudero, I. Gmez y M. Valencia. 1997-2008

28

INTRODUCCIN A LOS SISTEMAS DIGITALES

Los principales puntos a describir cuidadosamente son: el sistema digital globalmente, la Unidad de Datos (registros, buses) y la de Control, y los microprogramas de datos y de Control. Todos estos puntos deben ser descritos desde al menos dos puntos de vista: - estructural o de circuito, esto es, indicando qu componentes tiene y cmo se conectan entre s; - funcional o de comportamiento, esto es, explicando qu operaciones realiza y como lo hace. En esta obra, en la que nos centramos en el nivel RT, se utilizarn esencialmente dos formas de descripcin rigurosas: - Las de tipo grfico, que a su vez pueden desglosarse en otras dos: - Las orientadas al nivel estructural: son los diagramas de bloques y de circuitos tales como los de las Figuras 1.25 y 1.28. - Las orientadas al nivel funcional: son las denominadas cartas ASM (Algorithmic State Machine) que presentaremos en el siguiente apartado. - Las de tipo lenguaje. Generalmente se trata de unos lenguajes de programacin, ms o menos especficos para describir circuitos y que reciben el nombre de HDL (Hardware Description Language). Nosotros utilizaremos un HDL muy simple, que se explicar ms adelante. Por ltimo, dada la importancia y complejidad de la materia tratada en este apartado, vamos a hacer un resumen sobre el diseo de Sistemas Digitales. En primer lugar, recordar que la experiencia como diseador es determinante para lograr un buen producto1 y, a veces, incluso para obtener un sistema que simplemente funcione. De aqu que sea muy importante adquirir experiencia. Incluso con experiencia suficiente, el diseo debe efectuarse bajo las siguientes guas: - Afrontar el diseo siguiendo una metodologa. Quiz la mejor metodologa sea la denominada top-down (desde arriba hacia abajo) que concretamos tras estas guas. - Dividir con claridad el sistema entre la parte de procesado de datos y la de control. - Desarrollar la arquitectura de la unidad de procesado y el microprograma (de datos y de control) antes de elegir los dispositivos de hardware concretos. - Utilizar con rigor las formas de descripcin adecuadas y documentar bien todo el proceso. En cuanto a la aplicacin de la metodologa top-down al diseo de sistemas digitales, los principales pasos a seguir son: 1. Especificar el sistema globalmente a alto nivel; en concreto, - su conjunto de instrucciones (ISP) - su modo de operacin (uso y ejecucin) 2. Para cada instruccin (macrooperacin) obtener un algoritmo con primitivas RT (secuencia de microoperaciones) que la realice. 3. Ensamblar y depurar todos los algoritmos de las instrucciones del sistema para obtener: - un nico microprograma de datos y una Unidad de Procesado que pueda ejecutar todas las primitivas utilizadas en l, (en su caso, regresar al punto 2 para modificar lo que corres1. EN esto , el diseador puede crear elegancia y belleza o quebraderos de cabeza y caos. [Pros87].

Dpto. Tecnologa Electrnica. Universidad de Sevilla

INTRODUCCIN

29

ponda) - el microprograma de control asociado. 4. Realizar la Unidad de Procesado y de Control. 5. Implementar y verificar.

1.5 CARTAS ASMLas cartas ASM(Algorithmic State Machine) son formas de descripcin de tipo grfico especialmente enfocadas, como indica su nombre, a representar algoritmos secuenciales. Se trata de una herramienta prcticamente idnea para la materia que estamos estudiando puesto que: - El desarrollo de macrooperaciones en microoperaciones es un proceso algortmico secuencial, por lo que la descripcin de Sistemas Digitales a nivel RT cae plenamente dentro de la materia representada con cartas ASM. - Es una herramienta que da informacin sobre la estructura y sobre el comportamiento dinmico del sistema que se describe con ella, aspectos ambos de sumo inters. - La carta ASM proporciona informacin tanto del algoritmo con los datos como de la secuencia de control, por lo que la propia herramienta est muy prxima a las implementaciones hardware de las Unidades de Datos y de Control. - Se trata de una herramienta muy intuitiva, fcil de aprender y muy adecuada para trabajar a mano. - La herramienta tiende un doble puente: 1) hacia niveles de abstraccin ms bajos, en concreto con los modelos de mquinas de estado que son tan tiles a nivel de conmutacin; y 2) hacia niveles ms abstractos, como con la representacin mediante grafos de flujo de programas a nivel ISP. El propsito de este apartado es presentar las cartas ASM con un cierto nivel de detalle, con el fin de que el lector pueda utilizarlas adecuadamente de manera inmediata. Para ello, en sucesivos epgrafes mostraremos: sus definiciones bsicas, su relacin con las tablas de estado (de Moore y de Mealy), diferentes ejemplos de uso en los que se detallarn algunos errores comunes que se cometen al construir cartas ASM, se considerar cmo est contemplada la dimensin temporal en ellas y, por ltimo, regresaremos al ejemplo de sistema digital cuyo diseo iniciamos en el apartado anterior para describirlo con cartas ASM.

1.5.1 DefinicionesLos trminos particulares que vamos a definir se refieren a los componentes primarios (o cajas de estado, de decisin y de accin condicional), a la celda bsica (llamada bloque ASM) y al ente global (o carta ASM). Una carta ASM es un grafo orientado y cerrado compuesto por un nmero variable de bloques ASM interconectados entre s. Un bloque ASM que es equivalente a lo que se entenda como un estado en las mquinas de estado finito corresponde a todas aquellas acciones que tengan lugar en un mismo ciclo de reloj y sus componentes bsicos son: - caja de estado