Pdls

-

Upload

alejandra-hernandez -

Category

Documents

-

view

243 -

download

0

description

Transcript of Pdls

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

PDL´sDEFINICIÓN: Se entiende como un dispositivo lógico programable o PLD

(Program Logic Device) a un circuito integrado, con capacidad de ser

programado por el usuario para implementar cualquier tipo de sistema

combinacional y/o secuencial.

CATACTERÍSTICAS.

Las características más importantes de los diseños que usan PLD son:

1. Menor número de componentes

Permiten realizar sistemas complejos en un único circuito integrado en lugar de

utilizar varios circuitos interconectados lo que reduce el número de

componentes.

Las consecuencias de esta reducción de componentes son:

a) Reduce complejidad y tamaño del circuito impreso que soporta el

sistema digital.

b) Disminuye el número de puntos de soldadura, consiguiendo mayor

fiabilidad e inmunidad al ruido.

c) Menor tiempo de programación, por estar los componentes en el mismo

C.I.

Al reducir el número de componentes facilita la gestión de almacén.

2. Programabilidad

Otra de las características de los PDL es su Programabilidad: permite cambiar

o reconfigurar el diseño sin tener que modificar el cableado del circuito.

3. Difícil de copiar

Como última característica a resaltar es la dificultad de su copia, de esta forma

protege la propiedad del diseño.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

Limitaciones: Como requisitos de uso hay que mencionar que:

Hace falta herramientas de diseño que pueden ser costosas, por lo que resulta

rentable solo cuando el número de diseños o de ejemplares vaya a ser

elevado.

Arquitectura de las PDL

La arquitectura básica de un dispositivo lógico programable está formada a

base de elementos digitales con múltiples conexiones entre ellos.

Existen diversos tipos de PLD cada uno con una arquitectura distinta, pero su

estructura general está formada a base de bloques característicos que la

mayoría de los PDL lo utilizan. La estructura básica está formada por los

siguientes bloques:

Un buffer de entradas donde se obtienen cada entrada de forma directa y

complementaria. Estas entradas atacan a una matriz AND donde se obtienen

términos productos que, a su vez, atacan a una matriz OR donde, a su salida,

se obtienen las funciones en forma de suma de productos.

Esta estructura está encaminada ha obtener en los terminales de salida

expresiones lógicas combinacionales, en función de las entradas en forma de

suma de productos.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

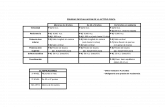

CLASIFICACION ENTRE ARQUITECTURAS DE LOS PLD’s

La clasificación de los PLD’s, como se mencionó anteriormente, dependerá

básicamente del plano o los planos que sean programables.

La clasificación se hace en tres grupos:

ROM. Mask Read-Only Memory (Memoria de Máscara Programable de Solo

Lectura), Dispositivo programado solamente por el fabricante y como se

muestra en el esquema anterior este se subdivide en tres partes que son:

PROM. Programmable Read-Only Memory (Memoria Programable de

Solo Lectura), Dispositivo programado por el usuario y no borrable

o reprogramable.

EPROM. Erasable Programmable Read-Only Memory (Memoria

Programable y Borrable de Solo Lectura); este tipo de Memorias se

borran Mediante Luz ultravioleta; con la ventaja de que puede ser

programada por el usuario.

EEPROM. Electrically Erasable Programmable Read-Only Memory

(Memoria Programable y Borrable Eléctricamente de Solo Lectura); al

igual que la anterior está puede ser programada por el usuario.

Y pueden ser utilizados como PLD’s, debido a que las entradas de

direccionamiento pueden ser manejadas como variables de entrada en las

ecuaciones y las salidas de la memoria, como salidas de las mismas.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

El número de productos es igual a:

2n x S = C

Donde:

n es igual al número de variables de Entrada.

S es la cantidad de funciones de Salida.

C es la capacidad de la memoria en bits.

Desgraciadamente estas se vuelven imprácticas cuando se contemplan

grandes números de entradas, debido a que por cada variable que se anexe, el

arreglo de fusibles se duplica. Muchas aplicaciones requerirán de un número

mayor de entradas, pero no tendrán la flexibilidad que puede ofrecer una

PROM como decodificador completo. Desde el punto de vista del fabricante

usar una PROM como PLD representa un uso ineficiente del silicio y por lo

tanto se incrementa su costo.

En este tipo de PLD’s el plano AND es fijo y el OR es programable.

PLA. Programmable Logic Array (Arreglo Lógico Programable), este tipo de

dispositivos resuelve el problema de las PROM; debido a que, tiene tanto el

plano AND como el OR programables. De forma que solo se seleccionan los

productos de términos necesarios para las diferentes aplicaciones; esto hace

mucho más eficiente la matriz programable y al dispositivo más versátil. A este

tipo de dispositivos, también se les conoce como Field Programmable Logic

Array (Arreglos Lógicos Programables de Campo). Los FPLA o PLA aceptan

más variables de entrada con mucho menor producto de términos que 2n.

Estos PLD’s incluyen además la capacidad de programar la polaridad de salida,

lo que permite trabajar con max-términos si se requieren; esto se logra a través

de una OR-Exclusiva.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

Un FPLA es el TIFPLA840 de Texas Instruments, el cual es especificado como

un FPLA de 14 x 32 x 6. Es decir que, tiene 14 variables como entradas, 32

compuertas AND para generar los productos lógicos de las variables, y 6

compuertas OR que pueden formar cualquier combinación de las salidas de las

compuertas AND.

No obstante, los fusibles adicionales (debido a que hay dos planos

programables), agregan un retardo mayor que los de un solo plano

programable y una circuitería más compleja y al mismo tiempo la programación

se vuelve más elaborada. Debido a la tecnología que utilizan también aumenta

su costo.

PAL. Programmable Array Logic (Lógica en un Arreglo Programable), la

arquitectura de éste PLD está compuesta por un Plano AND programable y el

Plano OR fijo. Este dispositivo es el intermedio entre una PROM y un PLA;

debido a que, por cada entrada que se agregue no será necesario duplicar la

cantidad de fusibles y el tener un plano fijo conduce a un menor retardo en la

circuitería interna. También incluye la capacidad de programar la polaridad de

salida. Este PLD puede incluir una serie de componentes a la salida del plano

OR, como pueden ser: Inversores y Flip-Flops, que permitirán hacer del

dispositivo, un PLD versátil.

Existen dos tipos de PAL’s, uno de los cuales puede ser programado

solamente una vez, por ejemplo: El PAL16R8 el cual es un dispositivo de 16

posibles entradas y con 8 salidas; todas con Flip-Flops. El otro PAL mejor

conocido como GAL de Generic Array Logic (Lógica en Arreglo Genérico),

combina las características de un PAL; pero además, agrega tecnología

especial para ser borrado y programado eléctricamente.

Todos los PLD están formados por matrices programables. Esencialmente, una

matriz programable es una red de conductores distribuidos en filas y columnas

con un fusible en cada punto de intersección. Las matrices pueden ser fijas o

programables.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

Matriz OR. Está formada por una serie de puertas OR conectadas a una matriz

programable con fusibles en cada punto de intersección de una columna y una

fila. La matriz se programa fundiendo los fusibles para eliminar las variables

seleccionadas de las funciones de salida para un caso específico. Para cada

una de las entradas de una puerta OR sólo queda intacto un fusible que

conecta la variable deseada en la entrada de la puerta. Una vez que el fusible

esta fundido, no se puede volver a conectar.

Matriz AND. Este tipo de matriz está formado por puertas AND conectadas a

una matriz programable con fusibles en cada punto de intersección. Al igual

que la matriz OR la matriz AND se programa fundiendo los fusibles para

eliminar las variables de la función salida. Para cada entrada de una puerta

AND sólo queda intacto un fusible que conecta la variable deseada a la entrada

de la puerta. Como para la matriz OR la matriz AND con fusibles se puede

programar una única vez.

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

DIFERENCIA ENTRE LAS ARQUITECTURAS DE LOS PLD’s

SIMBOLOGIA ADOPTADA EN LOS PLD’s

Los fabricantes han sustituido el símbolo del inversor y del no-inversor en uno

solo; pero, con dos salidas

complementadas. Han simplificado

las líneas de entrada a una

compuerta AND u OR, por medio

de una sola línea. Las conexiones

entre compuertas se representan

mediante una “X”o un punto. Las

“X” se encuentran en el Plano

programable y describen una

conexión fusible intacta. En el Plano

fijo, un punto representa una conexión fija y que por supuesto, ya no puede

cambiarse. La ausencia de estos dos símbolos en un cruce de líneas significa

TAREA

SANTANA PEÑA VICTOR HUGO

04/02/2015

que no existe conexión entre ellas.

Bibliografía

Gil, Luis, Introducción a la electrónica digital, Ed. Univ. Politéc.

Valencia, 1999, 257 pág.

Fuentes

Dispositivos lógicos programables (PLD),

Https: //ecadigitaliiequipo7.wordpress.com/2010/03/08/dispositivos-

logicos-programables-pld/, (página consultada el día 04.02.2015 a

las 19:00 pm).

UNIVERSIDAD DE GUADALAJARA, CENTRO UNIVERSITARIO DE

CIENCIAS EXACTAS E INGENIERIAS, PLD´S, “DISPOSITIVOS

LOGICOS PROGRAMABLES”,

http://proton.ucting.udg.mx/tutorial/MAN_PLD/MAN_PLD.pdf,

(página consultada el día 04.02.2015 a las 20:14)